Diss. ETH No. 16201

# On Instruction-Set Generation for Specialized Processors

A dissertation submitted to the SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH

> for the degree of Doctor of Technical Sciences

> > presented by GERO DITTMANN Dipl.-Ing. born March 15, 1974 citizen of Germany

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. Paolo Ienne, co-examiner Prof. Dr. Andreas Herkersdorf, co-examiner

## Acknowledgments

First of all, I would like to thank my advisor, Lothar Thiele, for giving me the chance to pursue a Ph.D. at ETH Zurich while working at IBM, and for encouraging me to delve into this fascinating field of synthesis methods for embedded systems. The course on hard-ware/software co-design by Marco Platzner provided my with an invaluable basis for my research. At an advanced stage, my co-advisor, Paolo Ienne, was an important influence, shaping my work by asking all the right questions.

The IBM Zurich Research Laboratory (ZRL) is a tremendously challenging and inspiring work environment. I want to thank all the people who make this lab such a special place. I am most indebted to Andreas Herkersdorf and Ton Engbersen who were my managers and mentors at ZRL. They have been an enormous source of inspiration and motivation. I very much appreciate the support by the lab's technical and administrative staff. I am particularly grateful to Charlotte Bolliger for proofreading my papers and teaching me a lot about the subtleties of the English language.

Thanks to the technical community for receiving me so openly. Special thanks go to Gerhard Fohler and Peter Puschner for taking the time to discuss my ideas on real-time scheduling in great length. I also want to thank my co-authors on papers and patents, especially Paul Hurley for helping me cope with integer linear programs.

On a less technical note, I express my utmost gratitude to my office mates, Sonja Buchegger, Mark Verhappen, Silvio Dragone, as well as the plants Alice and Bob, and to my unfailing lunchtime companions for sedulously discussing—and solving—all major questions in politics, art, literature, philosophy, and bicycle repair. I thank all my friends, inside and outside ZRL, for being there with encouragement or constructive doubt—whichever was appropriate.

Finally, I am infinitely grateful to my parents and sister without whose moral support this book would never have come into existence.

## Abstract

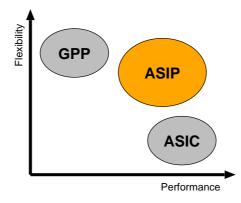

Owing to the ever-decreasing feature size of today's semiconductor processes, the cost of a mask set has already crossed the one-million-dollar line. Given this investment, a design must be applicable for multiple purposes. This flexibility is commonly provided by programmable elements. A gradual trade-off between the flexibility of general-purpose processor cores and the performance of hard-wired logic can be achieved with *application-specific instruction-set processors* (ASIPs).

Many automated ASIP design methods found in the literature today employ a library of patterns that represent potential specialized instructions. As the libraries tend to grow large their access times become a critical factor. However, no attempts have yet been made to speed up these searches in the pattern libraries. Furthermore, there are no methods available to recognize and exploit structural similarities between patterns.

Another deficiency in today's ASIP design methodologies is their exclusive focus on the data-dominated domain characterized by computation-intensive applications such as digital signal processing. This focus entails a lack of methods for control-dominated domains such as network processing. These domains are characterized by branch-intensive applications with fine-grained timing constraints imposed by frequent interactions with the ASIP environment. The major challenge here is not to speed up the over-all runtime of the applications, but to meet the many timing constraints. This challenge can be addressed by introducing special instructions that speed up the timing-critical paths.

In this thesis we propose a hierarchical organization for pattern libraries that removes the dependency of search times on the library size. In this way, much larger libraries can be handled which removes the need for heuristics to prune patterns from the library. Exact methods become possible. In our experiments we found that searches in our structure are orders of magnitude faster than in a linked-list library. Furthermore, we introduce a method that employs identity operands to find synergies between similar patterns. These similarities can be exploited to achieve leaner instruction sets and for data-path sharing.

On top of these library structures, we propose the first integrated ASIP design methodology for the control-dominated domain. We introduce novel methods to specify fine-grained timing constraints in ANSI C, to include them in an intermediate representation that facilitates compiler optimizations, and to derive an instruction set that enables the ASIP to meet the timing constraints. We present a case study that demonstrates the feasibility of our methods and the quality of the results.

# Zusammenfassung

Die stetig schrumpfenden Strukturgrößen moderner Halbleiterprozesse haben dazu geführt, dass die Kosten für einen Belichtungssatz bereits eine Million Dollar überschreiten. Damit sich diese Investition auszahlt, muss ein Design vielfältig einsetzbar sein. Die erforderliche Flexibilität wird üblicherweise mit Hilfe von programmierbaren Bausteinen erreicht. Eine feinstufige Abwägung zwischen der Flexibilität von General-Purpose-Prozessoren auf der einen Seite und der Leistungsfähigkeit von fest verdrahteten Schaltungen auf der anderen Seite wird ermöglicht von *application-specific instruction-set processors* (ASIPs).

Viele der veröffentlichten automatisierten ASIP-Design-Methoden bedienen sich einer Bibliothek von Mustern, die Kandidaten für Spezialbefehle darstellen. Da diese Bibliotheken sehr groß werden können, spielt ihre Zugriffszeit eine entscheidende Rolle. Dennoch wurde bisher nicht untersucht, wie die Suche in einer Musterbibliothek beschleunigt werden kann. Darüberhinaus sind keine Methoden bekannt, um Gemeinsamkeiten in der Struktur zweier Muster zu erkennen und auszunutzen.

Eine weitere Einschränkung heutiger ASIP-Design-Methodologien ist ihre ausschließliche Beschäftigung mit der Klasse der rechenintensiven, datendominierten Anwendungen wie digitaler Signalverarbeitung. Es fehlt daher an Methoden für kontrolldominierte Anwendungsklassen wie der Verarbeitung von Netzwerkprotokollen. Diese Klassen sind gekennzeichnet durch Anwendungen mit vielen Verzweigungen und detaillierten Zeitanforderungen, die von häufigen Interaktionen mit der Umgebung herrühren. Unter diesen Bedingungen besteht die Herausforderung nicht darin, die Gesamtlaufzeit der Anwendungen zu verringern, sondern sämtliche Zeitanforderungen zu erfüllen. Dies kann erreicht werden mit Hilfe von Spezialbefehlen, die die Ausführung von zeitkritischen Pfaden beschleunigen.

Diese Dissertation führt eine hierarchische Organisation für Musterbibliotheken ein, die die Abhängigkeit der Suchgeschwindigkeit von der Größe der Bibliothek aufhebt. Diese Eigenschaft macht wesentlich größere Bibliotheken beherrschbar, wodurch Heuristiken zum Verwerfen von Mustern vermieden werden können. Exakte Methoden werden möglich. Experimente zeigen, dass das Suchen in dieser Struktur um Größenordnungen schneller ist als in einer Bibliothek, die als verkettete Liste aufgebaut ist. Weiterhin wird eine Methode vorgestellt, die mit Hilfe von Identitätsoperanden Synergien zwischen sich ähnelnden Mustern findet. Die Ähnlichkeiten bieten die Möglichkeit, schlankere Befehlssätze zu erreichen und Datenpfade mehrfach zu nutzen.

Aufbauend auf diesen Bibliotheksstrukturen wird die erste integrierte ASIP-Entwicklungsmethodologie für kontrolldominierte Anwendungsklassen vorgestellt. Es werden neuartige Methoden entwickelt, um detaillierte Zeitanforderungen in ANSI-C zu spezifizieren, sie in eine Graphendarstellung für Compileroptimierungen einzubinden und daraus schließlich einen Befehlssatz abzuleiten, der es dem ASIP ermöglicht, die Zeitanforderungen einzuhalten. Abschließend wird anhand einer Fallstudie die Machbarkeit der Methoden und die Qualität der Ergebnisse demonstriert.

# Contents

| 1 | Intro              | oductio                                                                         | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                          |

|---|--------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | 1.1                | The Ca                                                                          | ase for Specialized Processor Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                          |

|   |                    | 1.1.1                                                                           | Systems on a Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                          |

|   |                    | 1.1.2                                                                           | Networking SoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                                          |

|   | 1.2                | Currer                                                                          | at ASIP Design Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                          |

|   |                    | 1.2.1                                                                           | A Generic Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                          |

|   |                    | 1.2.2                                                                           | Instruction-Set Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                                                                                                          |

|   | 1.3                | A New                                                                           | Methodology for Control-Dominated ASIPs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                          |

|   |                    | 1.3.1                                                                           | Control-Dominated vs. Data-Dominated ASIPs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                          |

|   |                    | 1.3.2                                                                           | The Design Methodology and its Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                          |

|   |                    | 1.3.3                                                                           | Data-Push Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                         |

|   |                    | 1.3.4                                                                           | Assumptions on Processor Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                                         |

|   | 1.4                | This T                                                                          | hesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                         |

|   |                    |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

| 2 | Patt               | ern Lik                                                                         | prary for Fast Searches and Synergies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                         |

| 2 | <b>Patt</b><br>2.1 |                                                                                 | orary for Fast Searches and Synergies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |

| 2 |                    |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

| 2 |                    | Relate                                                                          | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                         |

| 2 |                    | Relate                                                                          | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15<br>15                                                                                                   |

| 2 |                    | Relate<br>2.1.1<br>2.1.2<br>2.1.3                                               | d Work          Pattern Libraries          Searching and Pattern Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15<br>15<br>16<br>16                                                                                       |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3                                               | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15<br>15<br>16<br>16<br>17                                                                                 |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3<br>Hierar                                     | d Work       Pattern Libraries         Pattern Libraries       Searching and Pattern Matching         Identity Operands and Datapath Sharing       Searching         chical Library Organization       The Pattern Search Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15<br>15<br>16<br>16<br>17                                                                                 |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3<br>Hierar<br>2.2.1                            | d Work       Pattern Libraries         Pattern Libraries       Searching and Pattern Matching         Identity Operands and Datapath Sharing       Searching         chical Library Organization       Searching         The Pattern Search Graph       Searching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15<br>15<br>16<br>16<br>17<br>17                                                                           |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3<br>Hierar<br>2.2.1<br>2.2.2                   | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15<br>15<br>16<br>16<br>17<br>17<br>18                                                                     |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3<br>Hierar<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | d Work       Pattern Libraries         Pattern Libraries       Searching and Pattern Matching         Identity Operands and Datapath Sharing       Image: Comparison of the | 15<br>15<br>16<br>16<br>17<br>17<br>18<br>21                                                               |

| 2 | 2.1                | Relate<br>2.1.1<br>2.1.2<br>2.1.3<br>Hierar<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | d Work       Pattern Libraries         Pattern Libraries       Searching and Pattern Matching         Identity Operands and Datapath Sharing       Image: Comparison of the pattern Search Graph         The Pattern Search Graph       Image: Comparison of the pattern in a PSG         Inserting Patterns into a PSG       Image: Comparison of the patterns into a PSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ol> <li>15</li> <li>16</li> <li>16</li> <li>17</li> <li>17</li> <li>18</li> <li>21</li> <li>22</li> </ol> |

|   |      | 2.3.3    | Inserting Patterns into an IOG              | 26 |

|---|------|----------|---------------------------------------------|----|

|   |      | 2.3.4    | IOGs of DAG Patterns                        | 31 |

|   | 2.4  | Librar   | y Size                                      | 32 |

|   |      | 2.4.1    | Patterns in a PSG                           | 32 |

|   |      | 2.4.2    | Analytical Bounds for IOGs                  | 33 |

|   |      | 2.4.3    | Comparing IOGs with Unordered Libraries     | 34 |

|   | 2.5  | Summ     | ary of Pattern-Library Organization         | 35 |

| 3 | Con  | npiler N | Methods for Fine-Grained Timing Constraints | 37 |

| • | 3.1  | -        | d Work                                      |    |

|   | 5.1  | 3.1.1    | Specifying Timing Constraints               |    |

|   |      | 3.1.2    | Intermediate Representations                |    |

|   | 3.2  |          | ting Timing Constraints into ANSI C         |    |

|   | 5.2  | 3.2.1    | Fixed Timing Constraints between Operations |    |

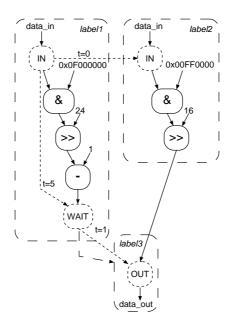

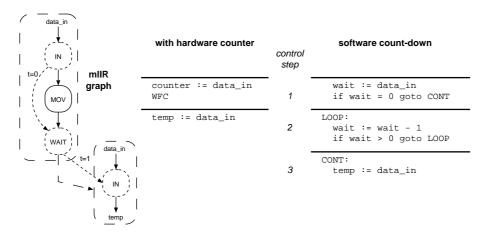

|   |      | 3.2.2    | Data-Dependent Wait                         |    |

|   |      | 3.2.2    | Code Example                                |    |

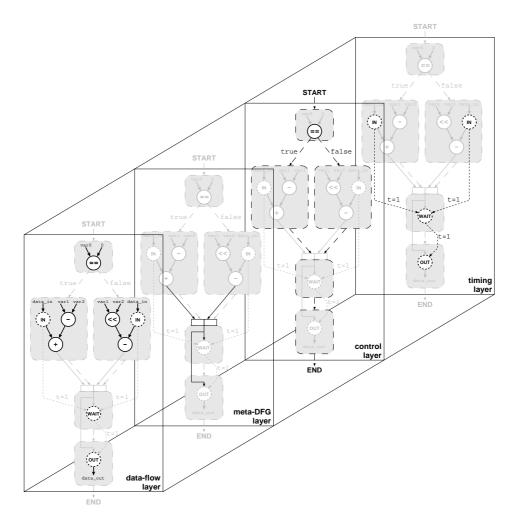

|   | 3.3  |          | Layer Intermediate Representation           |    |

|   | 5.5  | 3.3.1    | Data-Flow Layer                             |    |

|   |      | 3.3.2    | Control Layer                               |    |

|   |      | 3.3.3    | Meta-DFG Layer                              | -  |

|   |      | 3.3.4    | Timing Layer                                |    |

|   |      | 3.3.5    | Putting it all Together                     | 46 |

|   | 3.4  |          | g Layer Transformations                     |    |

|   | 5.4  | 3.4.1    | Parsing Timing Annotations in C             |    |

|   |      | 3.4.2    | Implementing a Data-Dependent Wait          | 49 |

|   | 3.5  |          | Postponing                                  |    |

|   | 5.5  | 3.5.1    | The Algorithm                               |    |

|   |      |          | C C                                         |    |

|   | 3.6  | 3.5.2    | Applicability and Relevance                 |    |

|   | 5.0  | Summ     |                                             | 55 |

| 4 | Inst | ruction  | -Set Generation for Precise Timing          | 57 |

|   | 4.1  | Relate   | d Work                                      | 58 |

|   |                   | 4.1.1                                                                                    | Operation Scheduling                  | 58                                                                                                                                          |

|---|-------------------|------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 4.1.2                                                                                    | Scheduling with Timing Constraints    | 59                                                                                                                                          |

|   | 4.2               | Timing                                                                                   | g-Forced Patterns                     | 59                                                                                                                                          |

|   |                   | 4.2.1                                                                                    | Problem Statement                     | 59                                                                                                                                          |

|   |                   | 4.2.2                                                                                    | ILP Formulation                       | 60                                                                                                                                          |

|   |                   | 4.2.3                                                                                    | Heuristic                             | 62                                                                                                                                          |

|   | 4.3               | Constr                                                                                   | aining Parallel Instruction Issues    | 66                                                                                                                                          |

|   |                   | 4.3.1                                                                                    | Problem Statement                     | 66                                                                                                                                          |

|   |                   | 4.3.2                                                                                    | ILP Formulation                       | 66                                                                                                                                          |

|   |                   | 4.3.3                                                                                    | Heuristic                             | 68                                                                                                                                          |

|   |                   | 4.3.4                                                                                    | Using IOGs to Eliminate Instructions  | 70                                                                                                                                          |

|   | 4.4               | Handli                                                                                   | ng Control Constructs                 | 71                                                                                                                                          |

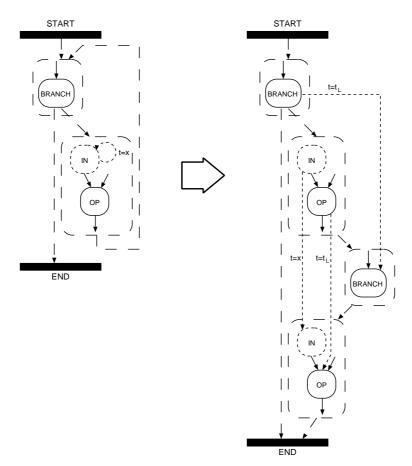

|   |                   | 4.4.1                                                                                    | Loop Ripping                          | 71                                                                                                                                          |

|   |                   | 4.4.2                                                                                    | Wait-Node Scheduling                  | 72                                                                                                                                          |

|   |                   | 4.4.3                                                                                    | Branches, Nop, WFC                    | 73                                                                                                                                          |

|   | 4.5               | Summ                                                                                     | ary of Instruction-Set Generation     | 73                                                                                                                                          |

|   |                   |                                                                                          |                                       |                                                                                                                                             |

| 5 | Ехр               | erimen                                                                                   | atal Results                          | 75                                                                                                                                          |

| 5 | <b>Exp</b><br>5.1 |                                                                                          |                                       | <b>75</b><br>75                                                                                                                             |

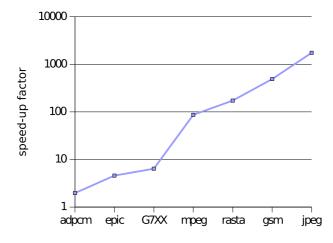

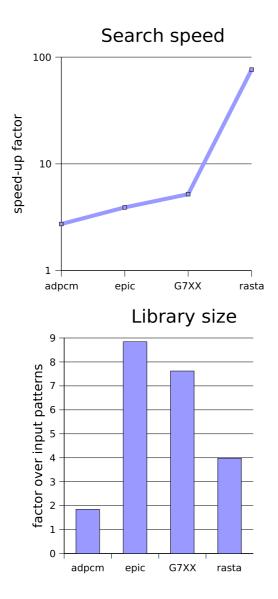

| 5 | -                 |                                                                                          | n-Library Performance: Speed and Size |                                                                                                                                             |

| 5 | -                 | Patterr                                                                                  | n-Library Performance: Speed and Size | 75                                                                                                                                          |

| 5 | -                 | Patterr<br>5.1.1                                                                         | n-Library Performance: Speed and Size | 75<br>75                                                                                                                                    |

| 5 | -                 | Patterr<br>5.1.1<br>5.1.2<br>5.1.3                                                       | h-Library Performance: Speed and Size | 75<br>75<br>75                                                                                                                              |

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3                                                       | h-Library Performance: Speed and Size | 75<br>75<br>75<br>76                                                                                                                        |

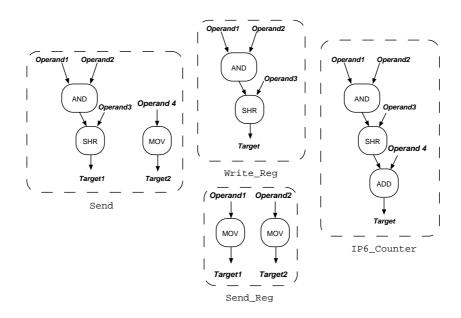

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp                                              | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> </ul>                                                                      |

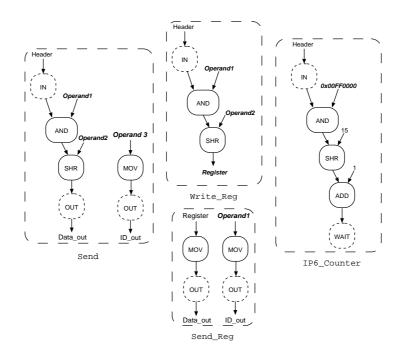

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp<br>5.2.1                                     | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> </ul>                                                          |

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp<br>5.2.1<br>5.2.2                            | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>80</li> </ul>                                              |

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp<br>5.2.1<br>5.2.2<br>5.2.3                   | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>80</li> <li>81</li> </ul>                                  |

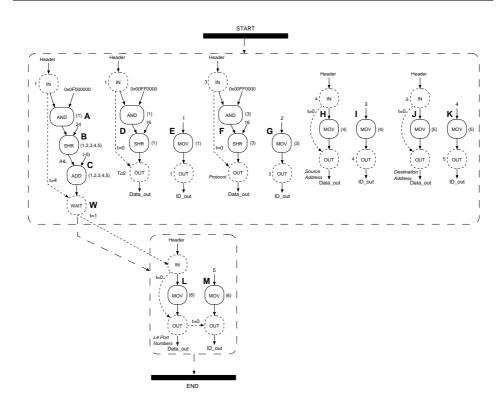

| 5 | 5.1               | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>80</li> <li>81</li> <li>86</li> <li>86</li> </ul>          |

| 5 | 5.1<br>5.2<br>5.3 | Patterr<br>5.1.1<br>5.1.2<br>5.1.3<br>Examp<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | a-Library Performance: Speed and Size | <ul> <li>75</li> <li>75</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>80</li> <li>81</li> <li>86</li> <li>87</li> <li></li></ul> |

|              | 6.1.1  | Efficient Pattern Libraries                    | 91  |

|--------------|--------|------------------------------------------------|-----|

|              | 6.1.2  | Design Methodology for Control-Dominated ASIPs | 92  |

| 6.2          | Future | Work                                           | 93  |

|              | 6.2.1  | Pattern Libraries                              | 93  |

|              | 6.2.2  | ASIP Design Methodology                        | 94  |

| Bibliog      | Iraphy |                                                | 95  |

| Biography    |        |                                                | 103 |

| Publications |        |                                                | 105 |

# **List of Figures**

| 1.1  | Performance/flexibility trade-off.                    | 2  |

|------|-------------------------------------------------------|----|

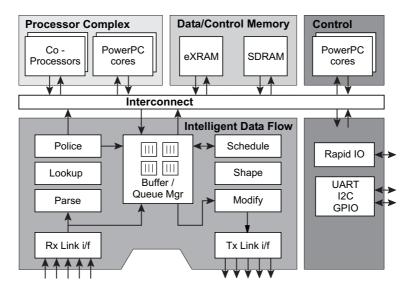

| 1.2  | NP with ASIP-based fast path                          | 3  |

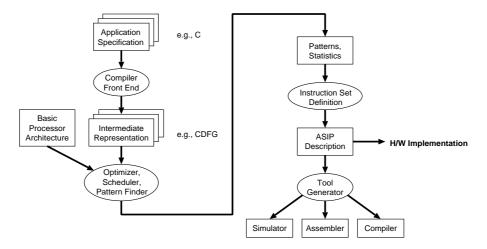

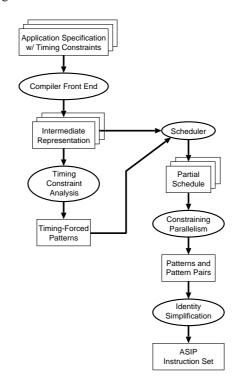

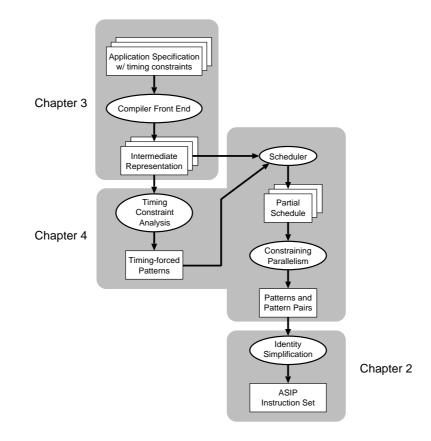

| 1.3  | A generic ASIP design methodology                     | 4  |

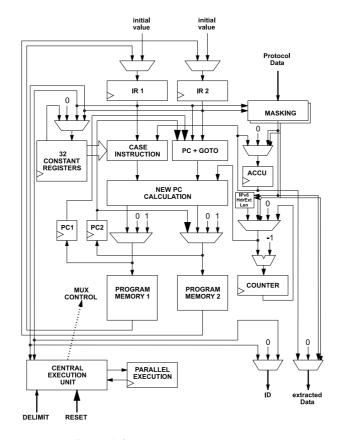

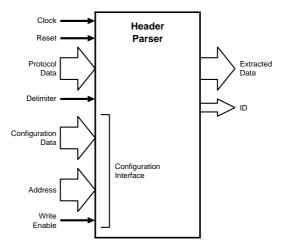

| 1.4  | A control-dominated ASIP                              | 8  |

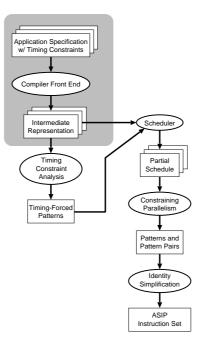

| 1.5  | Design methodology for control-dominated ASIPs        | 9  |

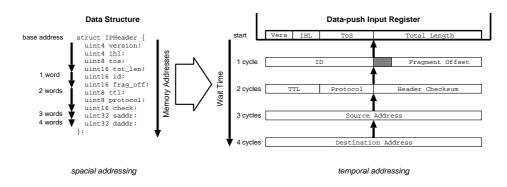

| 1.6  | From spacial to temporal addressing.                  | 11 |

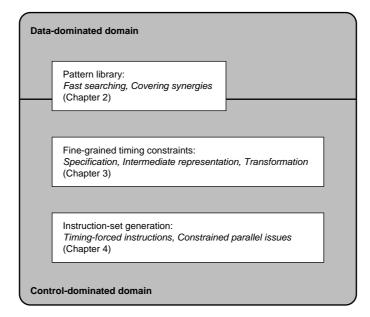

| 1.7  | Overview of the contributions.                        | 12 |

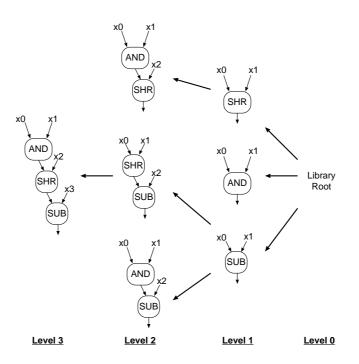

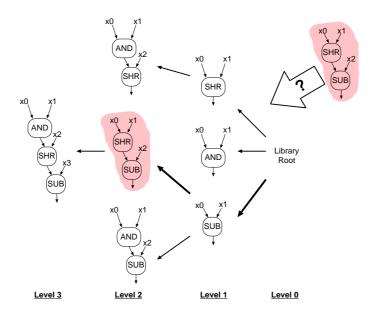

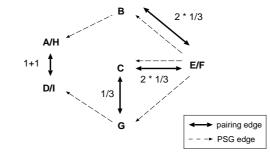

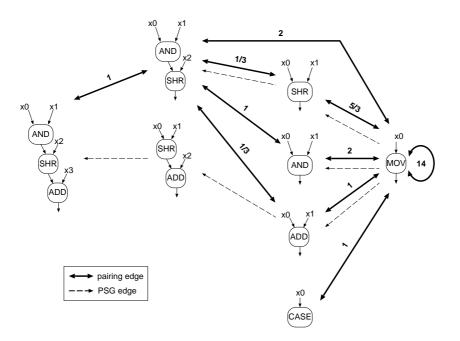

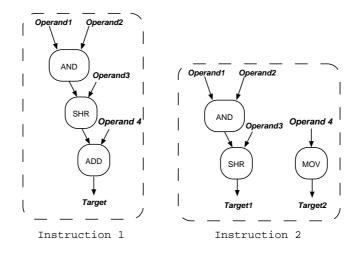

| 2.1  | Example of a pattern search graph                     | 18 |

| 2.2  | Pseudo code: Pattern search in a PSG.                 | 19 |

| 2.3  | Tree-pattern search in a PSG.                         | 19 |

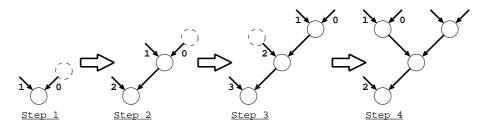

| 2.4  | Operand numbering.                                    | 20 |

| 2.5  | Pseudo code: Inserting a tree pattern into a PSG      | 21 |

| 2.6  | Pseudo code: DAG pattern search in a PSG              | 22 |

| 2.7  | Pseudo code: Inserting a DAG pattern into a PSG       | 23 |

| 2.8  | IOG of a pattern.                                     | 25 |

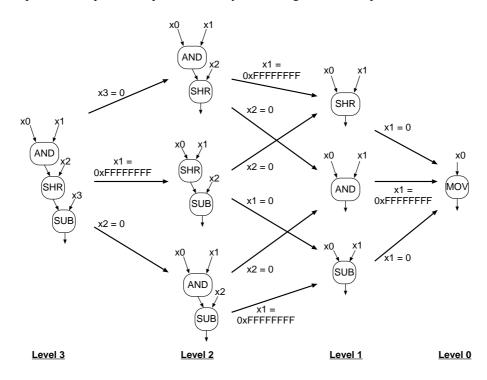

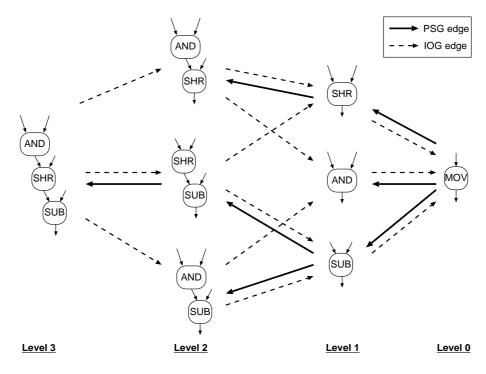

| 2.9  | Combined PSG/IOG.                                     | 26 |

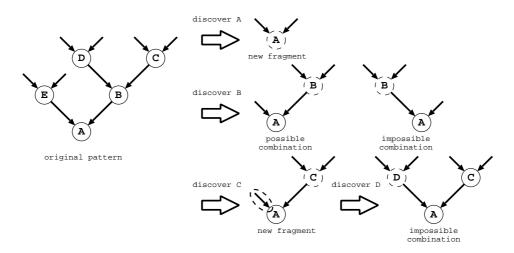

| 2.10 | Fragment combination.                                 | 27 |

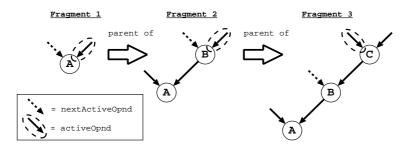

| 2.11 | Pseudo code: Insert a pattern into an IOG             | 29 |

| 2.12 | Pseudo code: Combine fragments with next pattern node | 30 |

| 2.13 | Pseudo code: Compute next active operand.             | 31 |

| 2.14 | Family tree of fragments.                             | 31 |

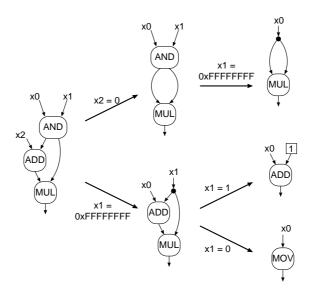

| 2.15 | IOG of a DAG pattern.                                 | 32 |

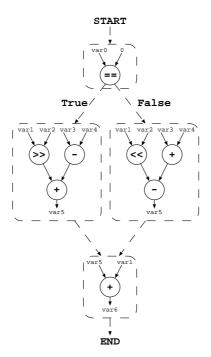

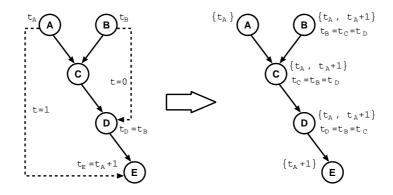

| 3.1  | A simple CDFG.                                        | 39 |

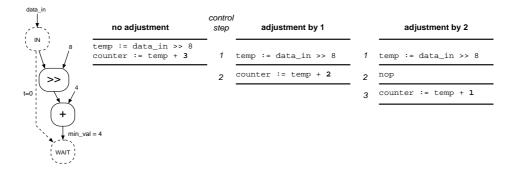

| 3.2  | Example of C code with timing constraints.            | 44 |

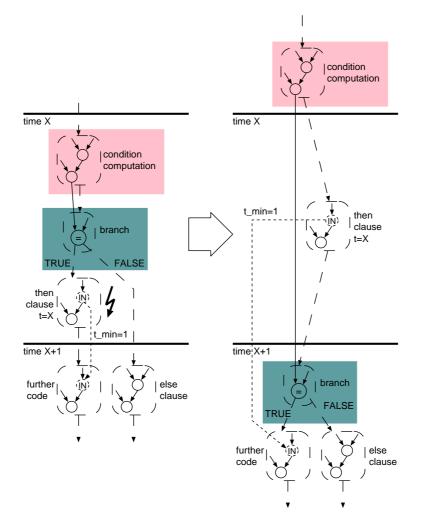

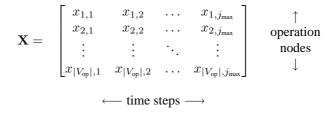

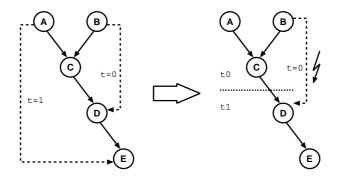

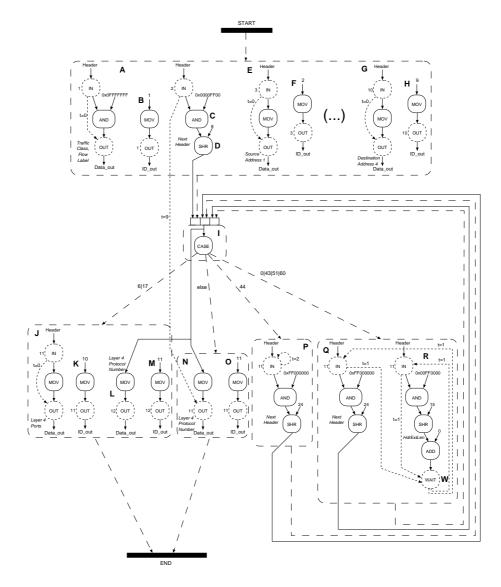

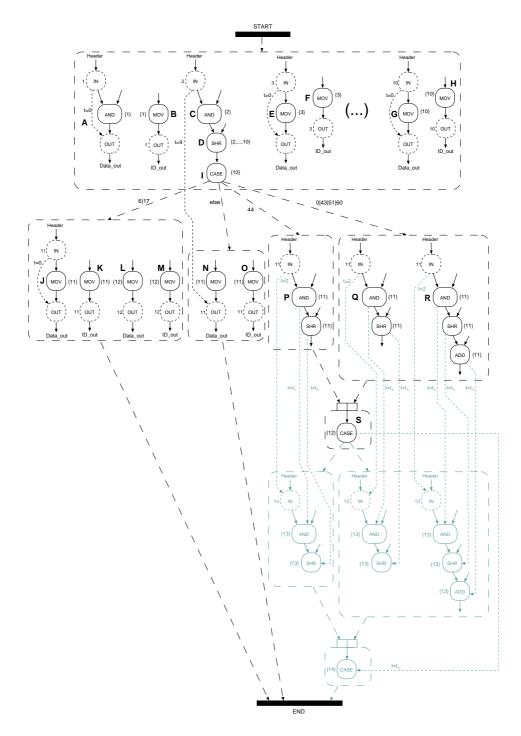

| 3.3  | Example of multi-layer IR graph                       | 47 |

| 3.4        | Parser productions for the basic timing constructs                       | 48 |