### Scalable Flow Control for Interconnection Networks

A dissertation submitted to the SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH

for the degree of Doctor of Technical Sciences

presented by FERDINAND GRAMSAMER

Dipl.-Ing., Universität Stuttgart, Germany born 13.03.1969 citizen of Germany

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. José Duato, co-examiner to my family

## Acknowledgements

My achievements are deeply rooted on the input, comments, feedback, and patience from the excellent people that I was lucky to work with during the last 5 years.

First of all, I'd like to thank Professor Thiele for his willingness to coach me, his promptness, the eye-opening discussions and his valuable comments on the progress of my research. In the same light, I thank Professor Duato for his excellent observations, ideas, and creativity that inspired my dissertation. I am grateful to his stimulating feedback.

I am happy to have had the chance to perform my studies in such a renowned place as the IBM Research Laboratory in Rüschlikon. This once in a life-time opportunity was enriched by an outstanding work-environment and most proficient colleagues. In particular, I'd like to express my sincere appreciation to Ronald Luijten for his supervision, help, and his capability in filtering out the essence of things and to Mitch Gusat for his superb advice, vision and experience on interconnection networks that he transmitted to me.

I am indebted to all the past and current colleagues of the PRIZMA team, in particular to Cyriel Minkenberg for his helpful feedback, and sharing his profound knowledge on switch architectures and modelling with me. Thanks to Francois Abel, Wolfgang Denzel, Mark Verhappen, Markus Sing, and Silvio Dragone for friendship, and countless fruitful work- and non-work related discussions. Also thanks to Ilias Iliadis for his useful comments that have helped improve Chapter 4.

Thanks to Peter Klett and Thomas Kretschmer from the Intellectual Property Department for the fun and the good cooperation, to Charlotte Bolliger for proofreading and correcting all my publications.

Last but not least I am thankful to my wife for her patience, support and love that she gave my throughout.

## Abstract

Performance of most digital systems is constrained by their communication and interconnection, not by their processing power. The technological progress makes memories and logic smaller, faster, and less expensive, whereas the corresponding necessary pin and wiring density scales at a slower rate. The clock rate of modern processors outpaces the frequency of communication between components. These factors combined make interconnection the key factor in the design of future digital systems.

Due to the extraordinary growth of the Internet, communication components such as routers and switches grow in size as they connect more computing resources at higher speeds. Unlike previous generations of networking components, these devices are no longer feasible on a single chip, board, or rack. It requires a new kind of system-level communication among multiple racks. Such large communication components are akin to multiprocessor systems with similar requirements:

- loss-less communication based on fix-sized packets

- efficient bandwidth utilization

- scalable in terms of attachable networking nodes

Hop-by-hop closed-loop flow control with selective backpressure is hereby often used to meet above requirements. The following issues have not yet been dealt with:

- Although a variety of such flow control schemes exist, no scheme triggers the return of flow control information based on the transmission- and reception-sided buffer state.

- The system-level flow control has been looked at for negligible round-trip time delays, whereas the impact of long links on resource requirements and performance has not been analyzed.

- The control overhead has not been minimized.

The above issues are addressed in this thesis and the major contributions in the research area of packet switches and interconnection networks are:

- The scheduling of flow control has been introduced. It allows to minimize the overhead necessary in feed-back control systems. The resulting scheme is distributed, autonomous, scalable and achieves load-balancing to optimize the utilization of resources.

- Various strategies are explored for this flow control scheme by exhaustive simulation for a wide set of system and traffic parameters. The exploration focuses on the resolution of output contention.

- The trade-off between implementational complexity and flow control overhead for buffered packet switches has been quantified for all combinations of relevant schemes.

- A multiplicity of highly loaded parallel flows through a buffered switch result in high aggregate throughput. This is a classical means to evaluate the quality of switches. Depending on the output queue service, throughput and delay for single flows may depend on the existence of other flows. The power metric is introduced as quality criteria to give a more distinguished view.

## Kurzfassung

Die Leistungsfähigkeit der meisten digitalen Systeme wird bestimmt durch ihre Kommunikation und Verknüpfung und nicht etwa durch ihre Rechenleistung. Der technologische Fortschritt bewirkt, dass Speicherelemente und Logik kleiner, schneller und billiger werden, während die dazu nötige Pin- und Verkablungsdichte langsamer zunimmt. Die Kommunikationrate zwischen Komponenten kann nicht mehr Schritt halten mit der Entwicklung der Taktraten moderner Prozessoren. All diese Faktoren zeigen, dass Verbindung der Schlüsselfaktor im Entwurf zukünftiger digitaler Systeme ist.

Wegen des ausserordentlichen Wachstums des Internets, wachsen Kommunikationskomponenten, wie Verbindungsknoten und Vermittlungsstellen, in ihrer Grösse, da sie immer mehr Rechenpunkte mit immer höherer Geschwindigkeit verbinden. Anders als vorhergehende Generationen von Netzwerkkomponenten, sind sie nun nicht mehr auf einem Chip, Karte, oder gar einem Gestell unterzubringen. Es wird eine neuartige Kommunikation auf Systemebene zwischen den einzelnen Gestellen verlangt, die nun für das Gesamtsystem notwendig sind. Solche grossen Kommunikationskomponenten ähneln Multiprozessorsystemen, die auch ähnliche Anforderungen haben:

- verlustfreie Kommunikation basierend auf Packeten gleicher Länge

- effiziente Bandbreiteausnutzung

- skalierbar für zusätzliche Netzwerkknoten

Geschlossene Flusskontrolle zwischen benachbarten Knoten mit selektiver Rückkopplung wird hierbei häufig verwendet, um oben genannte Anforderungen zu erfüllen. Die folgenden Themen sind is jetzt noch nicht behandelt worden:

- Obwohl eine Vielzahl von Flusskontrollansätzen existiert, retourniert keiner sein Informationen basierend auf dem Zustand sowohl der Übertragungs- als auch der Empfangsseite.

- Die Flusskontrolle auf Systemebene wurde bis anhin für vernachlässigbare Umlaufzeiten analysiert, während der Einfluss von grossen Umlaufzeiten auf Resourcen und Leistungsfähigkeit nicht angeschaut wurde.

- Der Kontrollüberhang wurde nicht minimiert.

Die oben genannten Themen werden in dieser Arbeit berücksichtigt, so dass sich die Hauptbeiträge im Forschungsgebiet der Packetvermittlungsstellen und Verbindungsnetzwerke folgendermassen zusammenfassen lassen:

• Eine Regelung zum Abruf der Flusskontrolle wurde eingeführt. Sie erlaubt es den Überhang, der notwendig in Rückkopplungssystemen ist, zu minimieren. Der daraus resultierende Ansatz ist verteilt, autonom, skalierbar und gleicht die vorhandenen Lasten so aus, dass der Gebrauch der Resourcen optimiert werden kann.

- Verschiedne Strategien werden hierfür mittels Simulation unter Berücksichtigung eines weiten Spektrums von System- und Verkehrsparametern ergründet. Das Interesse liegt hierbei bei der Auflösung von ausgangsseitigem Stau.

- Der Kompromiss zwischen Implementierungskomplexität und Flusskontrollüberhang für gepufferte Paketvermittlungsstellen wurde quantifiziert für alle Kombinationen relevanter Methoden.

- Eine Vielfalt von stark belasteten parallelen Flüssen durch die gepufferte Vermittlungsstelle resultiert in hohen Gesamtdurchsatz. Dies is der klassische Ansatz, um die Qualität von Vermittlungsstellen zu bestimmen. Abhängig davon wie die Ausgangswarteschlangen bedient werden, hängt der Durchsatz und die Durchlaufzeit von der Existenz anderer Flüsse ab. Das "Powermass" wird als Qualitätskriterium eingeführt, um sich ein differenzierteres Bild machen zu können.

# Contents

| At | Abbreviations xxi |          |                                                                 |        |

|----|-------------------|----------|-----------------------------------------------------------------|--------|

| 1  | Intr              | oductior | n                                                               | 1      |

| 1  | 1.1               |          | nship to a General Problem                                      | 1      |

|    | 1.1               |          | Quo in Switching                                                | 1      |

|    | 1.2               |          | Problems                                                        | 3      |

|    | 1.3               |          | Aakes the Problems Difficult?                                   | 3      |

|    | 1.4               |          | butions of this Thesis                                          | 4      |

|    | 1.5               |          |                                                                 | 4<br>5 |

|    | 1.0               | Organiz  | zation of the Thesis                                            | 5      |

| 2  | Syst              | em View  | v                                                               | 7      |

|    | 2.1               |          | unication Systems Example                                       | 7      |

|    |                   | 2.1.1    | Network Processor (NP)                                          | 9      |

|    |                   | 2.1.2    | Switch Fabric (SF)                                              | 9      |

|    |                   | 2.1.3    | Switch Adapter (SA)                                             | 11     |

|    |                   | 2.1.4    | Switch                                                          | 12     |

|    |                   | 2.1.5    | Summary                                                         | 14     |

|    | 2.2               |          | rocessor Environment Example                                    | 14     |

|    | 2.3               |          | 1 View                                                          | 16     |

|    | 2.4               |          | tion                                                            | 18     |

|    | 2.5               | Traffic  |                                                                 | 20     |

|    |                   | 2.5.1    | Communication Traffic                                           | 21     |

|    |                   | 2.5.2    | Multiprocessor Workload                                         | 23     |

|    |                   |          | 1                                                               |        |

| 3  | Obje              | ective   |                                                                 | 25     |

| 4  | The               | Flow-C   | ontrol Design Problem                                           | 29     |

|    | 4.1               | Basic F  | Flow-Control                                                    | 29     |

|    |                   | 4.1.1    | Definitions                                                     | 30     |

|    |                   | 4.1.2    | Performance                                                     | 30     |

|    | 4.2               | Charac   | terization of FC Schemes                                        | 32     |

|    |                   | 4.2.1    | FC Information                                                  | 33     |

|    |                   | 4.2.2    | Buffer Size                                                     | 33     |

|    |                   | 4.2.3    | Chip Area                                                       | 33     |

|    |                   | 4.2.4    | Summary                                                         | 34     |

|    | 4.3               | Classifi | ication of FC Schemes                                           | 34     |

|    |                   | 4.3.1    | Accounting and Decision at Current Node: The "Grant"-Scheme     | 35     |

|    |                   | 4.3.2    | Distributed Accounting; Decision at Upstream Node: The Absolute |        |

|    |                   |          | Credit Scheme                                                   | 38     |

|   | 4.4  | 4.3.3Accounting and Decision at the Up-stream Node: The Relative Credit41Support of Traffic Classes42 |

|---|------|-------------------------------------------------------------------------------------------------------|

|   | 4.5  | Summary                                                                                               |

| 5 | The  | N-dimensional Flow Control Problem 45                                                                 |

|   | 5.1  | The Cost of FC Information                                                                            |

|   | 5.2  | Point-to-Point Connections $(1 \times 1)$                                                             |

|   |      | 5.2.1 Examples                                                                                        |

|   |      | 5.2.2 Summary                                                                                         |

|   | 5.3  | Point-to-Multipoint Connections $(1 \times N)$                                                        |

|   |      | 5.3.1 General                                                                                         |

|   |      | 5.3.2 Examples                                                                                        |

|   |      | 5.3.3 Summary                                                                                         |

|   | 5.4  | Multipoint-to-Point Connections $(N \times 1)$                                                        |

|   |      | 5.4.1 General                                                                                         |

|   |      | 5.4.2 Examples                                                                                        |

|   |      | 5.4.3 Summary                                                                                         |

|   | 5.5  | Multipoint-to-Multipoint Connections $(N \times N)$                                                   |

|   | 5.5  | 5.5.1 General                                                                                         |

|   |      | 5.5.2 Examples                                                                                        |

|   |      | 5.5.3 Summary                                                                                         |

|   | 5.6  | Switching         55           55         55                                                          |

|   | 5.0  | 5.6.1 Dedicated Input Port and Shared Output Queues                                                   |

|   |      | 5.6.2 Combined Input 1 oft and Shared Output Queues                                                   |

|   |      | 5.6.3 Combined Input and Crosspoint Queued (CICQ) Switches                                            |

|   |      | 5.6.4 Application Example: Optimized Grant and Relative Credit 61                                     |

|   | 5.7  | Conclusions                                                                                           |

|   | 5.7  |                                                                                                       |

| 6 | Swit | ch Architecture Design using Flow Control Domains (FCDs) 67                                           |

| 7 | The  | Decention Scheduler 72                                                                                |

| / |      | Reception Scheduler73Very Operations72                                                                |

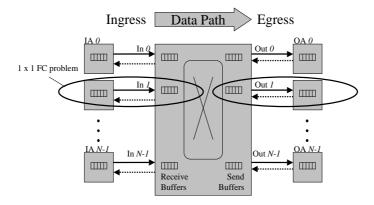

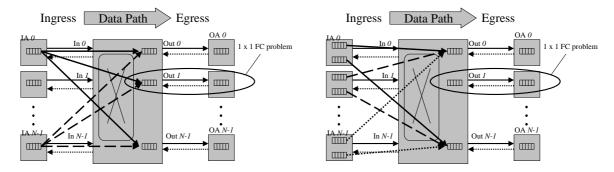

|   | 7.1  | Key Questions         73           71         1         Increase         N EC problem         72      |

|   |      | 7.1.1 Ingress - $N \times N$ FC problem                                                               |

|   |      | 7.1.2 Egress - $N \times 1$ FC problem                                                                |

|   | 7.2  | Switch Dynamics and Fairness    75                                                                    |

|   |      | 7.2.1 System Description                                                                              |

|   |      | 7.2.2 Background                                                                                      |

|   |      | 7.2.3 Problem Statement                                                                               |

|   |      | 7.2.4 Experimental Set-up                                                                             |

|   |      | 7.2.5 Results                                                                                         |

|   |      | 7.2.6    Summary and Conclusion    83                                                                 |

|   | 7.3  | Initial Experiments on Credit Scheduling                                                              |

|   |      | 7.3.1 Potential of Credit Scheduling                                                                  |

|   |      | 7.3.2         Parallel Departures         87                                                          |

|   |      | 7.3.3 Risk of Credit Scheduling                                                                       |

|   |      | 7.3.4Summary and Conclusion96                                                                         |

|   | 7.4  | The Reception Scheduler                                                                               |

|   | 7.5  | Reception Scheduler Strategies to Prioritize Credits                                                  |

|   | 7.6  | Performance Results                                                                                   |

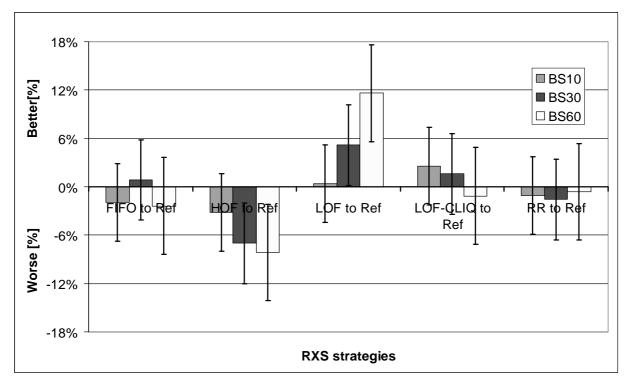

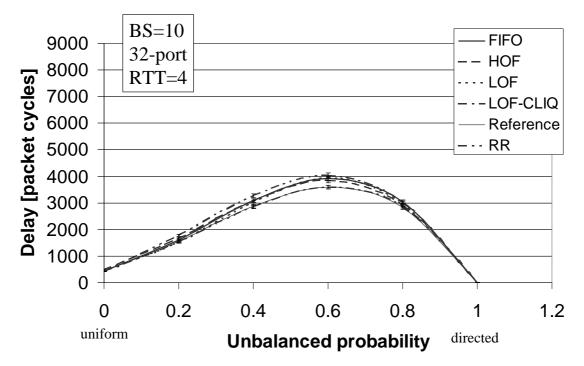

|    |        | 7.6.1     | Comparing Strategies under Design Point Assumptions | 105 |

|----|--------|-----------|-----------------------------------------------------|-----|

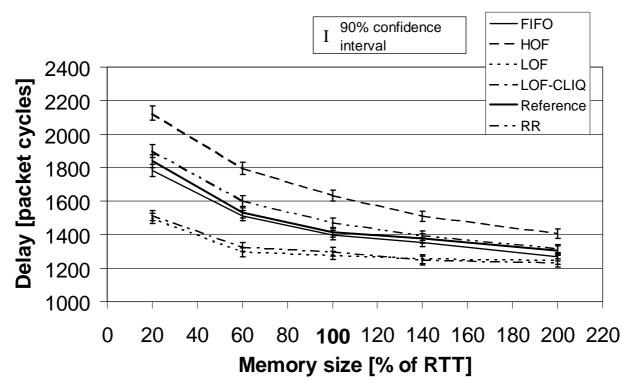

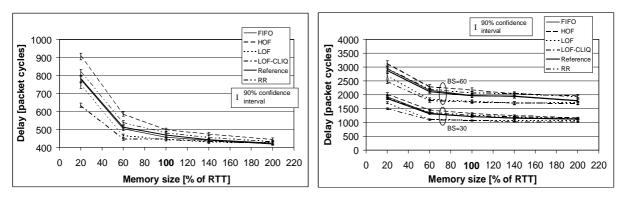

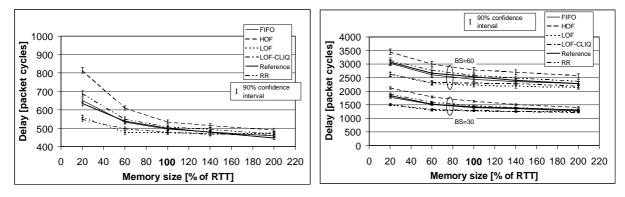

|    |        | 7.6.2     | Impact of Memory Size                               | 110 |

|    |        | 7.6.3     | Impact of Link Length                               | 116 |

|    |        | 7.6.4     | Impact of Non-Uniform Traffic                       | 121 |

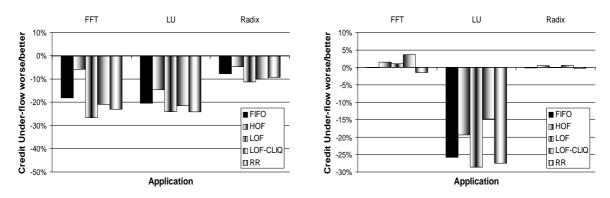

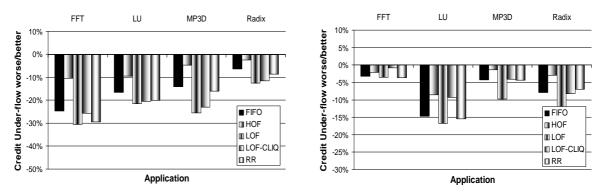

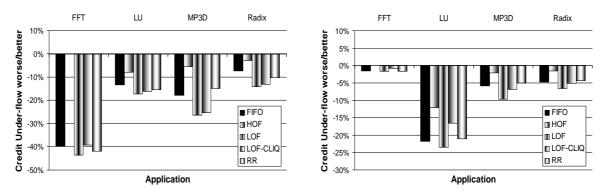

|    |        | 7.6.5     | Impact of Traces of Multiprocessor Workloads        | 131 |

| 8  | Con    | clusions  |                                                     | 135 |

|    | 8.1    | FC sch    | eduling                                             | 135 |

|    | 8.2    |           | cheduler Strategies                                 |     |

|    | 8.3    | Switch    | Dynamics and Fairness                               | 137 |

|    | 8.4    | Future    | Work                                                | 138 |

| A  | Defi   | nitions   |                                                     | 139 |

| B  | Why    | v Cables  | ? - An Example, IBM PowerPRS                        | 141 |

| С  | Imp    | lication  | of dropping packets                                 | 143 |

| D  | Burs   | sty Trafi | fic Model                                           | 145 |

| E  | Desc   | ription   | of the Multiprocessor Applications                  | 147 |

| Bi | bliogr | aphy      |                                                     | 151 |

# **List of Figures**

| 2.1  | A Communication Systems Network                                                                                                                                               | 7  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Inside a Networking Node                                                                                                                                                      | 8  |

| 2.3  | Previous Generation of Switch Fabrics                                                                                                                                         | 10 |

| 2.4  | Next Generation of Switch Fabrics                                                                                                                                             | 11 |

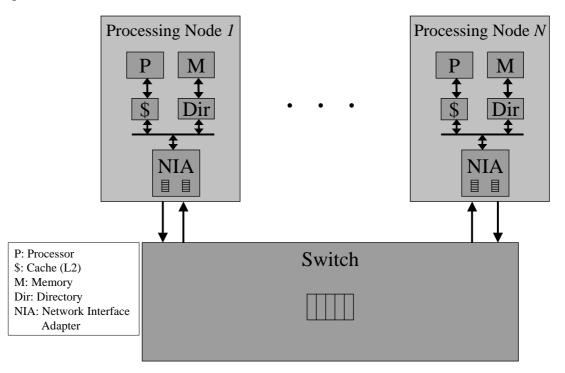

| 2.5  | Multiprocessor Network                                                                                                                                                        | 15 |

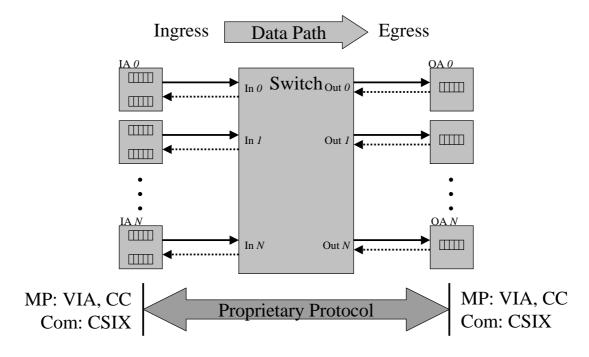

| 2.6  | Unfolded Switch Fabric                                                                                                                                                        | 17 |

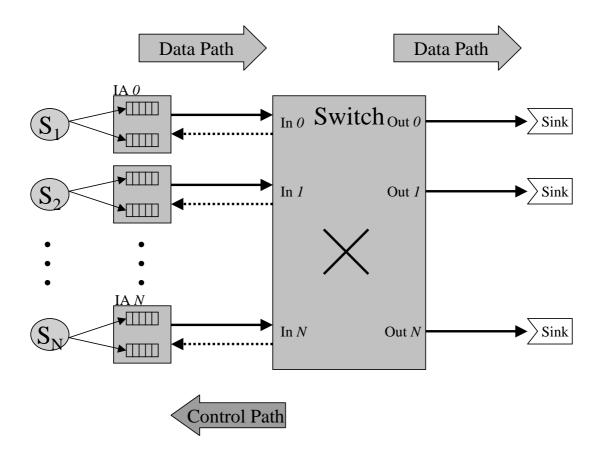

| 2.7  | Abstracted Switch Model                                                                                                                                                       | 18 |

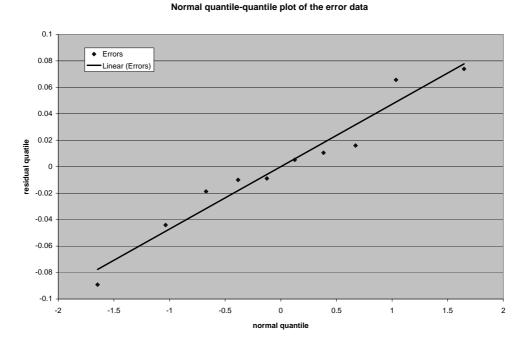

| 2.8  | Normal Quantile-quantile Plot for the Error Data                                                                                                                              | 20 |

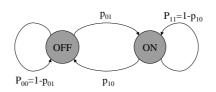

| 2.9  | Two-state Markov chain                                                                                                                                                        | 22 |

| 4.1  | The General FC Problem                                                                                                                                                        | 29 |

| 4.2  | Stateless FC Protocol: Grants                                                                                                                                                 | 35 |

| 4.3  | Stateless FC Protocol: Optimized Grants                                                                                                                                       | 37 |

| 4.4  | Stateful FC Protocol: Absolute Credit Update                                                                                                                                  | 38 |

| 4.5  | Stateful FC Protocol: Absolute Credit Update – FC Bandwidth Optimized                                                                                                         | 40 |

| 4.6  | Stateful FC Protocol: Absolute Credit Update – Buffer and FC Bandwidth Op-                                                                                                    |    |

|      | timized                                                                                                                                                                       | 40 |

| 4.7  | Stateful FC Protocol: Relative Credit Update                                                                                                                                  | 41 |

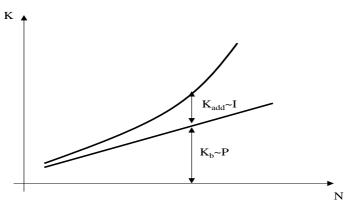

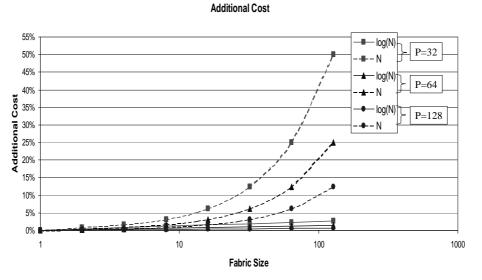

| 5.1  | Flow Control Levels                                                                                                                                                           | 46 |

| 5.2  | Cost Model                                                                                                                                                                    | 47 |

| 5.3  | Projection of the Per-link FC Cost                                                                                                                                            | 48 |

| 5.4  | The $1 \times N$ FC Problem                                                                                                                                                   | 50 |

| 5.5  | The $N \times 1$ FC Problem                                                                                                                                                   | 52 |

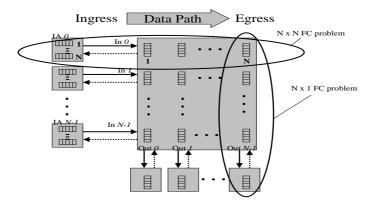

| 5.6  | The $N \times N$ FC Problem $\ldots \ldots \ldots$            | 54 |

| 5.7  | A Switch with $1 \times 1$ FC Problems $\ldots \ldots \ldots$ | 56 |

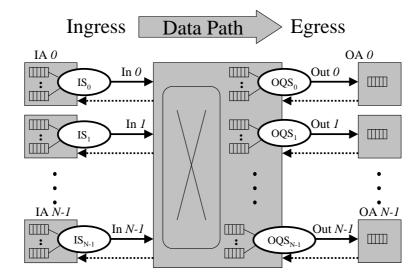

| 5.8  | CIOQ Switching Architecture                                                                                                                                                   | 56 |

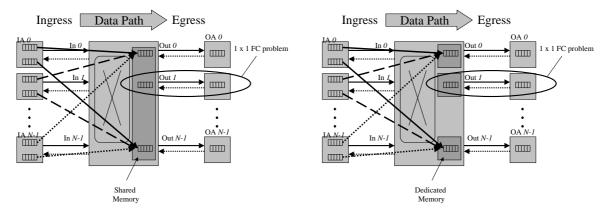

| 5.9  | CIOQ/VOQ with; a) Shared, b) Dedicated Memory                                                                                                                                 | 57 |

| 5.10 | CICQ Switching Architecture                                                                                                                                                   | 59 |

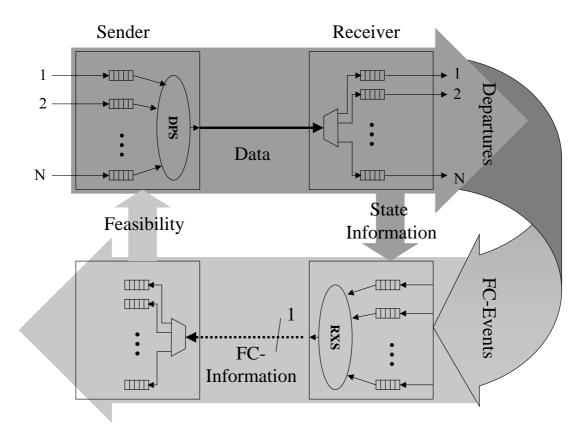

| 6.1  | Flow Control Scheduling of a Single Link                                                                                                                                      | 68 |

| 6.2  | Switch Fabric Composed of Autonomous Flow Control Domains                                                                                                                     | 69 |

| 7.1  | Important Scheduling Points in a Switch Fabric                                                                                                                                | 75 |

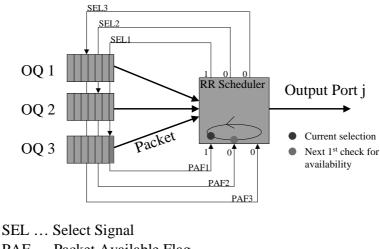

| 7.2  | Simplified Schematic of a Data Path Scheduler Applying Round-Robin                                                                                                            | 78 |

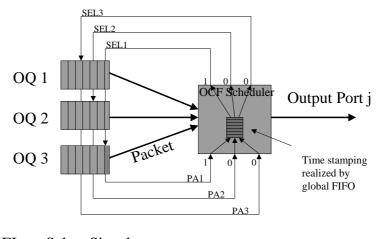

| 7.3  | Simplified Schematic of a Data Path Scheduler Applying Oldest-Cell-First                                                                                                      | 79 |

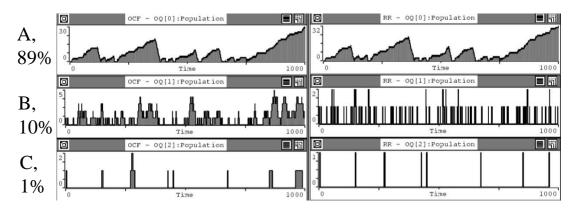

| 7.4  | A, B, C Send 89%, 10%, and 1% of (Output) Link Capacity to D                                                                                                                  | 80 |

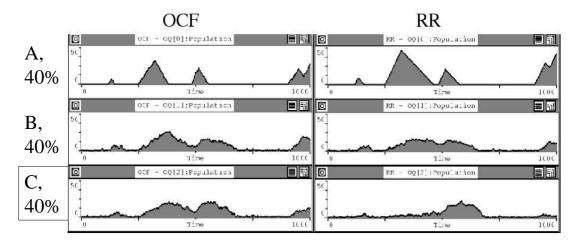

| 7.5  | A, B, and C Send 40% Bursty, 40% Non-bursty, and 40% Non-bursty Traffic to D                                                                                                  | 81 |

| 7.6  | A, B, and C Send 50% Bursty, 50% Non-bursty, and 5% Non-bursty Traffic to D                                                                                                   | 82 |

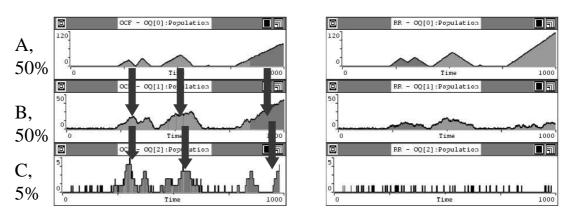

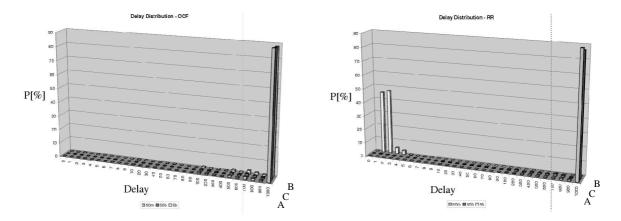

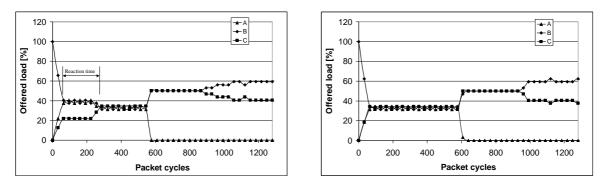

| 7.7  | Comparison of Delay Distribution                                                                                                                                              | 83 |

| 7.8  | Comparison of Dynamics of a Switch                                            | 83   |

|------|-------------------------------------------------------------------------------|------|

| 7.9  | Experimental Setup for Initial Analysis on FC Scheduling                      | 85   |

| 7.10 | Average FIFO Population for $N = 8$                                           | 87   |

| 7.11 | Average FIFO Population for $N = 16$                                          | 87   |

| 7.12 | Average FIFO Population for $N = 32$                                          | 87   |

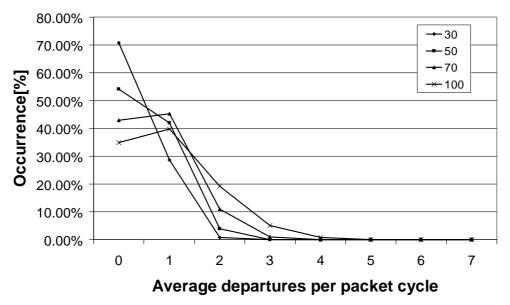

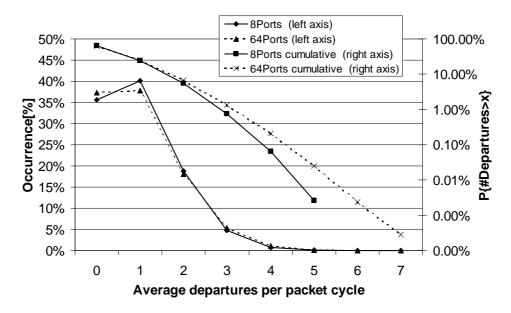

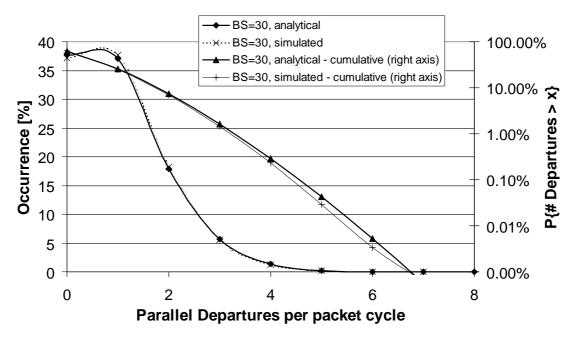

|      | The Distribution of Output Departures                                         |      |

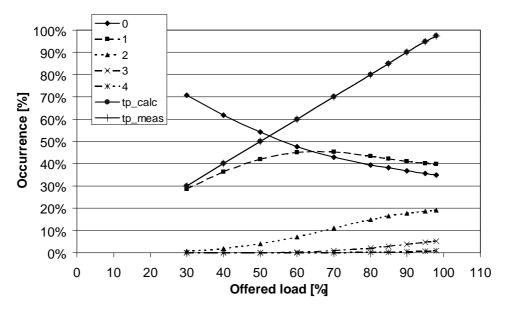

|      | The Influence of Input Load on Output Departures                              |      |

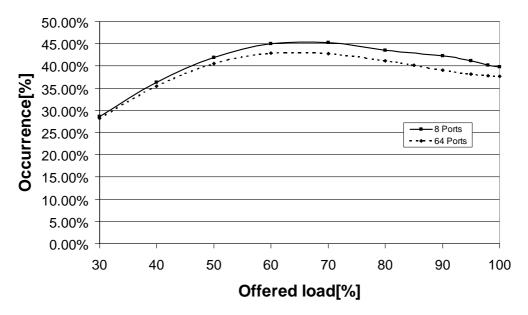

|      | A Single Output Departure in Comparison for a $N = 8$ , and 64 Port Device    |      |

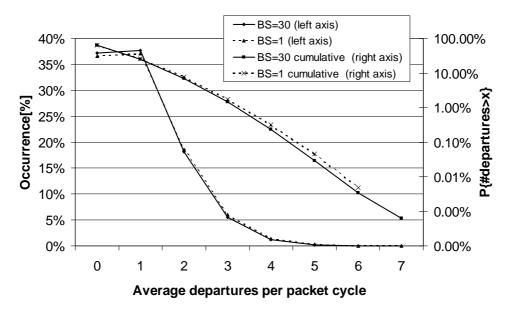

|      | The Influence of Bursts on Output Departures                                  |      |

|      | The Influence of the Switch Dimension on Output Departures                    |      |

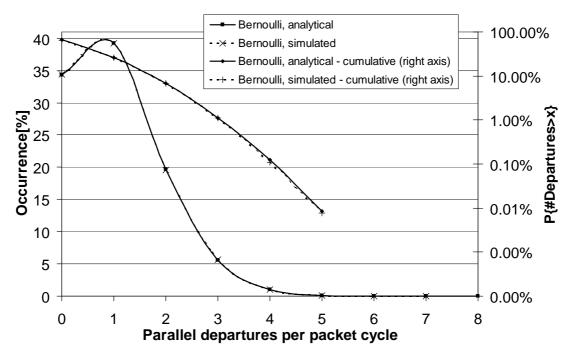

| 7.18 | Comparison of Simulation and Analytical Modelling for Uniform Traffic and     |      |

|      | Small Switch Sizes                                                            | 93   |

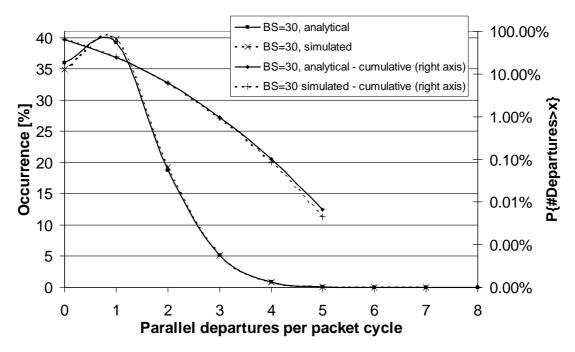

| 7.19 | Comparison of Simulation and Analytical Modelling for Bursty Traffic and      |      |

|      | Small Switch Sizes                                                            | 93   |

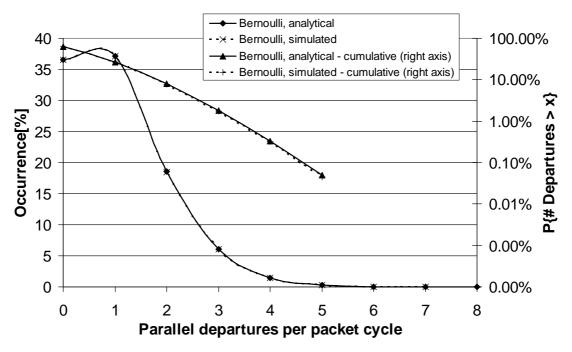

| 7.20 | Comparison of Simulation and Analytical Modelling for Uniform Traffic and     |      |

|      | Large Switch Sizes                                                            | 94   |

| 7.21 | Comparison of Simulation and Analytical Modelling for Bursty Traffic and      |      |

|      | Large Switch Sizes                                                            | 94   |

| 7.22 | Comparison of a FC Channel with Partial Return of FC Information by Serial-   |      |

|      | ization and Complete Return of FC Information                                 | 95   |

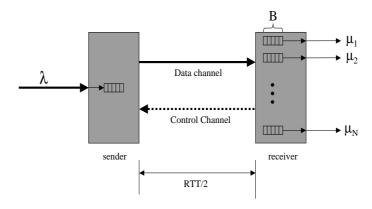

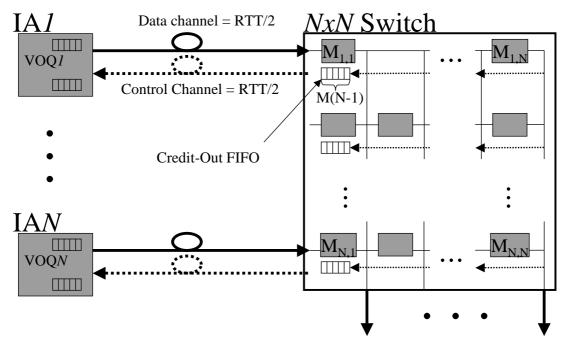

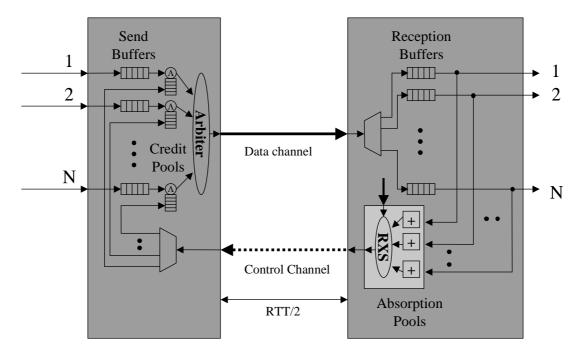

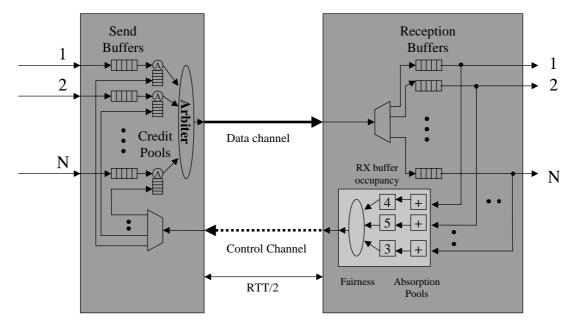

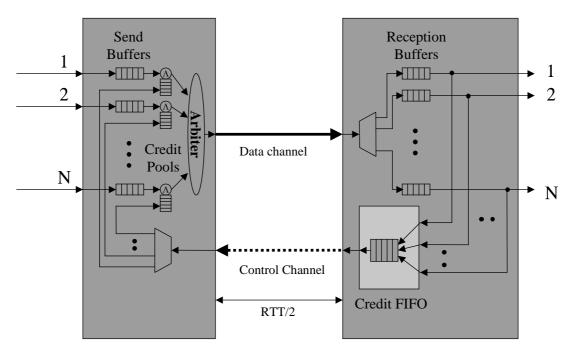

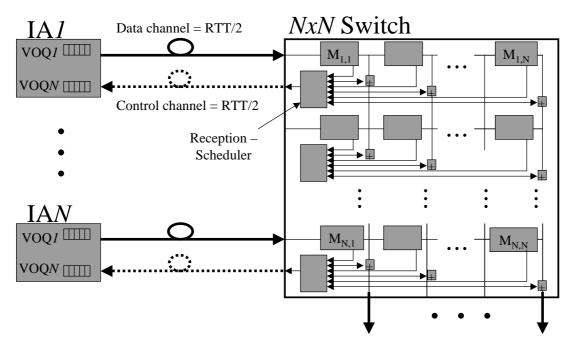

| 7.23 | A $N \times N$ Credit FC with a Bandwidth-limited FC Channel                  | 98   |

| 7.24 | Random RXS Strategy                                                           | 99   |

| 7.25 | Spatial RXS Strategy                                                          | 100  |

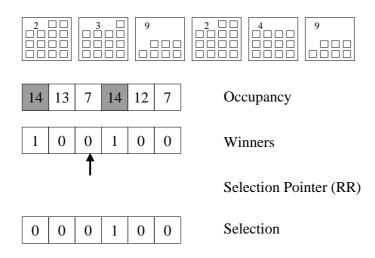

| 7.26 | Highest Occupancy First (HOF) RXS Strategy                                    | 101  |

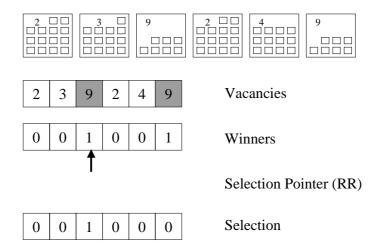

| 7.27 | Lowest Occupancy First (LOF) RXS Strategy                                     | 101  |

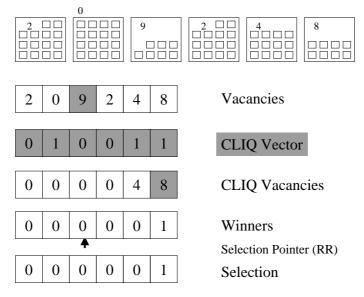

| 7.28 | Lowest Occupancy First Considering the Communicated Length of the Input       |      |

|      | Queues (LOF-CLIQ) RXS Strategy                                                | 102  |

| 7.29 | Temporal RXS (FIFO) Strategy                                                  | 103  |

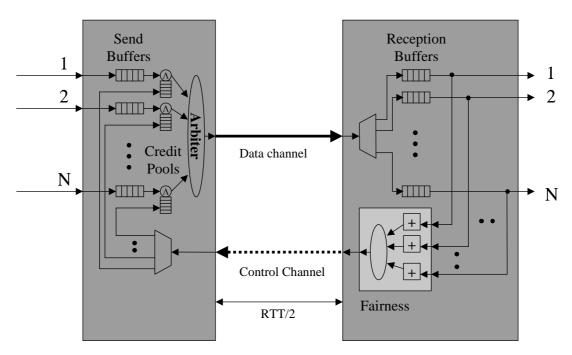

| 7.30 | Exemplary CICQ Switch Architecture Using N RXS Modules                        | 104  |

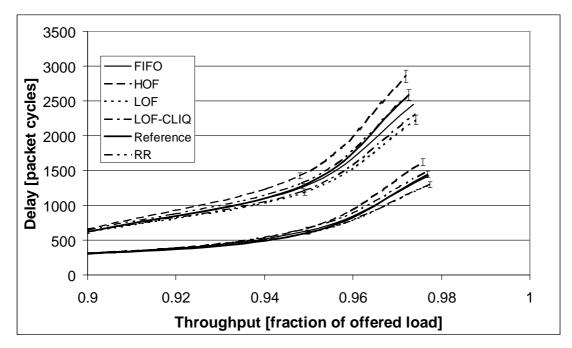

| 7.31 | RXS Strategies in Comparison to Unscheduled FC and Bandwidth of $N$ (Ref-     |      |

|      | erence): $N = 8$                                                              | 106  |

| 7.32 | RXS Strategies in Comparison to Unscheduled FC and Bandwidth of $N$ (Ref-     |      |

|      | erence): $N = 16$                                                             | 107  |

| 7.33 | RXS Strategies in Comparison to Unscheduled FC and Bandwidth of $N$ (Ref-     |      |

|      | erence): $N = 32$                                                             |      |

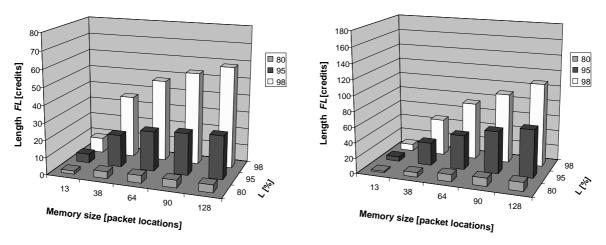

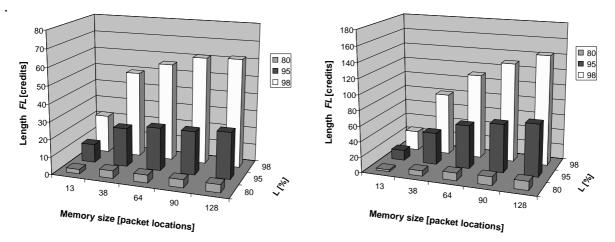

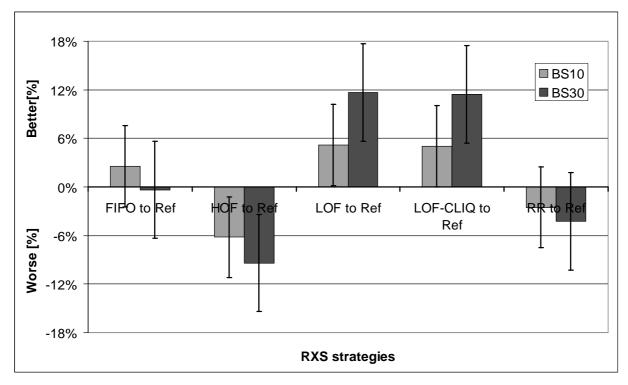

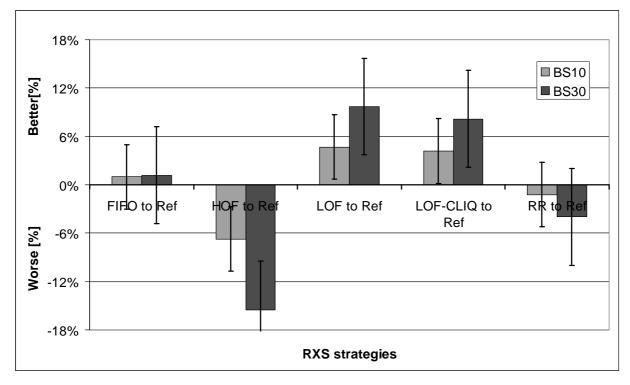

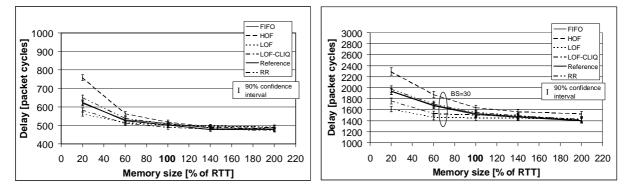

|      | Impact of Buffer Size on Performance, Exemplary Result: $N = 16$              |      |

|      | Impact of Buffer Size on Performance $N = 8$                                  |      |

| 7.36 | Impact of Buffer Size on Performance $N = 16$                                 | 112  |

| 7.37 | Impact of Buffer Size on Performance $N = 32$                                 | 112  |

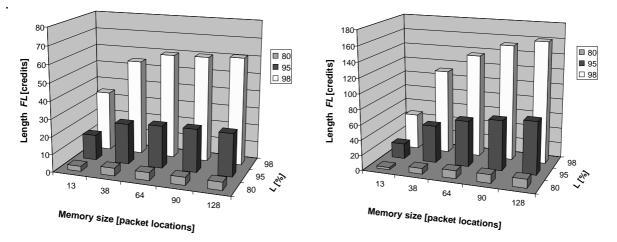

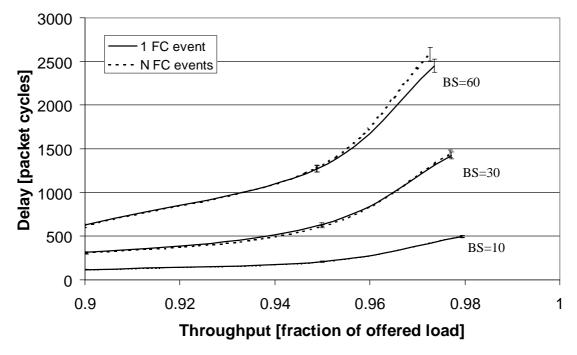

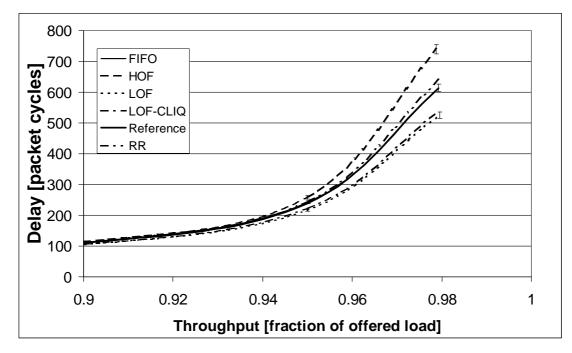

| 7.38 | Switch Performance for High Loads, Small Bursts and Short Links               | 117  |

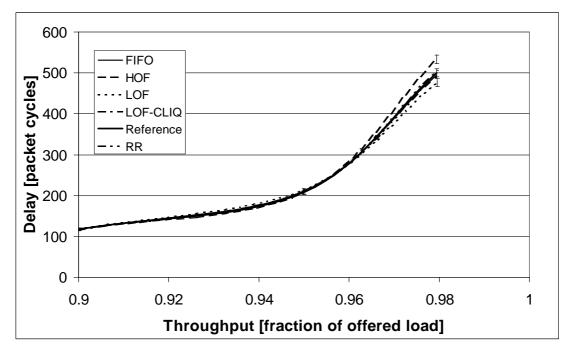

| 7.39 | Switch Performance for High Loads, Small Bursts and Long Links                | 117  |

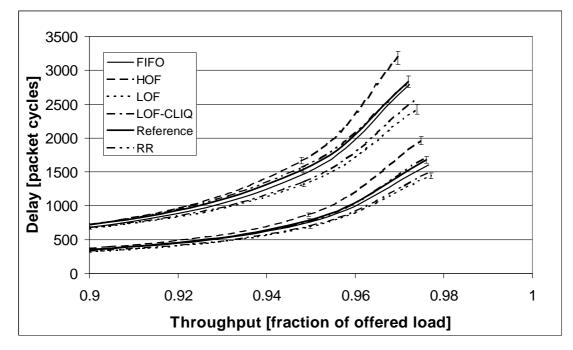

| 7.40 | Switch Performance for High Loads, Large Bursts and Short Links               | 118  |

| 7.41 | Switch Performance for High Loads, Large Bursts and Long Links                | 118  |

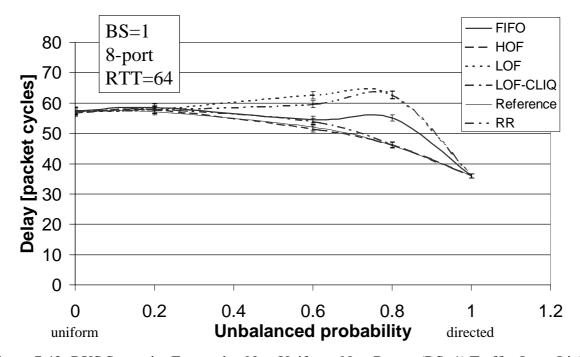

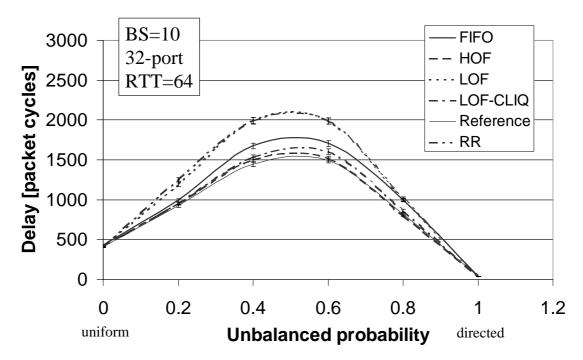

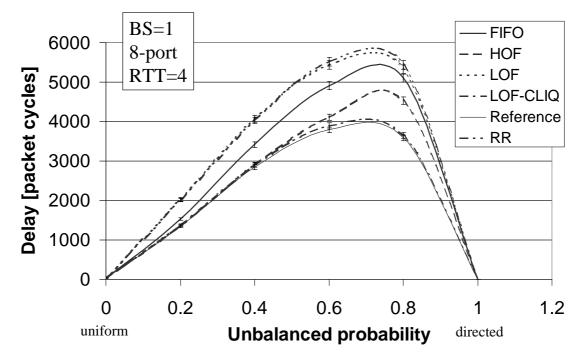

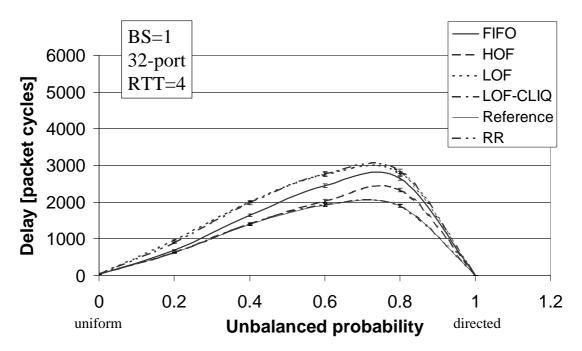

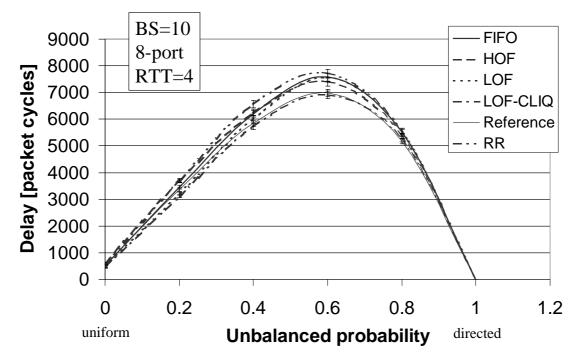

| 7.42 | RXS Strategies Exposed to Non-Uniform, Non-Bursty Traffic, Long Links and     |      |

|      | N=8                                                                           | 122  |

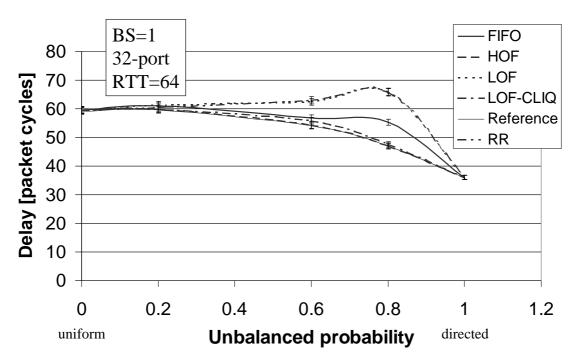

| 7.43 | RXS Strategies Exposed to Non-Uniform, Non-Bursty Traffic, Long Links and     |      |

|      | N = 32                                                                        |      |

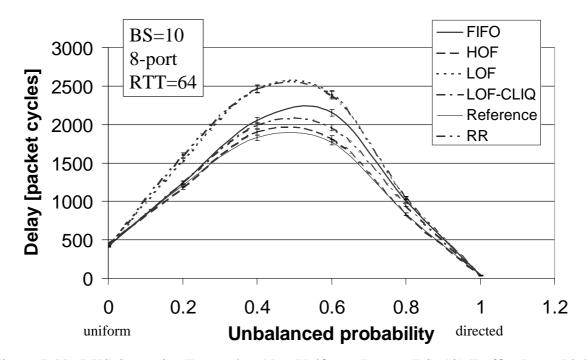

|      | RXS Strategies Exposed to Non-Uniform, Bursty Traffic, Long Links and $N =$   |      |

| 7.45 | RXS Strategies Exposed to Non-Uniform, Bursty Traffic, Long Links and $N = 3$ | 2123 |

| 7.46 | RXS Strategies Exposed to Non-Uniform, Non-Bursty Traffic, Short Links and         |

|------|------------------------------------------------------------------------------------|

|      | N = 8                                                                              |

| 7.47 | RXS Strategies Exposed to Non-Uniform, Non-Bursty Traffic, Short Links and         |

|      | $N = 32  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $          |

| 7.48 | RXS Strategies Exposed to Non-Uniform, Bursty Traffic, Short Links and $N = 8125$  |

| 7.49 | RXS Strategies Exposed to Non-Uniform, Bursty Traffic, Short Links and $N = 32125$ |

| 7.50 | RXS Strategies Exposed to Traces, 4-Node Multiprocessor                            |

| 7.51 | RXS Strategies Exposed to Traces, 16-Node Multiprocessor                           |

| 7.52 | RXS Strategies Exposed to Traces, 32-Node Multiprocessor                           |

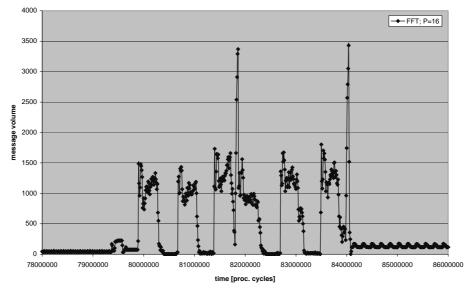

| E.1  | FFT Trace File                                                                     |

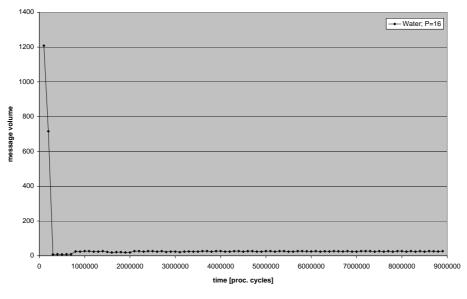

| E.2  | Water Trace File                                                                   |

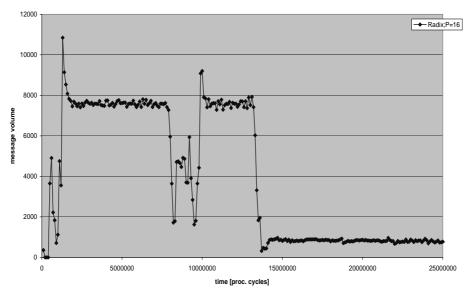

| E.3  | Radix Trace File         149                                                       |

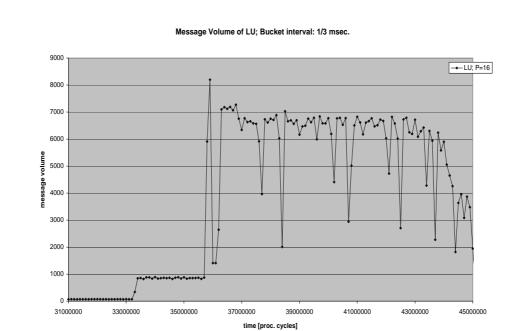

| E.4  | LU Trace File                                                                      |

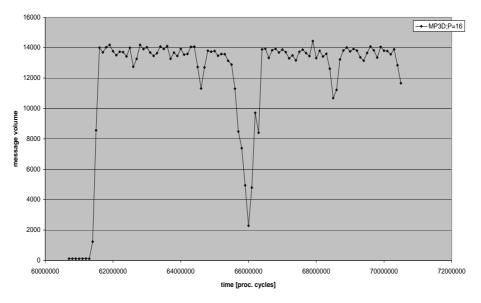

| E.5  | MP3D Trace File                                                                    |

# **List of Tables**

| 2.1  | Multiprocessor System Parameters                                                                                                  | 16  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Application Parameters                                                                                                            | 23  |

| 4.1  | Comparison of FC Schemes                                                                                                          | 43  |

| 5.1  | $1 \times N$ FC Problem Complexity $C_{1N}$ for Stateless and Stateful FC Classes and the Required Amount of FC Information $I$ . | 52  |

| 5.2  | $N \times 1$ FC Problem Complexity $C_{N1}$ for Stateless and Stateful FC Classes and the Required Amount of FC Information $I$ . | 53  |

| 5.3  | $N \times N$ FC Problem Complexity $C_{NN}$ for Stateless and Stateful FC Classes and the Required Amount of FC Information $I$ . | 54  |

| 5.4  | Mapping of <i>N</i> -dimensional FC Problem onto Switching Architectures                                                          | 56  |

| 5.5  | Mapping of <i>N</i> -dimensional FC Problem onto CIOQ Switching Architectures.                                                    | 59  |

| 5.6  | Mapping of N-dimensional FC Problem onto CICQ Switching Architectures                                                             | 61  |

| 5.7  | Total Complexity and Aggregate FC Bandwidth in Gb/s for CIOQ Switches                                                             | 63  |

| 5.8  | Total Complexity and Aggregate FC Bandwidth in Gb/s for CICQ Switches                                                             | 64  |

| 6.1  | Quantification of the Total FC Overhead in Gb/s for Various Subclasses of CIOQ Architectures and System Sizes $N$ .               | 72  |

| 7.1  | Measured Delay Statistics of 89/10/1                                                                                              | 80  |

| 7.2  | Measured Delay Statistics of 40/40/40                                                                                             | 81  |

| 7.3  | Measured Delay Statistics of 50/50/5                                                                                              | 82  |

| 7.4  | System Parameters of the Credit Contention Evaluation                                                                             | 96  |

| 7.5  | System Parameters of the Evaluation of Partial/Full Return of FC Information .                                                    | 97  |

| 7.6  | Performance Gain/Loss of HOF, LOF, LOF-CLIQ, FIFO and RR Compared to                                                              | 107 |

| 77   | Reference                                                                                                                         | 107 |

| 7.7  | Performance Differences of RXS Strategies in Comparison to Reference for Variation in Memory and Burst Size, and Ports            | 113 |

| 7.8  | Importance and Significance of the two Factors RXS and System Size                                                                | 113 |

| 7.9  | Performance Differences of RXS Strategies in Comparison to Reference Aver-                                                        | 111 |

| 7 10 | aged over Ports                                                                                                                   | 114 |

| /.10 | System Parameters of the Evaluation of the Influence of Memory Size on Switch Performance                                         | 115 |

| 7.11 | Performance Differences of RXS Strategies in Comparison to Reference for                                                          |     |

|      | Variation in Link Lengths, Load, and Ports                                                                                        | 119 |

|      | Importance and Significance of the Factor Link Length                                                                             | 120 |

| 7 13 | System Parameters of the Evaluation of the Influence of the Link Length                                                           | 120 |

| 7.14 | Performance Differences of RXS Strategies in Comparison to Reference for       |     |

|------|--------------------------------------------------------------------------------|-----|

|      | Variation in Degree of Non-uniformity of Traffic, Burst Size, Link Length, and |     |

|      | Ports                                                                          | 126 |

| 7.15 | Calculation of the Effects for Non-uniform Traffic                             | 127 |

| 7.16 | ANOVA Table for Non-uniform Traffic                                            | 127 |

| 7.17 | Importance and Significance of the two Factors RXS and System Size             | 128 |

| 7.18 | Performance Differences of RXS Strategies in Comparison to Reference Aver-     |     |

|      | aged over Ports for Short Links                                                | 128 |

| 7.19 | Performance Differences of RXS Strategies in Comparison to Reference Aver-     |     |

|      | aged over Ports for Long Links                                                 | 128 |

| 7.20 | System parameters of the Evaluation of the Influence of Non-uniform Traffic .  | 130 |

# **List of Symbols**

- $\rho\,$  throughput, intensity

- B buffer size

- BS average burst size with geometrically distributed burst lengths

- I flow control information

- L load; the average traffic load offered to the switch fabric

- $M\,$  cross-point memory or memory size of the buffered switch; M and B are used interchangeably

- ${\cal N}\,$  number of input or output ports of a switch fabric

- P packet length expressed in bits/bytes

- RTT round-trip time; typically expressed in packet cycles

- tu a time unit expressed in packet cycles

# Abbreviations

| ATM  | Asynchronous Transfer Mode              |

|------|-----------------------------------------|

| ARQ  | Automatic Repeat Request                |

| BAT  | Bandwidth Allocation Technology         |

| BGM  | Bipartite Graph Matching                |

| CBR  | Constant Bit Rate                       |

| CIOQ | Combined-Input Output-Queued            |

| CICQ | Combined-Input Crosspoint-queued        |

| CMOS | Complementary Metal-Oxide Semiconductor |

| DRR  | Dual Round Robin                        |

| ECC  | Error Correction Code                   |

| FC   | Flow Control                            |

| FCD  | Flow Control Domain                     |

| FCSD | Flow Control Subdomain                  |

| FFT  | Fast Fourier Transformation             |

| FIFO | First-in First-out                      |

| Gb/s | Gigabit per second                      |

| HOF  | Highest Occupancy First                 |

| HOL  | Head-of-Line                            |

| HDLC | High-Level Data Link Control            |

| IBM  | International Business Machines         |

| IA   | Input Adapter                           |

| ISO  | International Standard Organization     |

| LAN  | Local Area Network                      |

| LOF  | Lowest Occupancy First                  |

| LOF-CLIQ | LOF Communicated Length of Input Queues                                                       |

|----------|-----------------------------------------------------------------------------------------------|

| LT       | Line Termination                                                                              |

| LU       | is not an abbreviation, but relates to the factorization of a matrix into submatrices L and U |

| MAN      | Metropolitan Area Network                                                                     |

| MESI     | Modified Exclusive Share Invalidate                                                           |

| MP       | Multi Processors                                                                              |

| NIA      | Network Interface Adapter                                                                     |

| NP       | Network Processor                                                                             |

| NUMA     | Non-Uniform Memory Access                                                                     |

| OA       | Output Adapter                                                                                |

| OSI      | Open Systems Interconnection                                                                  |

| OC       | Optical Carrier                                                                               |

| OCF      | Oldest Cell First                                                                             |

| OQS      | Output Queue Scheduler                                                                        |

| RED      | Random Early Discard                                                                          |

| RR       | Round Robin                                                                                   |

| RSIM     | Rice Simulator for Instruction-level parallelism Multiprocessors                              |

| SA       | Switch Adapter                                                                                |

| SAN      | Storage Area Network                                                                          |

| SES      | Scientific and Engineering Software                                                           |

| SF       | Switch Fabric                                                                                 |

| SP       | Scalable POWERparallel                                                                        |

| SPLASH   | Stanford Parallel Applications for Shared Memory                                              |

| ТСР      | Transmission Control Protocol                                                                 |

| UDP      | User Datagram Protocol                                                                        |

| SMP      | Shared Memory Processor                                                                       |

| VBR      | Virtual Bit Rate                                                                              |

| VOQ      | Virtual Output Queueing                                                                       |

| VLSI     | Very Large Scale Integration                                                                  |

|          |                                                                                               |

- WAN Wide Area Network

- **WFQ** Weighted Fair Queueing

- WRR Weighted Round Robin

## Chapter 1

## Introduction

#### **1.1 Relationship to a General Problem**

Having the right information at the right time has always been a great advantage. Consider for instance someone driving in a car in a region unknown to him. If the street signs were to show him all possible options towards the destination chosen, he would be overwhelmed by the wealth of information. On the contrary, it would take him much longer to arrive at his destination as if the signs would just signal one option. When looking for a parking lot in a big city, the right information at the right time can really be useful. The driver has a parking garage in mind, but does not know whether it is full. Well, he just tries and it might turn out to be no problem, but he does not know before hand. If, however, the garage is full, it not only contributed significantly to his searching time, but also increased the overall utilization of the streets. If there are signs at major points in the city that inform the drivers about the parking status of the various garages, a driver will know in advance whether it is worth going where he initially wanted to park. With such a parking information system, which is by the way being employed in major cities in Europe, the time to park one's car can be reduced. This is a great advantage for the individual driver, as he is faster in finding a parking space. It is also an advantage for the overall traffic situation as a whole, because drivers will not contribute to traffic congestion, as they would if their parking aim was unsuccessful and they had to look for new opportunities.

This observation is the basic principle of the optimization effort in the design of switch fabrics carried out in this thesis. It will be applied for the flow-control mechanism that is used between switch adapters and the switch core.

### **1.2 Status Quo in Switching**

As switching is being realized in hardware it is exposed to the constant progress in technological development. Moreover, switch design has to meet market and customer requirements.

The market requires not only higher port speeds, but also more ports. The customer requires more distinctions of traffic classes, that is more knowledge about what kind of packets are being switched, to differentiate classes of service.

A switching subsystem consists of adapters, typically one per switch port, which need to be interconnected by a switch core. As the transistor density scales with roughly 1.5 and the chip area with 1.1 to 1.25 per year, the number of transistors per chip increases with 1.6 to 1.8 per year. This is commonly known as "Moore's Law". With the increase in chip density, there is a corresponding decline in the cost per transistor. As a consequence larger buffers become

affordable nowadays. Moreover, computational power, i.e. the logic on a chip, becomes cheaper over time. With current CMOS technology, the problem is to move data on and off the chip and with current interconnection technology across boards and card edges. We refer to this broadly as the problem of interconnection technology which has much more facets, such as size and pitch of card connectors, speed and supported distance of backplane interconnection systems, card and rack form factors, layers of metal realizing the chip internal wiring, and as the packaging problem to move the data on and off the chip. Current electrical backplane technology allows transmission rates of 2.5 Gb/s. For Terabit switches this means thousands of wires, and possibly hundreds of adapters. Such a large switching subsystem clearly no longer fits into a single switch rack, i.e. switch and adapter cards that are connected through a single backplane. A solution are multi-rack systems that are connected by cables, inherently increasing the round-trip time of intra-fabric control loops. Looking back over the past years, the relative cost of interconnect versus switch function has gone up, indicating a shift in optimization criteria. This is the underlying switch-architectural problem domain of this thesis. The interconnection technology is therefore a bottleneck and major contributor to switch cost. Therefore, the switch fabric internal control overhead due to a specific switch architecture design has to be optimized.

As switches are not only used in communication environments, but also in storage area networks, and multiprocessor systems including clusters of PC/workstations, the same concepts and components should be re-usable in these systems. Moreover, as switches also serve different market segments, such as high-end or low-end devices, one architecture should scale to fit all segments. To this end, this thesis was conducted to merge the switch design of communication and multiprocessor environments, in particular because the switch fabrics of communication systems are no longer realized on a single physical entity, but across a multiplicity of physically distant components. This development of switches in communication environments approaches it to a multiprocessor system, and henceforth leads to an overlapping problem domain.

Single-stage switch fabrics are often realized in a combined input- and output-queued architecture. This architecture comes in two flavors, one with a buffered and the other with a bufferless switch. Typically, both apply input queueing per output, commonly known as virtual output queueing. Both have certain shortcomings that we want to address in this thesis.

The bufferless switch fabric has a centralized controller, which schedules packets at all input adapters according to traffic and output availability. It applies scheduling algorithms that are tuned for high aggregate throughput [90]. These scheduling algorithms are challenging to implement as a global state of all adapters and outputs are necessary [96], which requires a high degree of interconnectivity. This clearly is a bottleneck when scaling to larger fabric sizes. However, the problem is not only the interconnection of VOQs and a centralized controller, but also the implementation of an algorithm that is capable of finding a best match of N inputs and outputs in a limited number of packet cycles, such as parallel, iterative matching algorithms.

The buffered switch fabric is an architecture that yields a high aggregate throughput. It typically employs a shared memory architecture that is limited by memory access bandwidth [34] or the size of input and output routers to packet storing locations [93]. Moreover, the amount of flow-control information to convey is large.

If not properly addressed, these two architectural choices leave little room for supporting different traffic classes. An architecture that seems to be very attractive for supporting quality-of-service (QoS) by design is a cross-point buffered switch architecture. The drawback of such an architecture is the large amount of buffers required as it scales on the order of  $O(N^2)$ , N being the number of switch ports. However, with the technological progress mentioned earlier, this disadvantage increasingly looses importance as compared to the other two architectures. It was only recently that this type of architecture received more attention [47, 46, 49, 48]. We

believe that time has come to investigate this type of architecture. A recent publication showed that such an architecture is also feasible for large round-trip times [41]. Because of the high cost of buffers, researchers refrained from investigating such a switch architecture. This thesis will analyze this architecture, in particular considering large round-trip times.

### **1.3 Open Problems**

In view of the market demands for ever higher bandwidth and more ports and because of the interconnection bottleneck, a high-speed switch fabric will be realized in the foreseeable future using long links. However, the question of the impact that long links have on performance and resource consumption has not yet been addressed appropriately. For instance in [11], long links and flow control were analyzed, but under the aspect of a single link as part of an irregular topology. In our work, we address similar aspects from the perspective of a single link as part of a switch fabric, which is an aggregation point of links. We additionally address issues of flow-control overhead.

Owing to the fact that in the past a switch had been feasible on a single rack, the issue of flow-control bandwidth was rarely considered. For instance in [17], flow-control channel limitations have been considered for TCP/IP (Transmission Control Protocol/Internet Protocol), which is an end-to-end flow-control protocol. While the authors describe the phenomena of acknowledgment congestion, which relates to the congestion of flow-control events in this thesis, and its impact on performance of one and multiple TCP connections, our research is more strongly focused on, but not limited to, a link-level flow-control scheme. We offer flow-control scheduling as a solution to reverse path congestion. We believe that flow-control scheduling can be applied without limitations to scheduling acknowledgements in an end-to-end flow-control protocol, such as TCP/IP. However, this would be beyond the scope of this thesis.

Although important, flow control is an issue that has attracted less attention in recent years. It has numerous facets that are complex and often confusing. For instance in [23], a comprehensive survey of flow control was given. Since this publication, which dates back to 1979, much has changed and some additions to that survey, such as an evaluation of flow control complexity and switch-fabric-internal flow control schemes, are necessary. There has been a come-back of flow-control issues in the early 90's. The discussion was led by [8, 10] who made credit flow-control popular. The grant flow-control scheme was carried on for instance by [28] with a significant contribution on buffer efficiency. We deliver a framework that allows to catalogue the different schemes.

In the past, the main focus of research in switch architectures was on improving the aggregate throughput of the fabric [90], [37]. It is only recently that more attention is being paid to the aspect of QoS support [48], [60], and [61]. Even though scheduling algorithms are important, scheduling yield can only be as good as the underlying architecture. The relationship between switch architecture and QoS support has not been considered thoroughly.

#### **1.4 What Makes the Problems Difficult?**

Flow control has to provide correctness and assure work-conservation. These requirements have to be fulfilled, and set the framework of any flow control scheme. Often, detailed issues of flow control were intentionally ignored when dealing with switch performance so that the influence

of factors such as buffer size, input and output-queueing, scheduling, packet sizes, traffic behavior, or switch dimension is better understood. When taking also link-length into account, the parameter scope widens, resulting in an even more complicated analysis.

As flow control is considered a solved problem, it is difficult to convince colleagues and researchers of the necessity of reconsidering flow control.

Provided an infinite flow control channel, it is easy to achieve, with the switch fabric assumed here, good performance results. However, we try to minimize the flow control overhead and maintain the good performance. It is not obvious how to achieve this, in particular when exposing the switch fabric to communication and multiprocessor environments and their typical traffic behavior.

Issues of QoS have been reduced to simple priorities in the past. Already here the issues are very complex. We will attempt to provide a foundation by means of an appropriate switch architecture to have better support of QoS-related aspects that go beyond priorities such as bandwidth and delay guarantees.

Finally, all ideas ultimately have to be feasible, as the switch will be built in real hardware. We refer to [41] for a comprehensive feasibility study of the switch architecture utilized in this thesis.

### **1.5** Contributions of this Thesis

This thesis starts with a comprehensive survey of flow control schemes and their application in buffered switches. It introduces a classification of flow control schemes that embeds relevant existing schemes. Flow control complexity is introduced as an abstraction of the chip area consumed, which allows a quantification of the trade-off between implementational cost and flow-control bandwidth, i.e. flow control overhead. With flow-control scheduling, a mechanism is introduced that achieves robust switch performance for varying traffic characteristics and link lengths at low flow control overhead. This makes the scheme attractive to be used in communication as well as in multiprocessors switches, and allows the switch dimensions to be scaled. Furthermore, flow control scheduling is a reusable building block to realize multistage fabrics. With flow control scheduling, a simple and easy-to-understand principle provided by mother nature has been realized in technology. It is the principle of filtering information, which is, for instance, applied in the human body between what the eye sees and what the brain grasps from theses images. In Section 1.1 we gave examples from everyday life in which these principles are also useful. We therefore see a certain generality in our results that could make the scheme attractive for instance for TCP/IP by scheduling the reverse channel, which carries the acknowledgements of typically different connections. We provide reasons for and insight into the necessity of the output-queue organization of switches to support different QoS aspects. These aspects relate to communication as well as multiprocessor switches.

Beyond the scope of this thesis are multi-stage switch fabrics, end-to-end flow-control schemes, and multicast or multi-class traffic.

### **1.6** Organization of the Thesis

This dissertation is structured as follows: Chapter 1 (this chapter), provides a general overview of this thesis by relating it to an everyday problem, summarizing the current state of the art in switch architecture, pointing out shortcomings and briefly discussing the solution this thesis tries to give. Chapter 2 outlines the problem domain. Here, we abstract the two target switching environments of communication and multiprocessor systems to derive a unified model. We give reasons for the abstractions and assumptions made in this work. As we perform our analysis mainly by simulations, we also present the simulation technique and the traffic patterns applied to the model. After having prepared the problem domain, we state the objectives of this dissertation in Chapter 3. Flow control is introduced in Chapter 4. Here, we present all terms and issues related to flow controlling a single link and classify existing flow control schemes. In Chapter 5 we expand the flow control design problem to N dimensions at either side of the link, and give examples of the resulting arrangements in networking in general and in switching in particular. Based on this discussion, we show in Chapter 6 that for switch design it is advantageous to view the switch as an aggregation point of autonomous flow control domains and propose flow-control scheduling as a solution for reducing flow-control bandwidth while maintaining switch performance. In Chapter 7, we propose various flow-control scheduling strategies and explain their mechanisms. We do a performance analysis by means of simulation to evaluate the behavior of flow control scheduling and the proposed strategies in comparison to an unscheduled flow control channel of unrestricted bandwidth. Furthermore, we provide substance to the discussion on how a switch architecture should be constructed to be able to optimally support QoS aspects. The discussions are two-fold, one for a communication and another one for a multiprocessor environment. Finally, Chapter 8 summarizes the conclusions we arrived at in the course of the work presented in this dissertation.

## Chapter 2

## **System View**

In the introduction, Chap. 1, we outlined that we want to achieve convergence in switches for communication systems, storage area networks and in switches for multiprocessor environments, including clusters of PCs/workstations. For convergence a unified model is necessary. We will derive such a model in Sec. 2.3. This model will be used throughout this thesis to investigate the problems, described in Chap. 3, and do analysis by means of simulation.

Before arriving there, we need to outline a typical example of each system, which is done in Sec. 2.1 for communication and in Sec. 2.2 for multiprocessor switches. We will make abstractions to each system to find a valid model. It is explained why these abstractions do not limit us in the results that will be obtained.

After having found a unified model, we will present our chosen simulation technique in Sec. 2.4 and present the traffic that will be exercised on the model in Sec. 2.5.

A list of definitions that will be used throughout this thesis is presented in Appendix. A. The words that are defined here are written in italic upon their first encounter in the text.

### 2.1 Communication Systems Example

A switch fabric (SF) is exposed to all type of networks and network protocols. Therefore, we start our considerations at a very high level to better understand how a SF is typically embedded in communication systems.

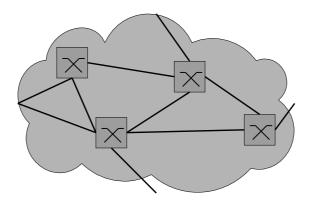

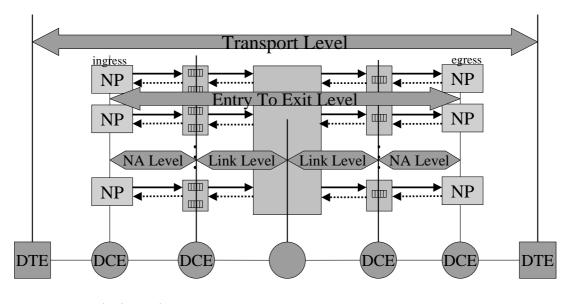

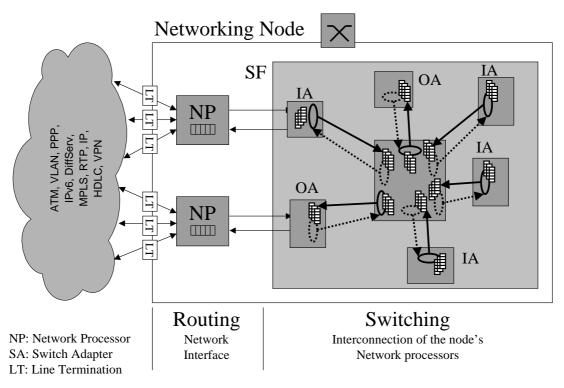

Figure 2.1: A Communication Systems Network

Typically, communication systems are drawn by a cloud representing a network, be it a Local Area Network (LAN), Metropolitan Area Network (MAN), or Wide Area Network (WAN), that runs any type of network protocol, as shown in Fig. 2.1.

The network cloud consists of networking nodes, represented by the boxes in above Figure. The edges interconnecting those boxes are links typically running at optical carrier (OC) speeds, for instance OC-192 (10Gb/s) or OC-768 (40Gb/s). Each networking node is an aggregation point of edges, which interconnects incoming links with outgoing links. Its functions are briefly described as follows:

- **line termination:** allows to physically attach a multiplicity of transmission systems to the node and provides framing functionality;

- **protocol processing:** provides the intelligence and processing power to analyze packet headers, look up, compute and update routing tables, classify packets into predefined service classes, perform other control information and (often complex) rules, and to provide queueing and policing of packets;

- **switching:** provides high-speed, non-blocking [86] interconnection of the various functional units of the networking node.

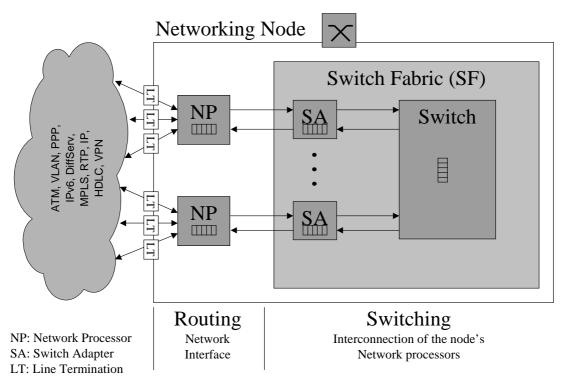

Figure 2.2: Inside a Networking Node

These functions are typically split across logical entities, such as a line termination (LT), network processor (NP) and a SF, which is shown in Fig. 2.2.

For further discussion, we define a queueing point to be a point where a packet can be parsed, checked, modified, or scheduled and experiences queueing time. Queueing time is defined for instance in [97] and is composed of waiting time and service time. Waiting time is the time interval between arrival time and the instant the service begins. Service time is the time required to perform a set or a subset of the functions listed above on the packet. Queueing points are symbolized by a finite queue.

We also define a *frame* to be a data unit of variable length.

#### 2.1.1 Network Processor (NP)

The NP, sometimes also referred to as Traffic Manager (TM), is a queueing point both for ingress and egress. As a functional unit it performs protocol processing as described above. Therefore, it is able to interface to different type of network protocols, such as ATM, VLAN, IPv6, DiffServ, or RTP just to name a few. The ingress NP connects to the input side, while the egress NP connects to the output side of the SF. The ingress NP receives frames of data from the line interface and provides the SF with routing and possibly quality of service (QoS) information, i.e. to let the SF know to which egress NP to forward a frame to under what constrains. Therefore, the network protocol is not seen at the SF. The received data at the egress NP is queued again before being transmitted to the LT and on the output link. It may incorporate sophisticated scheduling algorithms to support priorities and guarantees. Since our interest is the SF, we can already make the following statements:

- 1. In order to be protocol independent, we allow connection-less, as well as connectionoriented operation.

- 2. The type of network protocol is not relevant to our work also due to statement 1. As a conclusion, our SF is applicable to all communication network environments as outlined in Fig. 2.1.

- 3. If a protocol requires QoS provisioning, the SF will support it.

#### 2.1.2 Switch Fabric (SF)

For implementational complexity reasons, it is a well-accepted design technique to use fixedsize packets for packet switches at the hardware level [51, 96]. Throughout this dissertation, we will use the term *packet* for fixed-sized data units. We therefore a assume our SF to operate based on packets.

The SF performs the following two main functions:

- **Routing:** Each packet must be directed independently from its arriving input to the destination output according to the routing information provided by the NP. We assume the routing (and QoS information) given from the NP to be incorporated into the packet, namely into the packet header. For this reason packets are referred to as being *self-routing*.

- **Queueing:** Simultaneous arrival of packets at different inputs destined to the same output causes *output contention*, assuming that only one packet may leave an output per packet cycle. Without dropping packets that lose contention, queueing is necessary. Queueing is therefore a means to resolve output contention. In order to be able to maintain the sequence of flows, a flow being a stream of packets between arbitrary pairs of inputs and outputs of a given service class, all queues obey the first-in first-out (FIFO) service discipline. This is a requirement to be protocol independent and henceforth to also support connection-oriented traffic or service classes. Obviously, this supports connection-less operated protocols as well.

The placement of the queueing function determines the class of packet switch architecture. Several basic approaches for packet queueing in packet switches are known [87]. The two classical architectures are based on input or output queueing. A switch belongs to the input queue class of switches, if its queueing function is performed before the routing function. If it is done after routing, it is attributed to the output queue class of switches [96]. While the

input queueing approach suffers from the head-of-line (HOL) blocking phenomenon limiting the maximum throughput to 58.6% [86], but has the advantage of low complexity and cost, the output queueing approach delivers optimal performance at high implementational complexity of the output queues. They must provide write access to a multiplicity of input ports. This can be achieved by operating a single queue at sufficiently higher speed or by higher paralleled implementation. Both approaches are complex and costly [34]. A reasonable compromise was proposed by [34], that allows output queues to only operate at a fraction of the required speed-up or parallelism. It is a so-called combined input output queued (CIOQ) switch architecture. To avoid packet loss, it employs a flow-control (FC) mechanism between output and input queues. The grand part of the buffer space can economically be implemented at the input, while only a small fraction is required for performance reasons at the output. The authors of [34] point out that the input queues do not necessarily have to be part of the same physical device that realizes the routing function and output queueing.

We adopt this approach in this dissertation and split therefore the SF into a switch adapter (SA) that realizes the input queues and a switch core, or simply a switch that incorporates the routing matrix and the output queues. We consider single stage fabrics only, but like to point out that our solutions shown in this dissertations seem to be very attractive for multistage fabrics.

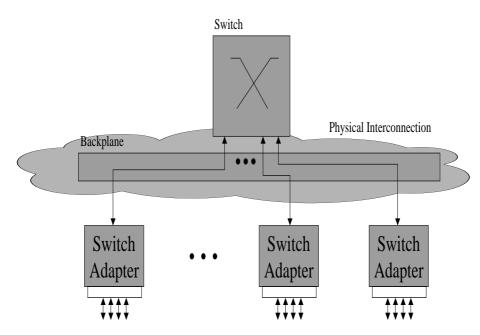

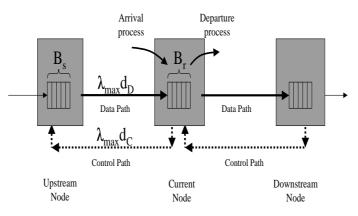

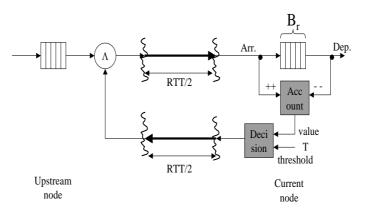

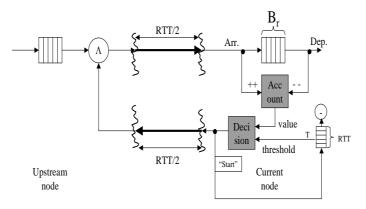

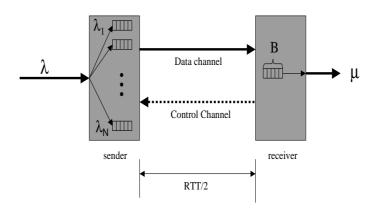

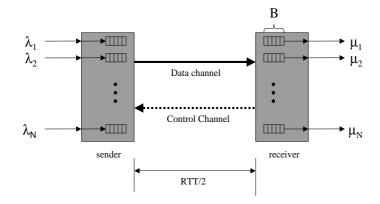

Figure 2.3: Previous Generation of Switch Fabrics

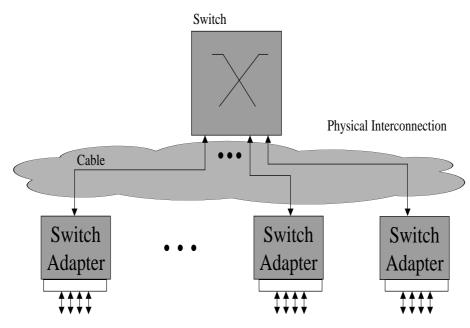

SAs are interconnected to the switch via links that operate a FC mechanism to prevent packet loss as outlined earlier. These links may be realized over a backplane as shown in Fig. 2.3 such that the SF is packaged on a single board or by cables as shown in Fig. 2.4 such that the SF is packaged across multiple racks. While a backplane is more efficient in terms of cost, space and in the round-trip time (RTT) bandwidth product and is therefore the preferred solution, cables offer higher bandwidth per link, which is very important for high-speed switching.

To underline the importance that future VLSI high-speed switching is constrained by 1) limited number of signal I/Os per chip 2) limited number of boards per backplane, we present an example of IBM's current switching family, the IBM PowerPRS [40] in Appendix B.

As a result cables as shown Fig. 2.4 will be employed. However, such "long distance" cables dominate the total SF costs. These cables are about 3-10m in length. Including the data integrity and synchronization processing of the link, RTT times bandwidth product between SA

Figure 2.4: Next Generation of Switch Fabrics

and switch is expected to be in the 10s of packets. This is in contrast to what previous switch design work assumed. For instance [1] [37] [5] [6] [46] consider RTTs of 1, [47] in addition analyzes RTTs of 2. Large RTTs have so far solely been analyzed in the context of point-to-point links between SAs. Thus, while the **inter** SF communication for RTT >> 1 has been treated for instance by in [8] [10], the **intra** SF communication has been thoroughly neglected. In our thesis we will deal with this aspect and assume an RTT times bandwidth product of 64 packets, if not stated otherwise. For brevity, we say RTT=64. Our switch *design point* is specified work-conserving (definition provided in Subsection 4.1.1) for arbitrary input-output pairs using an RTT = 64.

In the following the functionality of the switch adapter and the switch are explained.

#### 2.1.3 Switch Adapter (SA)

The SF interface, the SA, is another queueing point. It is a device that serves several purposes.

- Queueing: It performs input queueing for reasons explained earlier.

- Segmentation/Reassembly: It segments the frames of the NP into packets before and reassembles them again after switching.

- Header Generation: It compiles the routing and QoS information provided by the NP into a format that the switch understands and prepends it as packet header.

Sometimes the functions of the SA are a physical part of the NP, sometimes these functions are realized in separate functional SA units. A separate SA allows to interface to different NP vendors, standards and packet formats and gives hence more flexibility, but typically adds another queueing point. A SA incorporated into the NP gives therefore shorter packet delays through a networking node, but makes the NP even more complex and less flexible. As the combination of input and output queueing and the FC applied inbetween, is the essence of this thesis, we consider the SA as logical entity, which is part of the whole SF. The input queues are often realized as virtual output queueing (VOQ), i.e. queuing at the input per output, to avoid

the HOL blocking phenomenon. Virtual output queueing is a well established way to implement input queueing. It has been adopted in the design of crossbar switches [89], as well as in the design of buffered switches using shared memory [44, 96] and will also be assumed in our work. This approach has been proven to be robust against varying traffic characteristics [38].

The segmentation/reassembly, as well as the header generation are the reason why the switch has to run faster than the targeted data line rate (speed-up). Note, that from this point of view the SA can also be considered a speed-matching entity. The SA may also convert the physical format of a packet, for instance from a serial to a parallel representation to efficiently interconnect to the switch. This depends on the link technology that is used. At the egress the SA again queues the packet to restore a format that is understood by the NP. The SA for one switch input/output port pair typically is one physical entity.

It is assumed that the adapter at the egress of the switch, the output adapter (OA), is always able to absorb all traffic at all times. This assumption is made in order to avoid interference with congestion. One purpose of our work is to find an optimal solution for resolving output contention, as we describe in Chap. 3. We therefore need to exclude occurrences of network congestion which is achieved by this assumption. Therefore, the OA is not relevant to our work. The adapter at the ingress side of the switch, the input adapter (IA), however, does play a major role in our considerations, since it houses the VOQs and the link (data path) scheduler. This is the reason, why we often see only the input aspect of a SA, and refer to it as IA. Therefore, we use the term IA and SA interchangeably. We exclude link technology issues from our work and assume an error-free physical interconnection between IA and switch. This is a reasonable assumption with current link technologies and coding schemes used. IBM's Unlink technology for instance achieves a bit error rate of up to  $10^{-18}$ . For a 1Tb/s system, there would be one single error per roughly 11 days. With an additional Error Correction Code (ECC) for both the payload and the header the link can be considered error free. It makes therefore sense to assume responsibility of guaranteed delivery of packets by higher level protocols, e.g. end-toend protocols that operate between NP-egress and NP-ingress.

#### 2.1.4 Switch

The CIOQ class of switches is represented by two alternative architectures. One architecture is based on a cross-bar employing a centralized scheduler. The other architecture is an outputqueued-switch based architecture. The former is attractive due to its simplicity and low cost in realizing the SF. However it is known not to scale well to larger fabric sizes. This is because it has to find a best match out of a set of  $N^2$  inputs (VOQs) and N outputs (challenges for bipartite graph matching (BGM) algorithm). It is also, because there need to be  $2N + N^2$  interconnection lines for the request and grant operation to and from the input adapters and the switch ports. Moreover, for achieving throughput of close to 100% with this architecture, a speed-up of 2 is required [79]. This speed-up is to be seen in addition to the speed-up necessary for the packet overhead. Therefore, the bandwidth through the routing fabric and the read bandwidth of the input buffers must be doubled. Considering the chip I/O bandwidth bottleneck, this speed-up, the wiring complexity, and the performance of the BGM algorithm are significant implementation challenges which exclude this architecture from our field of exploration.

The latter architecture is often realized with output queues located in a block of shared memory. This approach allows a better utilization of the limited memory space available on the VLSI chips, because the space allocated to a specific output queue varies dynamically with the load. However, mechanisms need to be put in place that avoid one output taking the maximum share thus degrading the performance of other connections. In addition the shared memory must also be protected from running out of storage. These FC mechanisms are costly in terms of packet overhead and hence speed-up and bandwidth.

FC is the mechanism employed within SFs to fulfill the lossless requirement. It means the SF must not drop packets due to overflowing buffers. While some traffic classes of network protocols would allow the loss of packets, for instance, User Datagram Protocol (UDP), or Available Bit Rate (ABR) services in ATM, some of them don't, such as Transmission Control Protocol (TCP), or just allow the abortion of packets with a specific bit in the header being set, as for instance in Variable Bit Rate (VBR) class of traffic in ATM. From statement 2) - the switch to be network protocol independent and it to be able to support all classes of traffic - follows that the switch must not drop packets. This is not a necessary conclusion, since specific drop information might be passed from the NP level down to the switch. The implications of such a drop function don't directly relate to our work and are therefore shortly discussed in Appendix C. The output-queued-switch based CIOQ architectures has three drawbacks.

- 1. It requires multi-port queues that are challenging to implement.

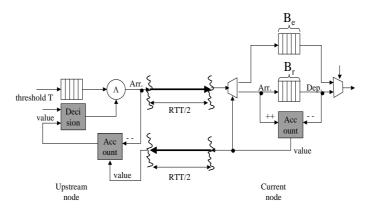

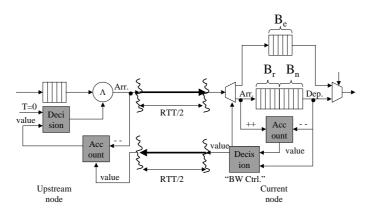

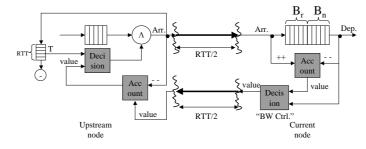

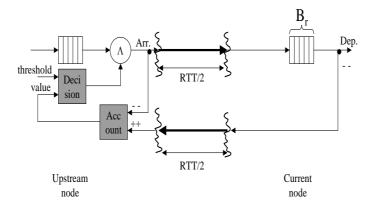

- 2. For performance and economic reasons, these queues are realized within a shared memory, which requires a two layered FC mechanism. One to protect the output-queues and one to protect the memory from overrunning.