Diss. ETH No. 19648

# Modular Performance Analysis of Embedded Real-Time Systems: Improving Modeling Scope and Accuracy

A dissertation submitted to

## ETH ZURICH

for the degree of

Doctor of Sciences

presented by

SIMON PERATHONER Dott. Ing. Inf. Politecnico Milano

> born 12.06.1981 citizen of Italy

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. Dr. h.c. mult. Reinhard Wilhelm, co-examiner

TIK-SCHRIFTENREIHE NR. 127

Simon Perathoner

# Modular Performance Analysis of Embedded Real-Time Systems: Improving Modeling Scope and Accuracy

A dissertation submitted to ETH Zurich for the degree of Doctor of Sciences

Diss. ETH No. 19648

Prof. Dr. Lothar Thiele, examiner Prof. Dr. Dr. h.c. mult. Reinhard Wilhelm, co-examiner

Examination date: April 21, 2011

# Abstract

A fundamental aspect of the design of an embedded system is the prediction of its performance in terms of timing, memory, or energy early in the design process. The objective of this task, typically referred to as systemlevel performance evaluation, is twofold. On one hand, it is instrumental for pre-validating a system design before any resources are invested for the actual implementation and, on the other hand, the performance evaluation is a central driver for the exploration of the design space. For systems with strict performance requirements such as hard real-time systems the performance evaluation needs to be provably correct, that is, it has to cover the worst-case performance scenarios. Furthermore, the evaluation should be fast such that it can be employed for the exploration of large design spaces.

Recent research efforts have led to analytical and modular methods for worst-case performance evaluation at the system level. These methods ensure the correctness of the performance evaluation and are fast even for large-scale systems. However, they suffer from limited modelling scope and analysis accuracy. As a consequence, when applying these methods to complex systems, one often experiences considerable abstraction losses, which lead to overly pessimistic performance results.

This thesis introduces several formal models and methods that refine the modelling capabilities of analytical performance evaluation and prevent abstraction losses. The results build on the existing framework for Modular Performance Analysis (MPA), but apply also to other analytical formalisms. The main contributions of this thesis can be summarized as follows:

- The modelling scope of analytical performance evaluation is extended to systems with cyclic dependencies.

- New models and methods are introduced for handling structured event or data streams in analytical performance evaluation.

- A novel hybrid analysis methodology is presented that combines analytical and state-based system evaluation.

- New design methods for energy-efficient real-time systems are introduced.

# Zusammenfassung

Ein wesentlicher Aspekt der Entwicklung von eingebetteten Systemen ist die Vorhersage deren Leistung bezüglich Zeitverhalten, Speicherbedarf oder Energieverbrauch in frühen Entwurfsphasen. Diese Leistungsbewertung, oft als *System-level Performance Evaluation* bezeichnet, dient zwei Zielen. Zum einen ermöglicht sie die Validierung von Systementwürfen vor der eigentlichen Implementierung des Systems. Zum anderen ist die Leistungsbewertung ein entscheidendes Element der Exploration des Entwurfsraumes. Für Systeme mit strengen Leistungsanforderungen wie zum Beispiel Echtzeitsystemen, muss die Leistungsbewertung nachweisbar korrekt sein, d.h. sie muss Worst-Case Szenarien erfassen. Weiterhin sollte die Leistungsbewertung möglichst schnell sein, damit sie für die Exploration von grossen Entwurfsräumen eingesetzt werden kann.

Die Forschungsbemühungen der letzten Jahre haben analytische, modulare Methoden zur Worst-Case Leistungsbewertung auf Systemebene hervorgebracht. Diese Methoden garantieren die Korrektheit der Leistungsbewertung und sind auch für grosse Systeme schnell. Allerdings zeichnen sich diese Verfahren auch durch einen eingeschränkten Anwendungsbereich und teilweise mangelnder Analysegenauigkeit aus. Aus diesem Grund kommt es bei der Analyse von komplexen Systemen häufig zu erheblichen Abstraktionsverlusten und folglich zu pessimistischen Leistungsbewertungen.

Die vorliegende Arbeit stellt formale Modelle und Methoden vor, die die Ausdruckskraft und Genauigkeit der analytischen Leistungsbewertung wesentlich verbessern. Die Arbeit baut auf den bestehenden Ansatz der *Modular Performance Analysis (MPA)* auf. Die Ergebnisse finden jedoch auch in weiteren analytischen Verfahren Anwendung. Die konkreten Beiträge dieser Arbeit können wie folgt zusammengefasst werden:

- Der Anwendungsbereich der analytischen Leistungsbewertung wird um Systeme mit zyklischen Abhängigkeiten erweitert.

- Modelle und Methoden zur Handhabung von strukturierten Datenströmen werden vorgestellt.

- Ein neuartiges hybrides Analyseverfahren wird eingeführt, welches analytische und zustandsbasierte Leistungsbewertung kombiniert.

- Neue Entwicklungsmethoden zum Entwurf von energieeffizienten Echtzeitsystemen werden vorgeschlagen.

# Acknowledgement

First and foremost I would like to thank my advisor Prof. Dr. Lothar Thiele for his constant support during my research activity. Thank you for many fruitful discussions, and for all the valuable inputs that shaped this thesis. I would also like to thank Prof. Dr. Reinhard Wilhelm for co-examining this work.

Furthermore, I would like to express my sincere gratitude to all the collaborators that directly or indirectly contributed to the results of this thesis. In particular, I wish to thank Prof. Dr. Bengt Jonsson, Prof. Dr. Jian-Jia Chen, and Dr. Kai Lampka for sharing ideas and co-authoring papers.

I also thank all my current and former colleagues at the Computer Engineering group for their company and for lots of interesting discussions.

Finally, my warmest thanks go to my girlfriend Kathrin, my parents, and my brother for their constant love and support.

The work presented in this thesis was supported by the Swiss National Science Foundation (SNF) under grant number 200020-116594 and by the European Union project COMBEST under grant number 215543. This support is gratefully acknowledged.

# Contents

| Ał | Abstract                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                    |  |  |  |  |  |  |  |

|----|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Zu | Zusammenfassung iii                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Ac | Acknowledgement                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 1  | 1.1<br>1.2<br>1.3                                         | oductionEmbedded Real-Time SystemsSources of ComplexitySystem-Level Performance Evaluation1.3.1Role in the Design Flow1.3.2Requirements1.3.3Approaches                                                                                                                                                                                                                                                                                                                                                                                                    | 1<br>1<br>2<br>4<br>5<br>6<br>7                                                                                                                                                    |  |  |  |  |  |  |  |

|    | 1.4                                                       | Thesis Overview and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 2  | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | nal Methods for Performance Evaluation         Overview of related work         Modular Performance Analysis         2.2.1       A general performance model         2.2.2       Performance characterization in the time domain         2.2.3       Real-Time Calculus         Evaluation and Comparison of Abstractions for Performance Verification         2.3.1       Motivation and Challenges         2.3.2       Comparison Methodology         2.3.3       Benchmark Systems         2.3.4       Analysis Results         2.3.5       Discussion | <ul> <li>13</li> <li>14</li> <li>19</li> <li>20</li> <li>22</li> <li>27</li> <li>42</li> <li>42</li> <li>43</li> <li>44</li> <li>47</li> <li>56</li> <li>58</li> <li>61</li> </ul> |  |  |  |  |  |  |  |

| 3  | Cycl<br>3.1<br>3.2<br>3.3                                 | lic DependenciesIntroductionMotivational exampleFixpoint Computations on Streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>61</b><br>62<br>63<br>65                                                                                                                                                        |  |  |  |  |  |  |  |

|   |      | 3.3.1 Operational Model                         | 65  |

|---|------|-------------------------------------------------|-----|

|   |      | 3.3.2 Correctness and Convergence               | 70  |

|   | 3.4  | Fixpoint Computations in MPA                    | 74  |

|   |      | 3.4.1 Verification of Assumptions               | 74  |

|   |      | 3.4.2 Obtaining an Initial Characterization     | 77  |

|   |      | 3.4.3 Summary of the Method                     | 77  |

|   | 3.5  | Experiments                                     | 78  |

|   | 3.6  | Related Work                                    | 81  |

|   | 3.7  | Summary                                         | 83  |

| 4 | Stru | ictured Event Streams                           | 85  |

|   | 4.1  | Introduction                                    | 85  |

|   |      | 4.1.1 Motivational example                      | 86  |

|   |      | 4.1.2 Terminology                               | 88  |

|   |      | 4.1.3 Organization                              | 89  |

|   | 4.2  | FIFO Scheduling                                 | 89  |

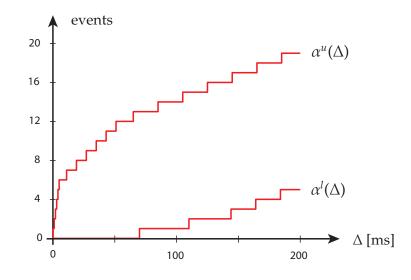

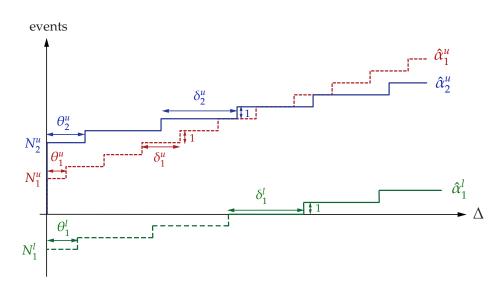

|   | 4.3  | Event Count Curves                              | 90  |

|   |      | 4.3.1 Definitions                               | 91  |

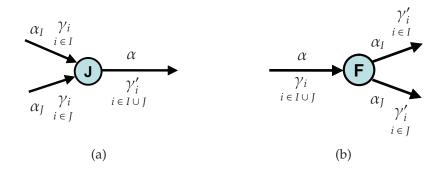

|   |      | 4.3.2 Join and Fork of Simple Event Streams     | 93  |

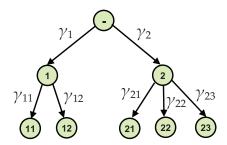

|   |      | 4.3.3 Hierarchical application of ECCs          | 95  |

|   |      | 4.3.4 Join and Fork of Structured Event Streams | 96  |

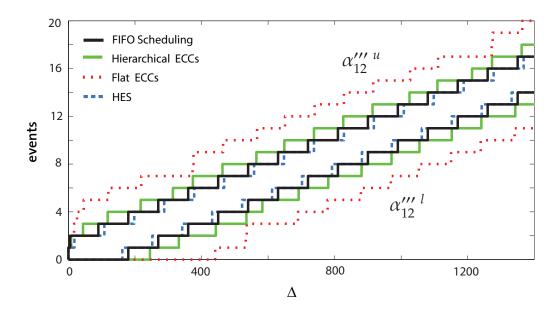

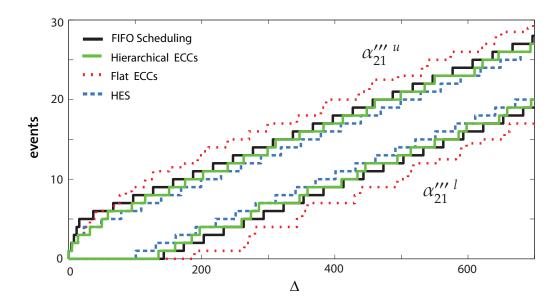

|   |      | 4.3.5 Experimental Evaluation                   | 99  |

|   | 4.4  |                                                 | 101 |

|   |      | 4.4.1 General System Description                | 101 |

|   |      |                                                 | 102 |

|   |      | 4.4.3 Models and Analysis                       | 103 |

|   |      |                                                 | 104 |

|   | 4.5  | Related work                                    | 107 |

|   | 4.6  | Summary                                         | 108 |

| 5 | Hyb  | orid Performance Verification                   | 111 |

|   | 5.1  | Introduction                                    | 112 |

|   |      | 5.1.1 Organization                              | 113 |

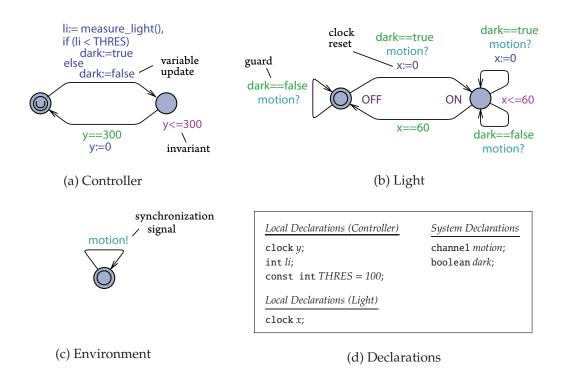

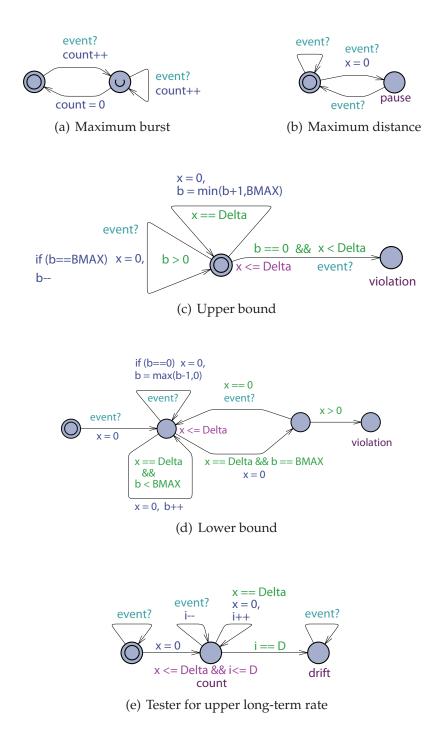

|   | 5.2  | Timed Automata                                  | 113 |

|   | 5.3  | General Approach and Requirements               | 116 |

|   | 5.4  |                                                 | 118 |

|   |      | 5.4.1 Linear Pattern                            | 119 |

|   |      | 5.4.2 Concave/Convex Pattern                    | 122 |

|   |      |                                                 | 129 |

|   |      |                                                 | 131 |

|   | 5.5  | Ŭ I J                                           | 132 |

|   |      |                                                 | 133 |

|   |      | 5.5.2 Algorithm                                 | 136 |

|                      |      | 5.5.3 Correctness                         | 140 |  |  |  |  |  |  |

|----------------------|------|-------------------------------------------|-----|--|--|--|--|--|--|

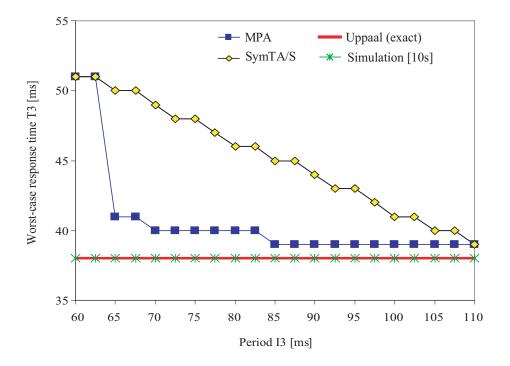

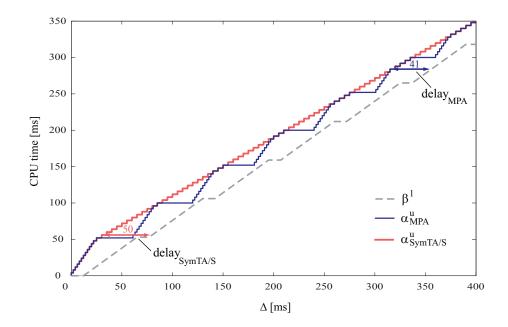

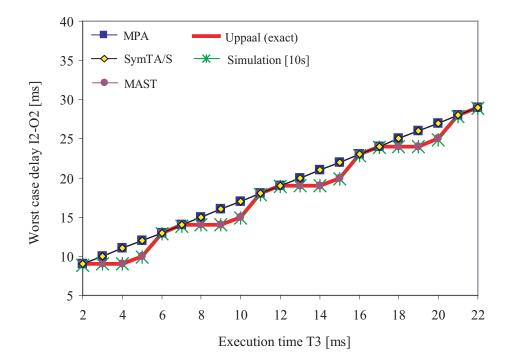

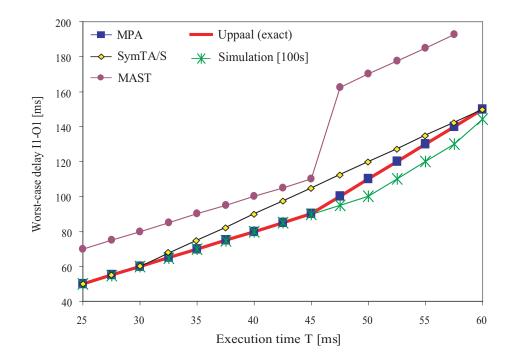

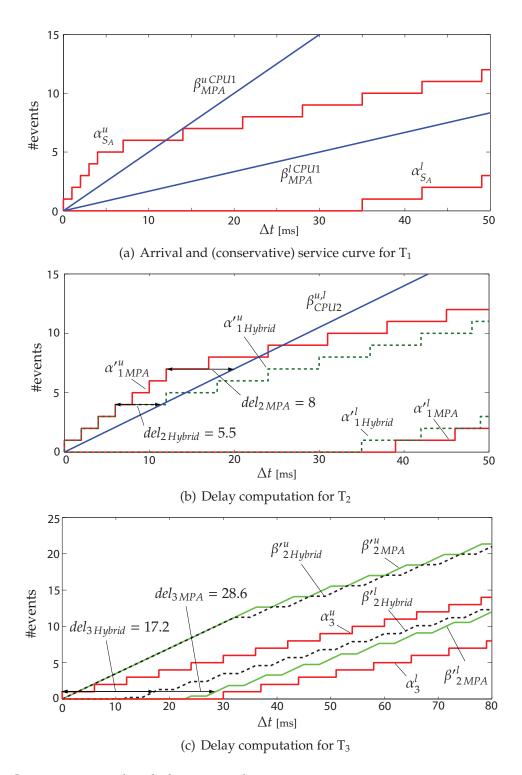

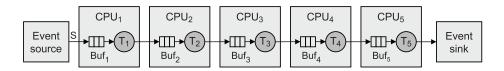

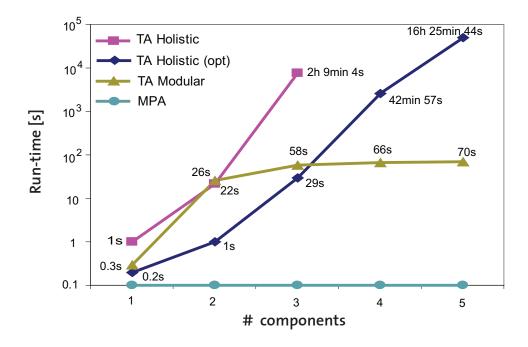

|                      | 5.6  | Experimental Evaluation                   | 140 |  |  |  |  |  |  |

|                      |      | 5.6.1 Case Study                          | 141 |  |  |  |  |  |  |

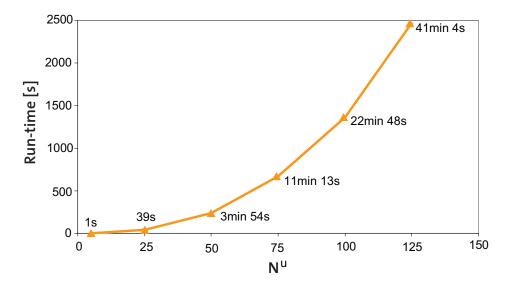

|                      |      | 5.6.2 Scalability of the Approach         | 145 |  |  |  |  |  |  |

|                      |      | 5.6.3 Approximation Errors                | 150 |  |  |  |  |  |  |

|                      | 5.7  | Related work                              | 153 |  |  |  |  |  |  |

|                      | 5.8  | Summary                                   | 155 |  |  |  |  |  |  |

| 6                    | Ene  | rgy-Efficient System Design with MPA      | 157 |  |  |  |  |  |  |

|                      | 6.1  | Introduction                              | 158 |  |  |  |  |  |  |

|                      |      | 6.1.1 Organization                        | 159 |  |  |  |  |  |  |

|                      | 6.2  | Dynamic Voltage Scaling                   | 160 |  |  |  |  |  |  |

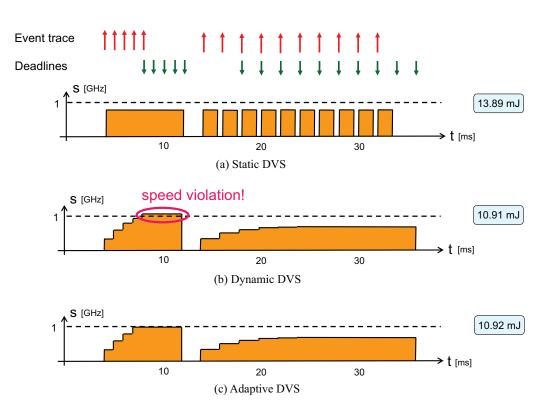

|                      |      | 6.2.1 Offline DVS scheduling              | 161 |  |  |  |  |  |  |

|                      |      | 6.2.2 Online DVS scheduling               | 161 |  |  |  |  |  |  |

|                      | 6.3  | Design of Offline DVS Systems with MPA    | 163 |  |  |  |  |  |  |

|                      |      | 6.3.1 Models and Problem Definition       | 164 |  |  |  |  |  |  |

|                      |      | 6.3.2 Proposed Algorithms                 | 168 |  |  |  |  |  |  |

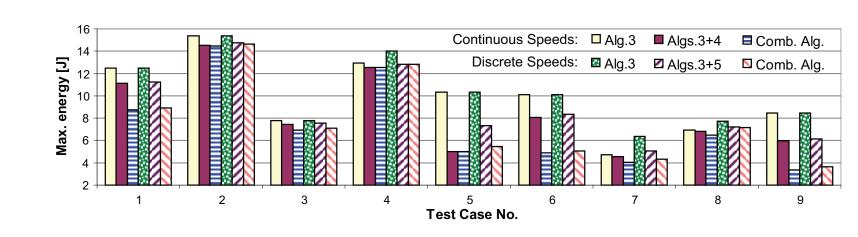

|                      |      | 6.3.3 Experimental Evaluation             | 178 |  |  |  |  |  |  |

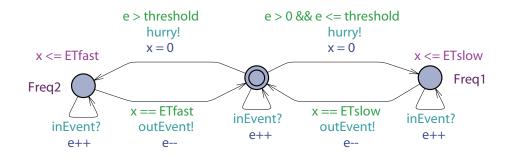

|                      | 6.4  | Design of Online DVS Systems with TA      | 182 |  |  |  |  |  |  |

|                      |      | 6.4.1 System Model and Problem Definition | 183 |  |  |  |  |  |  |

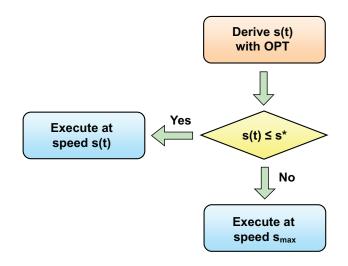

|                      |      | 6.4.2 Adaptive Scheduling Scheme          | 183 |  |  |  |  |  |  |

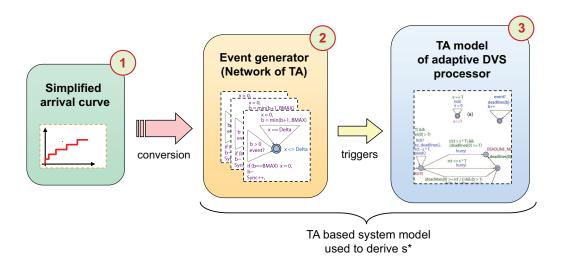

|                      |      | 6.4.3 Parametrization and Verification    | 186 |  |  |  |  |  |  |

|                      |      | 6.4.4 Experimental Evaluation             | 192 |  |  |  |  |  |  |

|                      | 6.5  | Related Work                              | 194 |  |  |  |  |  |  |

|                      | 6.6  | Summary                                   | 196 |  |  |  |  |  |  |

| 7                    | Con  | clusions                                  | 199 |  |  |  |  |  |  |

|                      | 7.1  | Main Results                              | 199 |  |  |  |  |  |  |

|                      | 7.2  | Outlook                                   | 200 |  |  |  |  |  |  |

| Bibliography         |      |                                           |     |  |  |  |  |  |  |

| A                    | Acro | onyms                                     | 217 |  |  |  |  |  |  |

| List of Publications |      |                                           |     |  |  |  |  |  |  |

|                      |      |                                           |     |  |  |  |  |  |  |

| Curriculum Vitae     |      |                                           |     |  |  |  |  |  |  |

1

# Introduction

This thesis presents a set of novel formal methods for the performance evaluation of distributed embedded systems. It builds on an existing analytical framework for modular performance analysis, and aims at improving its modeling capabilities as well as the quality of the achievable analysis results. In this work we primarily consider real-time systems and, hence, focus on techniques for faithful timing analysis of systems. Existing analytical approaches for performance analysis are restricted to specific system models and performance metrics, and deliver only pessimistic performance guarantees for many real systems. The goal of our work is to extend the applicability of formal performance analysis methods by alleviating these problems.

The Introduction is structured as follows: In Section 1.1 we describe the main features of embedded real-time systems. The principal characteristics that complicate the design and the analysis of such systems are summarized in Section 1.2. Section 1.3 introduces the reader to systemlevel performance evaluation, describes its role in the design flow, and identifies its principal requirements. Finally, in Section 1.4 we give an overview of the thesis contents, and summarize our contributions.

# 1.1 Embedded Real-Time Systems

Embedded systems are computer systems that are dedicated to particular applications and are part of a larger device, often including electrical or mechanical parts. Examples of embedded systems are the hardware/software systems that control cars, airplanes, medical equipment, industrial robots, telecommunication devices, appliances, or consumer electronics. Nowadays, embedded processors account for by far the largest share of produced CPUs. This is not surprising if one considers, for instance, the rapidly increasing market for mobile electronic devices.

Embedded systems have several characteristics that distinguish them from general purpose computer systems. First of all, they are tightly coupled to the physical system they are embedded in, meaning that they continuously interact with it and have to meet constraints imposed by it. Note that in this aspect, there is a close relation between control systems and embedded systems: from a broad perspective, basically every computer-based controller in a control loop can be seen as an embedded system.

Another characteristic of embedded systems is that they are usually not reprogrammable by the end user of the device that embodies them. They are designed to perform just a few dedicated tasks that are known at design time. Knowledge about the particular system environment is often exploited for the design of optimized hardware/software solutions.

Moreover, in most of the cases embedded systems have to meet particular requirements in terms of energy, size, weight or cost. In many application domains, they also have to be fully predictable and highly dependable, as a malfunction or breakdown of the device they control is not acceptable.

A particular class of embedded systems are real-time systems. These are systems for which the execution has to meet timing constraints. For instance, in many cases an embedded system has to react to a stimulus or event emitted by the environment within a specified amount of time, also denoted as deadline. Note that real-time processing does not necessarily mean 'fast' processing, but is a synonym for 'timely' or 'predictable' execution. Real-time systems for which a deadline violation cannot be tolerated are often denoted as *hard*.

Finally, we would like to note that recently many authors prefer the denomination *cyber-physical system* to *embedded system*. In particular, the expression *cyber-physical system* is often used to refer to networks of individual components which interact with their physical environment. Within the scope of this thesis, we do, however, not distinguish the two terms. For the sake of consistency, we will stick to the classical denomination of *embedded systems*.

## **1.2** Sources of Complexity

In many cases, modern embedded computer architectures are highly complex and consequently difficult to design and analyze. In the following we identify different factors that contribute to the complexity of embedded hardware/software systems.

#### • Distributed Architectures

Requirements of the controlled device such as scalability, fault tolerance or parallel completion of different (real-time) tasks very often lead to the design of distributed embedded systems. Furthermore, also the constraints imposed by the physical environment often enforce distributed solutions. A distributed system consists of a set of processing elements that communicate over some network. The distribution of the components considerably complicates the design and the analysis of a system. For instance, communication delays on shared busses are typically not negligible, and need to be considered in the timing analysis. Therefore, the analysis requires a holistic approach that considers both computation and communication in a distributed system.

#### • Heterogeneous Components

Another obstacle for the design and analysis of embedded systems is the fact that they often consist of heterogeneous components. The irregularity of the components very often derives from differing functionalities, or from particular characteristics of the local environments. For example, it is not unusual to find heterogeneous processing elements such as DSPs, microcontrollers, and (multicore) CPUs in one and the same device. Similarly, the communication networks are often composed by multiple heterogeneous sub-networks.

#### • Multitasking

Frequently, the individual processing components of an embedded system execute multiple concurrent tasks. These processors implement a scheduling policy that determines which task is to be executed at which time. There are a variety of static and dynamic, preemptive and non-preemptive (real-time) scheduling policies. Depending on the particular scheduling policy and the activation pattern of the tasks, it is often not trivial to bound the timing interference among concurrent tasks.

#### • Shared Resources

Not only processors but also several other hardware resources are subject to contention in an embedded system. Examples are memories, communication channels, and I/O devices. Often the access to shared resources has to occur in a mutually exclusive way. Hence, while a task is granted access to a common resource, other tasks on other processing elements might experience blocking, that is, they might be forced to wait before they gain access to the resource. Predicting the worst-case interference of tasks on each other is often hard, as the individual processing components operate in parallel, and usually take independent resource access decisions.

Note that all the concepts mentioned above can apply at different abstraction levels in the system architecture. For instance, the concept of networked components may apply to physically separated processors, but as well to Multiprocessor Systems-on-Chip (MPSoC). Similarly, contention for shared resources such as memories or busses can be observed on-chip as well as on a system-wide scale.

## **1.3** System-Level Performance Evaluation

Given the stringent requirements of many application domains, it becomes clear that evaluating the performance of an embedded system is highly important in the design process. In particular, not only the functional correctness of the computations performed by a system is relevant, but also the performance of the system in terms of e.g. response times or energy consumption needs to be ensured. Note that for embedded systems the distinction between functional (behavioural) and non-functional (performance) requirements is blurry. For instance, in a real-time system, a correct result arriving later (or even earlier) than specified can lead to a system failure. Similarly, in a battery operated mobile device, excessive energy consumption can compromise the required operation time of the device and hence its functionality.

Different performance aspects can be relevant for an embedded hardware/software system. The most common ones are:

- Timing properties (e.g. response times, end-to-end latencies)

- Memory requirements (e.g. buffer sizes)

- Energy consumption

The quantification of the system behaviour with respect to one or several of such metrics is generally referred to as performance evaluation or performance analysis.

The performance evaluation of embedded systems is essentially different from the performance evaluation of general-purpose computers. In particular, due to the restrictive requirements of many application domains (e.g. hard real-time constraints), the designers of embedded systems often can not rely on average or stochastic performance characterizations of a system. Instead, safe bounds for the best-case and worst-case performance of a system are required. This thesis focuses on high-level techniques for reliable worst-case (best-case) performance evaluation.

#### **1.3.1** Role in the Design Flow

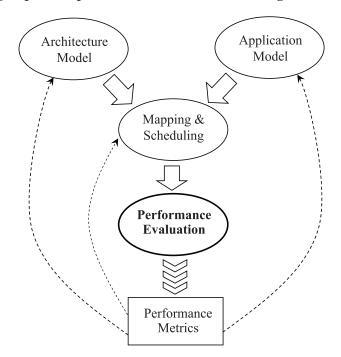

Performance evaluation at an early design stage, mainly at the system level, is important for taking fundamental design decisions before resources are invested in detailed implementations. In particular, the role of performance evaluation in the design flow is twofold: On one hand, it is employed as a validation or even certification instrument after the system-level design is completed. On the other hand, it is used as a driver for the design space exploration, as illustrated in Figure 1.

Fig. 1: Typical design space exploration cycle (Y-model)

The figure shows the so-called Y-model, which is largely employed for design space exploration in hardware/software co-design. It represents an iterative design flow with successive refinements. The design starts from modelling the hardware platform (architecture) and the software structure (application) separately. The next design step consist in deciding the assignment of software tasks to processing resources (mapping) and determining the precedence relations among tasks (scheduling). At this point a complete system model is configured, and its performance can be ascertained by an appropriate performance evaluation method. After the analysis, the performance results are used to derive the next exploration step in the design space. In particular, based on the obtained performance metrics, the design choices in terms of architecture, application, as well as mapping and scheduling are revised.

It becomes apparent that the system-level performance evaluation plays a central role in the described design methodology. It guides the designer to efficient solutions in a potentially huge design space, and thus supports him in taking crucial design decisions early in the design flow.

Finally, we would like to note that, in general, not only the mentioned performance metrics, but also other design characteristics such as software code size, chip area, cost, etc. are considered in the exploration of the design space. In the present thesis we will, however, focus solely on the performance metrics listed above.

#### 1.3.2 Requirements

There are several requirements that an ideal method for system-level performance evaluation should fulfil. In the following, we specify a list of requirements for performance evaluation methods adapted from [TW].

• Modelling Scope

The modelling capabilities of the evaluation technique should be rich, meaning that the method should cover a broad domain of systems. In particular, the evaluation technique should be able to precisely model a large variety of processing and communication components, scheduling policies, and arbitration protocols.

• Correctness

The results of the performance evaluation should be correct in the sense that the determined performance bounds should be inviolable by the modelled system. In other words, every behaviour that the system may exhibit should be contained in the performance bounds resulting from the analysis. Note that correct performance evaluation methods are often also denoted as *conservative* or *exhaustive* methods.

#### • Accuracy

The result of the performance evaluation should be accurate, meaning that it should be as close as possible to the actual worst-case or best-case performance of the system. In other words, pessimistic analysis results should be avoided.

#### • Fast Evaluation

The run-times of the evaluation tools should be short. In particular, this is essential if the performance evaluation is used in a design space exploration loop as described in Section 1.3.1.

#### • Scalability

A method for performance evaluation should not just be applicable to small example systems, but should scale to large, industrial embedded systems.

#### • Modularity

The evaluation method should be modular in the sense that the designer can model and analyze a system by composing several smaller, ideally pre-build system modules. The modularity is a key requirement for an analysis method, as it enables the fast reconfiguration and extension of existing models, as well as the incremental design of systems.

Note that some of the listed requirements might be conflicting. For instance, a more accurate technique for performance evaluation often comes at the price of a slower analysis. Finally, we would like to point out that the relevance of the individual requirements highly depends on the particular application domain and design method.

#### 1.3.3 Approaches

In this section we give a rough overview of approaches to system-level performance evaluation of embedded systems, and describe the major pros and cons of each methodology. For a detailed discussion of particular techniques, we refer the reader to Chapter 2.

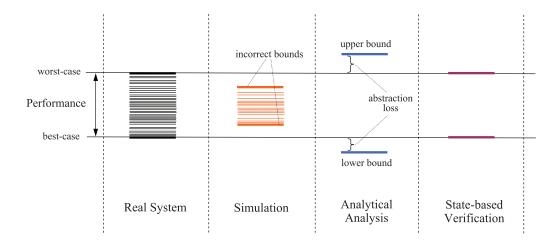

Most contemporary methods for performance evaluation fall in one of the three main classes reported in Table 1. The first class is formed by empirical evaluation techniques such as simulation, testing or measurements (on prototypes or real systems). Simulation-based methods are often characterized by rich modelling capabilities, meaning that they can represent a broad domain of systems in large detail. However, as common for empirical methods, they are typically not exhaustive. In particular, every simulation run is of finite length and, hence, simulations can reproduce only a finite set of system behaviours. This implies that, in general, corner cases might be missed by a simulation. In terms of performance evaluation, this means that simulation-based methods cannot be employed to derive hard performance guarantees for a system, as the delivered worst-case (best-case) performance bounds might be incorrect. This is represented in Figure 2, which illustrates the typical distribution

| Empirical Methods<br>(Simulation, Testing,<br>Measurements)                             | Testing, (Mathematical System |                                                                      | State-based<br>Verification Methods<br>(Model Checking)                                                      |  |

|-----------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>+ Large modelling scope</li> <li>- Not exhaustive</li> <li>(-) Slow</li> </ul> | +<br>+<br>-                   | Exhaustive<br>Fast<br>Limited modelling<br>scope<br>Limited accuracy | <ul> <li>+ Exhaustive</li> <li>+ Accurate (exact)</li> <li>- Slow<br/>(State space<br/>explosion)</li> </ul> |  |

**Tab. 1:** Methodologies for performance evaluation

of bounds obtained with different techniques for a generic performance metric.

Another category of methods for performance evaluation are analytical techniques. They are based on mathematical abstractions of system behaviours and provide closed-form expressions to quantify the performance of a system. Analytical approaches are often considerably faster than simulation-based methods, but more importantly, they are provably correct. For this reason, they can be used to safely bound the performance of a system. However, analytical methods for performance evaluation often suffer from limited modelling scope because they rely on a restricted set of component models and are limited to the analysis of specific performance metrics. If the system to be analyzed does not closely fit this set of models, it might still be possible to find a conservative approximation of the system behaviour, but at the price of reduced analysis accuracy. A second issue is that the mathematical abstractions employed by these methods might themselves not be tight. In other words, even if a system matches the modelling capabilities of an analysis method, the performance bounds derived for it might still be overly conservative. These two kinds of accuracy problems are commonly referred to as abstraction *loss* of an analytical performance evaluation method. Figure 2 shows the qualitative impact of the abstraction loss on the performance bounds.

The third family of approaches for performance evaluation are the state-based verification methods. They mostly rely on techniques from the domain of model checking. In particular, they offer some formalism for specifying a model of a system, and employ a model checker to automatically verify whether the model meets a given (performance) property, typically specified as formula in (temporal) logic. Compared to analytical approaches for performance evaluation, these methods have a

Fig. 2: Typical performance bounds obtained with different evaluation methods (adapted from [Wan06])

much larger modelling scope, as they can typically model arbitrary statedependent behaviour of system components. Moreover, they can guarantee exact performance results, meaning that the results are not only correct but also perfectly accurate (cf. Figure 2). Unfortunately, state-based verification methods suffer from state-space explosion, a problem that severely inhibits their practical application. More specifically, the state-transition system that is derived from a high-level model grows very quickly with the size of a model. The consequence is that for large-scale models, the verification tools often exhibit prohibitively long verification times and/or large memory requirements.

Finally, we would like to mention that not all existing techniques for performance evaluation fit in one of the above classes. For instance, there are also several stochastic approaches which we do not consider in the scope of this thesis.

## **1.4** Thesis Overview and Contributions

This thesis focuses on analytical, modular methods for performance evaluation of distributed embedded systems. Its principal aim is to fight the abstraction loss of these methods. In particular, our work improves the application scope and the accuracy of a specific formalism for performance evaluation, the framework for *Modular Performance Analysis* (MPA) [TCN00, WTVL06]. Most of the abstractions and concepts introduced in this thesis are, however, also applicable to other analytical formalisms. In the following we summarize the contents and the individual contributions of the five main chapters of the thesis.

#### **Chapter 2: Formal Methods for Performance Evaluation**

In Chapter 2, we provide a survey and general discussion of existing formal methods for performance evaluation of distributed real-time systems. The survey is followed by an introduction of the framework for Modular Performance Analysis, which forms the basis for the theoretical contributions of this thesis.

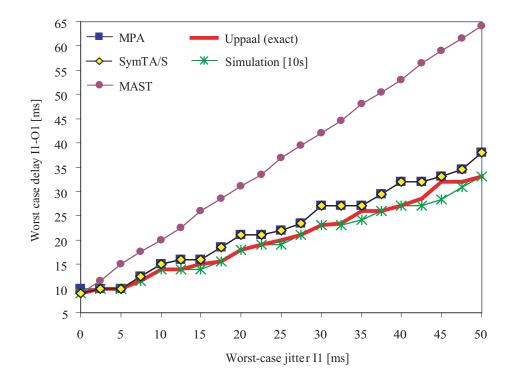

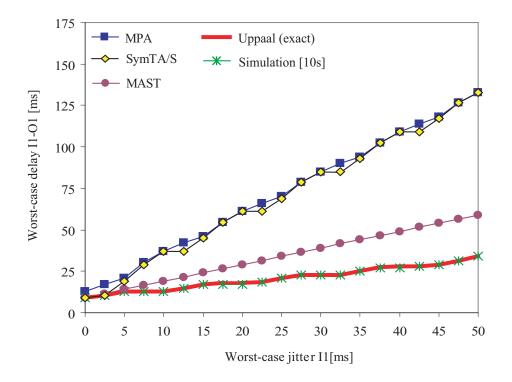

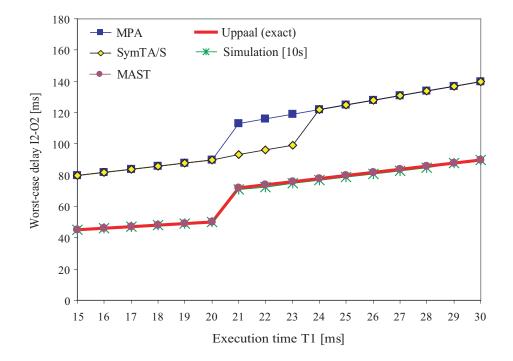

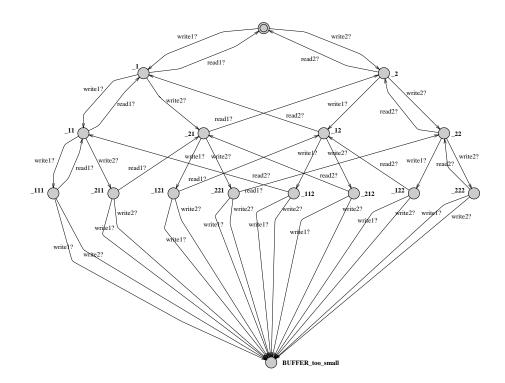

The second part of Chapter 2 is devoted to the quantitative assessment of different methods for performance evaluation. In particular, we reproduce and extend the results presented in [Per06], where we investigated the influence of different abstractions on the accuracy of the performance evaluation. The assessment is based on a set of benchmark systems that are used to quantify the accuracy and the runtimes of various evaluation tools. The comparison points out several pitfalls for analytical performance evaluation which stimulated most of the research presented in this thesis.

#### **Chapter 3: Cyclic Dependencies**

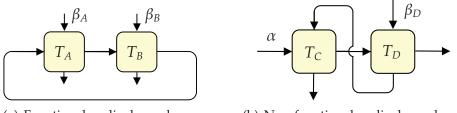

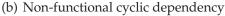

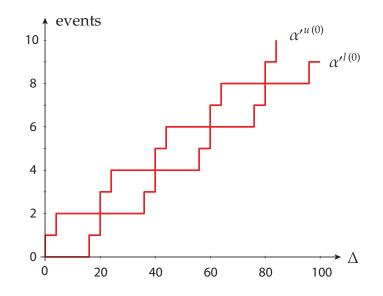

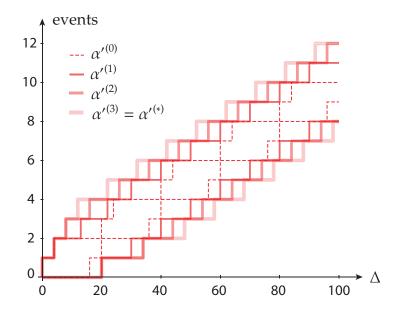

In Chapter 3 we approach a major obstacle for modular, analytical techniques for performance evaluation, namely the analysis of models with cyclically dependent components. In particular, we extend the modelling scope of MPA to systems with non-functional cyclic dependencies by showing that such systems can be safely analyzed by means of fixpoint iteration. While this is a natural approach successfully used in many other domains, in the context of MPA (and similar methods), it was unclear to what extent the resulting fixpoints are faithful to the performance of the modelled systems. Moreover, it was not clear how to best choose starting points for fixpoint iterations in MPA. We solve these problems by providing the theoretical foundations for fixpoint iterations in MPA. More specifically, Chapter 3 contains the following contributions:

- We develop a general operational semantics underlying the MPA framework.

- On this basis, we prove central properties about the faithfulness of fixpoint computations in MPA.

## **Chapter 4: Structured Event Streams**

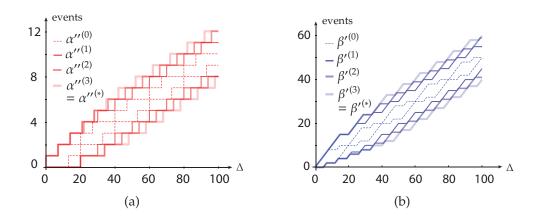

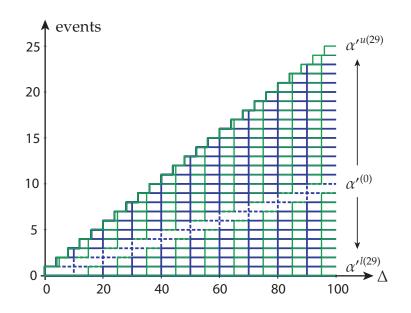

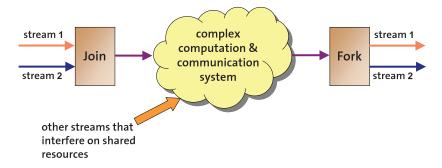

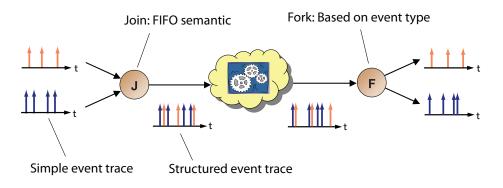

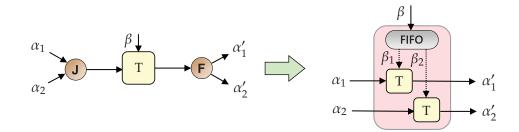

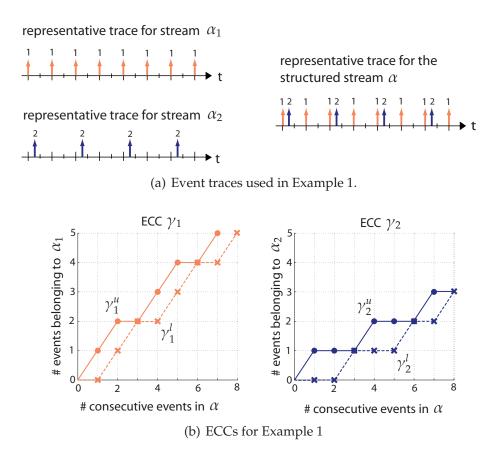

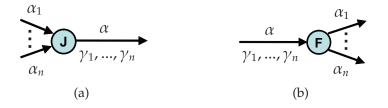

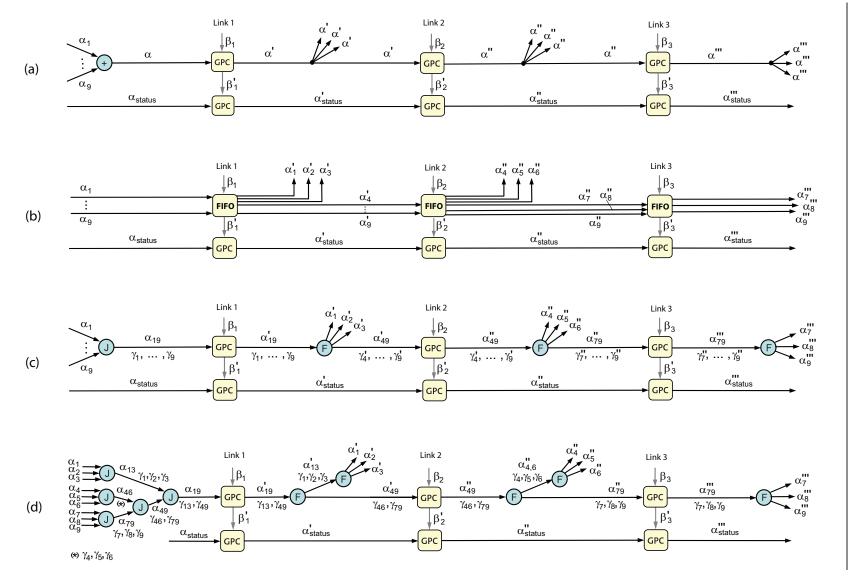

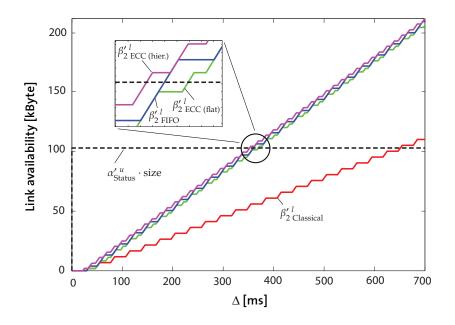

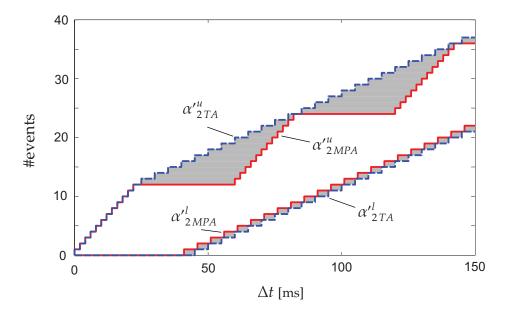

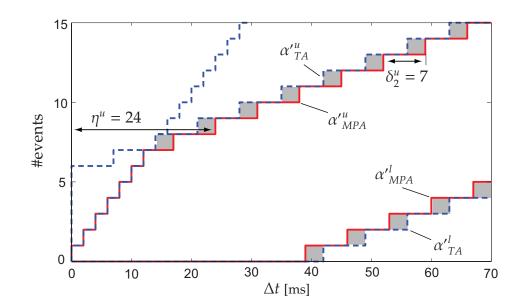

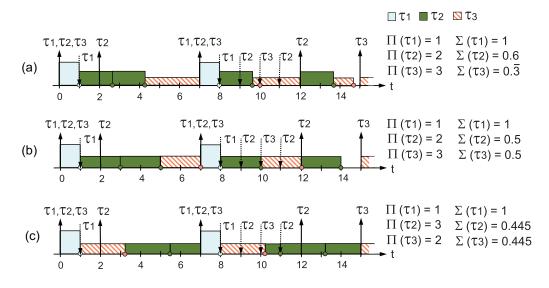

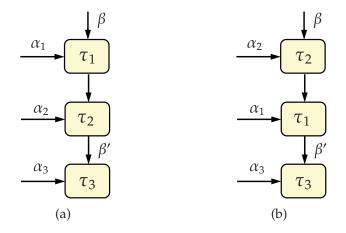

In Chapter 4 we introduce models and methods that considerably reduce the abstraction loss of MPA by extending its modelling scope to a highly relevant design pattern: the merging and splitting of event streams in stream-based distributed embedded systems, based on event type information. This pattern applies, for instance, if data from different streams is first combined, transmitted over a shared communication channel, and then separated again. Our model is based on a novel characterization of structured event streams which seamlessly integrates in the existing framework for Modular Performance Analysis. In particular, the contributions of Chapter 4 can be summarized as follows:

- We propose a new approach for analyzing the processing and communication of merged event streams in distributed embedded systems. The approach is based on Event Count Curves, a model for representing structures in event streams.

- We show how the FIFO component introduced in Chapter 2 can be used to handle structured event streams.

- We evaluate the two proposed models and compare their performance with existing techniques from related work. We also apply the proposed techniques to a realistic application scenario.

## **Chapter 5: Hybrid Performance Evaluation**

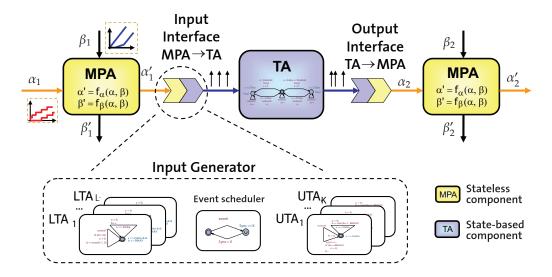

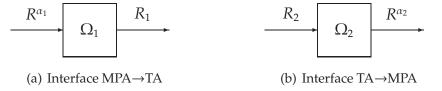

In Chapter 5 we introduce a novel hybrid methodology for the performance evaluation of distributed real-time systems. The approach combines analytical and state-based performance analysis. In the resulting hybrid and modular framework, system components can be modelled by either MPA or Timed Automata, a state-based formalism for the verification of real-time systems. In this way, we can benefit from the advantages of both domains: On one hand, we obtain considerably better modelling capabilities and analysis accuracy compared to a pure MPA representation of a system. On the other hand, we can avoid state space explosion by constraining the verification scope to the level of single system components. The interfaces among components in the hybrid analysis methodology rely on conversions of arrival curves (the event stream model adopted by MPA) to networks of co-operating Timed Automata and vice versa. To summarise, the following contributions are contained in Chapter 5:

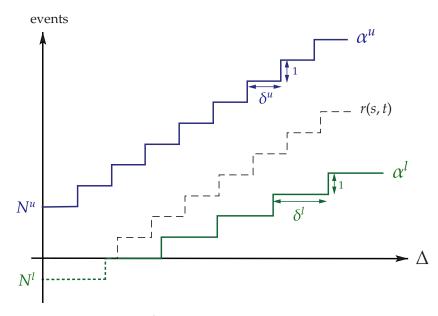

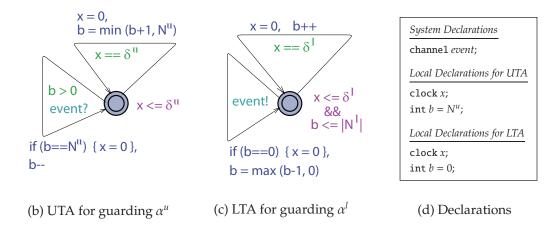

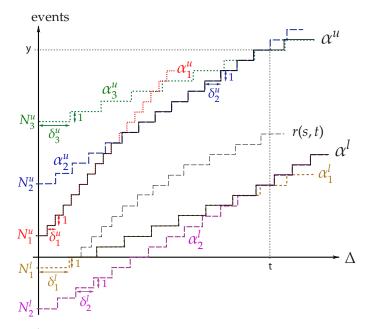

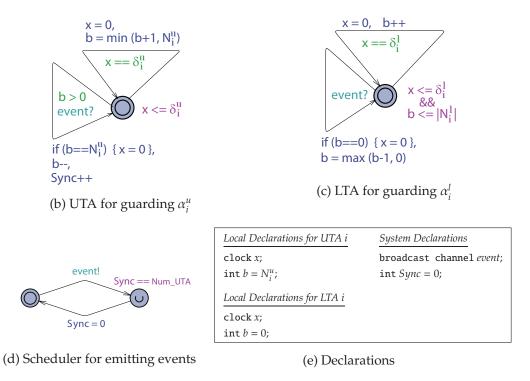

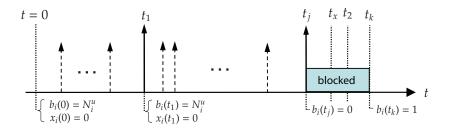

• We describe a pattern allowing us to convert arrival curves (or other common event stream models) to networks of co-operating Timed Automata, and vice versa.

- We prove the correctness and tightness of the proposed transformations, i.e., the Timed Automata generate all event traces and solely the event traces complying with the arrival curves.

- We evaluate the accuracy and scalability of the proposed methodology.

### Chapter 6: MPA for Energy-Efficient System Design

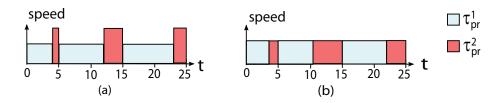

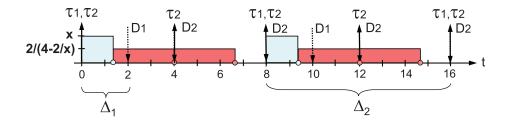

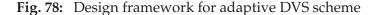

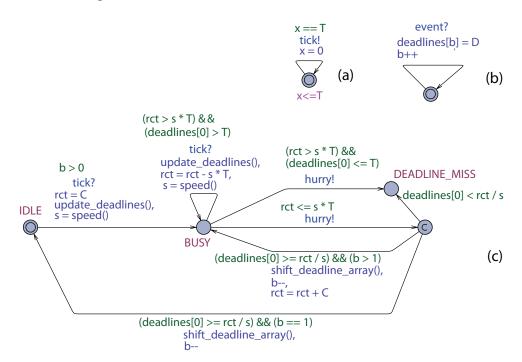

While the Chapters 2-5 focus mainly on the analysis of timing characteristics of embedded systems, in Chapter 6 we approach the analysis of another very important performance aspect: the worst-case energy consumption of embedded systems. More specifically, we look at the combined observance of real-time and energy constraints. We show how Dynamic Voltage Scaling (DVS), a common technique for the reduction of the energy consumption of a processor, can be seamlessly incorporated in the framework of MPA, extending its application scope to the design of energy-efficient real-time systems. In particular, we consider two different design problems: (1) The energy-efficient *static* assignment of execution speeds and priorities to a set of event streams. (2) The energyefficient *dynamic* adjustment of the execution speed to process a single event stream. The first method is based on the original MPA framework for performance evaluation, whereas the second one builds on top of the hybrid evaluation framework introduced in Chapter 5. Specifically, the following contributions can be identified for Chapter 6:

- We devise algorithms to derive energy-efficient static priority and speed assignments to multiple real-time tasks with arbitrary release patterns.

- We present an adaptive scheme that dynamically adjusts the execution speed to process an arbitrary event stream. We show that the scheme guarantees timing and speed constraints, and at the same time ensures energy-efficient processing.

- We demonstrate the effectiveness of the presented methods by means of experimental test cases.

# 2

# Formal Methods for Performance Evaluation

The performance evaluation is a central step in the design process of an embedded system. Testing and measurements on prototypes or real systems are largely applied to validate the performance of system implementations. However, a major drawback of these methods is that they cannot be applied at early design stages, that is, when implementation details of the system are not yet defined. Model-based techniques are an alternative way to evaluate crucial (performance) characteristics of a system early in the design flow. The principle of model-based engineering is to construct simplified models of a system in order to reason about its properties. The major challenge lies in constructing models which are abstract enough to cope with missing implementation details, but nevertheless allow us to draw correct conclusions about the system. There is a large body of work on model-based design and verification of embedded systems. In the present chapter we first provide an overview of existing formalisms, with a focus on abstraction methods for system-level performance evaluation (Section 2.1). In Section 2.2 we detail the theoretical foundations of the Modular Performance Analysis (MPA), the formalism used as basis for the contributions of this thesis. Finally, in Section 2.3 we reproduce and extend our work of [Per06], that quantitatively compares several approaches to performance evaluation. The comparison identifies various pitfalls for analytical performance evaluation, and forms the basis for the extensions and improvements presented in the following chapters.

## 2.1 Overview of related work

There are several different basic principles for model-based performance evaluation of embedded systems. An important distinction is drawn between empirical and worst-case methods for performance evaluation. The former class includes most simulation-based approaches, whereas the latter contains exhaustive methods such as analytical or state-based verification techniques. Besides these two classes there are also stochastic methods for performance evaluation which we do not, however, consider in this context.

The use of simulation to estimate the performance of system designs is the current state-of-the-art in many application domains. There exist various simulation-based methods for different levels of abstraction. Commercial tool suites for electronic system design offered by companies such as Cadence, Synopsis, Mentor Graphics, or Magma offer a broad range of simulation instruments from high-level discrete event simulators to cycleaccurate software/hardware co-simulators. Apart from commercial design tools, there are also open-source simulation environments. Examples are processor architecture simulators such as SimpleScalar [ALE02, Sim] and PTLsim [You07, PTL], network simulators such as ns-2 [ns2], full system simulators like OVPsim [Ovp], and system-level discrete event simulators such as SystemC [Sys, GLMS02]. While most of these simulators have a fairly broad application scope, there are also tools dedicated to particular system types, e.g. the TrueTime simulator for networked control systems [CHL<sup>+</sup>03, TT].

The main advantage of simulation-based methods for performance evaluation is their large and extendable modelling scope. In other words, they permit to represent a broad domain of systems with an almost arbitrary level of detail. Unfortunately, detailed system simulations are often very time consuming, especially if high timing fidelity is required (e.g. cycle-accurate simulators). The crucial drawback of simulation-based approaches is that they are typically not exhaustive, that is, they cannot guarantee full coverage of the system behaviour. Especially for large and complex system architectures, it is often unfeasible to reveal performance corner cases by means of simulation. The consequence is that simulators cannot be employed to provide guarantees on the best-case/worst-case performance of embedded systems, as required by several application domains (e.g. hard real-time systems).

The need for reliable and provably correct performance bounds for complex embedded systems has driven research for many years. The result are several analytic and state-based formal methods for worst-case performance evaluation, which are discussed in the remainder of this section. Various analytical methods for timing/performance evaluation have been introduced for different abstraction levels in the design flow. At the process level, designers of hard real-time systems are typically interested in determining the worst-case execution time (WCET) of programs. The complexity of this task depends largely on the architecture of the underlying processor, as components such as caches, pipelines, or branch predictors complicate the analysis. Analytical methods for WCET analysis have been proposed in [LM95], [Wil] amongst others. For an extensive overview of methods and tools we refer the reader to [WEE<sup>+</sup>08].

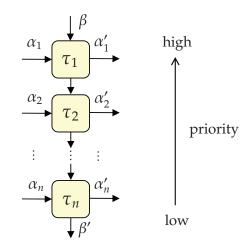

At the system level, designers have to guarantee the performance of multiple real-time tasks that are executed on a single processor or on a distributed system. The analysis of the worst-case completion times of concurrent tasks on a single processor is commonly denoted as *scheduling analysis*. This field has been extensively studied over the past 35 years and there is a large body of results for different task scheduling policies such as Rate Monotonic Scheduling (RM) [LL73], Fixed Priority Scheduling (FP) [JP86, TBW94], Earliest Deadline First Scheduling (EDF) [LL73], or Round Robin Scheduling (RR) [RKZ95, RLH<sup>+</sup>07]. There also exist many extensions for the various scheduling algorithms, e.g. for the consideration of offsets [PG98], mutually exclusive shared resources [BA06], task re-executions [LB03], and limited priority levels [BYJ03]. Detailed information about the various algorithms can be found in [But97], as well as in other books on the topic. In recent years, the attention of the real-time scheduling community has shifted mostly to multiprocessor platforms, e.g. [GFB03, BBMS10].

The analytic performance evaluation of *distributed* embedded systems has also been investigated. The major intricacies with respect to the single processor case are concurrent task executions, heterogeneous resources as well as communication delays on shared communication devices. Several methods have been proposed so far for the worst-case analysis of distributed real-time systems. The methods are based on essentially different abstractions. The first idea was to extend results of the classical scheduling theory to the distributed case. The resulting combined analysis of processor and bus scheduling is often referred to as *holistic scheduling analysis*. Rather than a single evaluation method, holistic scheduling denotes a collection of techniques for the analysis of distributed systems, each of which is tailored for a specific combination of processor scheduling and communication arbitration. The first work in this direction is by Tindell and Clark. In [TC94] they combine FP preemptive scheduling on the processors of a distributed system with TDMA scheduling on the interconnecting bus. In [PEP02] Pop, Eles and Peng analyze mixed eventtriggered and time-triggered task sets that communicate over protocols with both static and dynamic phases such as FlexRay. Holistic scheduling under the presence of data or control dependencies has been studied in [YW95] and [PEP00], respectively. Other holistic analysis techniques can be found in the literature, e.g. [PG03]. The major drawback of holistic analysis methods is their poor flexibility. While they produce accurate results for a particular system architecture, they are typically not applicable to other system configurations. Hence, their modelling scope is strongly limited. This implies that for every new system configuration a new holistic analysis method would have to be developed, which is obviously a very difficult task. Another important issue for holistic techniques is scalability. This is because the complexity of the monolithic models obviously increases with the size of the represented system. The heterogeneous set of available techniques also makes it difficult to apply holistic scheduling in practice. This latter problem was, however, alleviated by González Harbour et al. with the release of the MAST tool [GGPD01], which enhances, implements and aggregates several holistic analysis algorithms.

Compositional or modular analysis methods such as SymTA/S [HHJ<sup>+</sup>05] and Modular Performance Analysis (MPA) [CKT03] form a more flexible and scalable alternative to analytically bound the worst-case performance of distributed systems. These methods make use of a modular system abstraction in which every hardware/software unit of the system is modelled by an individual abstract component. These abstract components represent single computation or communication tasks of the system. Typically, it is assumed that each task is triggered by the arrival of an input event, and that it produces an output event after its execution is completed. The dataflow among components is then abstracted by means of event streams (timed sequences of events). The basic concept of compositional performance analysis methods is to evaluate the system component-wise by forwarding the output streams of an individual component to other dependent components. System performance metrics such as end-to-end delays of events are then derived by aggregating the results of individual component analyses.

The SymTA/S analysis approach was introduced by Richter, Jersak and Ernst [RJE03, Ric05, Jer05]. The general idea of the methodology is to reuse algorithms from classical scheduling analysis (or extensions thereof) at the component level, and to propagate local analysis results to other components through appropriate interfaces. These steps are repeated until all components in the model are analyzed. In the case of cyclic dependencies among components, fixpoint iteration is applied. Details on the generation of starting points and on the convergence of the SymTA/S analysis in the presence of cyclic dependencies can be found in [Ric05] and [SDI+08], respectively. For the local performance analysis of components, e.g. for determining the worst-case response time to input events, SymTA/S uses formal analysis methods based on the busy window technique proposed by Lehoczky [Leh90]. SymTA/S offers local analysis techniques for FP scheduling (preemptive and non-preemptive), Round Robin, TDMA, EDF, CAN, and several arbitration schemes used in the automotive domain. The key element of the SymTA/S analysis methodology is the use of event models to represent the dataflow among components. An event model is an abstract representation for the timing of event arrivals in a stream. Since most algorithms of classical scheduling analysis assume simple patterns for the arrival of input events (e.g. periodic events, periodic events with jitter), in the original SymTA/S approach [HHJ<sup>+</sup>05], the interface among components is limited to a small set of simple event models. These are commonly denoted as Standard Event Models (SEM) or Periodic with Jitter (PJD) models. To guarantee that the output event model of a component fits the input event model expected by the following component, the SymTA/S method applies appropriate Event Model Interfaces (EMIF) or Event Adaption Functions (EAF). While the restriction to SEMs enables the reuse of previous results of real-time research, and simplifies the calculation of output event models, it has the drawback of limited analysis accuracy. This is because, on the one hand, complex timing behaviours of general event streams cannot be captured by SEMs and, on the other hand, event model conversions may be lossy. Recently, the restriction of SymTA/S to SEMs was relaxed by Schliecker et al., who extended the methodology to arbitrarily shaped event models [SRIE08]. In particular, the authors of [SRIE08] introduce the multiple event busy time model which they use to characterize the outputs of arbitrarily triggered components under FP scheduling. Many other extensions and ameliorations have been presented for the SymTA/S analysis method. Examples are the consideration of correlations among events (context-based analysis) [JHE04, HE05], pipelined delay analysis [SE09], analysis of MPSoC architectures with shared memory [NSE09], analysis of hierarchical communication [RE08], as well as SymTA/S-based sensitivity analysis [Rac09] and robustness optimization [Ham08]. The rich set of available extensions as well as the development of a commercial tool [Sym] make SymTA/S a very powerful framework for worst-case system-level performance evaluation. Nonetheless, the method has some inherent limitations. First, it is based on existing algorithms of scheduling analysis which means that for any new scheduling policy a new, dedicated analysis needs to be conceived. Moreover, the method is not modular in terms of processing or communication resources. For instance, it does not

A different approach to compositional performance analysis that does not rely on classical scheduling theory is the Modular Performance Analysis (MPA) which was introduced by Thiele et al. in [TCN00]. The method uses the Real-Time Calculus (RTC), a formalism that has its roots in Net-

support the modelling of hierarchical scheduling policies.

work Calculus [LT01], to analyze the flow of event and resource streams through a network of computation and communication components. The MPA framework is discussed in detail in Section 2.2.

Apart from analytical methods for performance evaluation, one can also apply general state-based verification techniques to characterize the worst-case performance of a system. The state-based formal verification of systems has been investigated extensively over the past 30 years. The task of automatically verifying whether a state-based model of a system meets a given specification, typically given as formula in temporal logic, is commonly denoted as model checking. Since the pioneering work of Clarke, Emerson and Sifakis [CES86, QS82], various techniques for model checking have been proposed and implemented in verification tools, e.g. [Spi, NuS]. For details on model checking and an overview of existing techniques we refer the reader to [BK08, CGP99]. For the domain of realtime systems, the automatic verification of hybrid models is particularly interesting. Hybrid models are state-based representations of systems that combine discrete system properties with continuous quantities such as time. A prominent example are Timed Automata (TA) [AD94]; similar formalisms can be found in [Hen96, GMM90]. Two examples of corresponding model checking tools are Uppaal [BLL<sup>+</sup>] and Kronos [BDM<sup>+</sup>]. While none of the mentioned state-based verification techniques is particularly conceived for performance evaluation, there has been work on applying them for this purpose. For instance, TA modelling techniques have been applied for monoprocessor scheduling analysis, see [FPY02], and the corresponding tool Times [AFM<sup>+</sup>]. In [NM09, Ch.4] Larsen et al. provide a framework based on Uppaal for the analysis of multiprocessor scheduling scenarios which also considers timing uncertainties and task dependencies. An alternative framework for scheduling analysis of MPSoC systems has been proposed by Brekling, Madsen et al., see [BHM08] and [NM09, Ch.5]. As last example, we mention the approach for worst-case performance evaluation of distributed systems presented by Hendriks and Verhoef [HV06] which relies on customized TA representations of Standard Event Models.

State-based performance verification methods have two advantages with respect to analytical approaches. They typically offer a larger modelling scope, as arbitrary finite-state models can be used to represent the system behaviour. Moreover, they can derive *exact* performance bounds for the modelled system, as there is no inherent abstraction loss for these methods. In other words, state-based approaches for performance verification are typically more accurate than analytical ones. However, the detailed modelling capabilities do not come for free: the verification of state-based models is seriously affected by state-space explosion. This fact often forecloses the application of state-based methods to large, realistic systems.

There are also hybrid approaches for system-level performance evaluation which integrate different paradigms. For instance, in [LRD04] Lahiri et al. present a method that combines simulation for parameter estimation with analytical system evaluation. The main advantage of this method are faster system evaluations with respect to a purely simulative approach. Similar hybrid methods can be found in [KPBT06, BPN<sup>+</sup>04, HKH<sup>+</sup>09] and in [NM09, Ch.4]. In Chapter 5 of this thesis, we will discuss a hybrid technique for worst-case performance evaluation that combines MPA and TA, that is, an analytical and a state-based technique.

Finally, we would like to mention languages or frameworks for the compositional design of heterogeneous real-time systems such as BIP [Bip], Ptolemy II [Pto], Metropolis [Met], POOSL [Poo], or Moses [Mos]. They not only offer useful features such as deadlock analysis, correctness by construction, or automatic code generation but also support the simulation and, in some cases, the formal verification of the modelled systems. Hence, they can also be employed for system-level performance evaluation.

## 2.2 Modular Performance Analysis

In this section, we introduce the framework for Modular Performance Analysis (MPA) which forms the basis for the contributions of this thesis. MPA is an analytical method for worst-case performance evaluation of distributed systems. In contrast to SymTA/S, its origins do not come from classical real-time scheduling, but from network performance analysis. The MPA formalism provides an elegant way of capturing the workload imposed on a system by concurring applications, as well as the service offered by the system architecture. A key feature of MPA is modularity; MPA represents each hardware/software unit of a system by an individual abstract component. This considerably eases the analysis of large and heterogeneous distributed systems. In MPA, abstract components are combined to form a performance model (or MPA model) of a system. An MPA model is used to derive performance metrics like worst-case endto-end delays or buffer fill levels. What distinguishes MPA from other analysis methods is that it explicitly characterizes the service, i.e. the processing or communication resources, which are available to individual components. This not only permits systems designers to model complex resource availability patterns, but also strengthens the compositionality of the approach in terms of resource sharing schemes.

In the following, we first illustrate the general concepts of the modular system abstraction employed in MPA (Section 2.2.1). Then, we briefly de-

scribe a simple formalism for characterizing the performance of a system in the time domain (Section 2.2.2). As we will explain, this formalism in the concrete time domain is of limited practical use for the worst-case performance evaluation of systems. However, it serves as basis for the introduction of the Real-Time Calculus (Section 2.2.3), the interval-based formalism commonly used within MPA for worst-case performance evaluation.

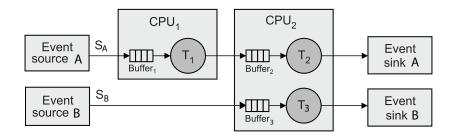

#### 2.2.1 A general performance model

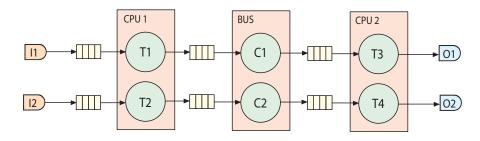

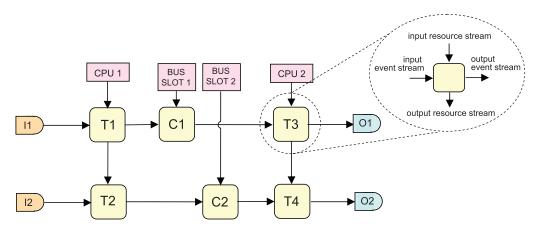

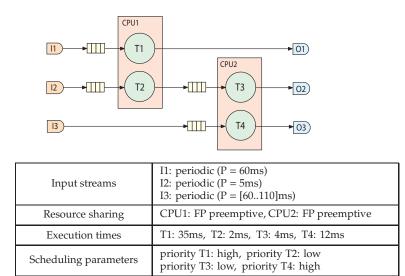

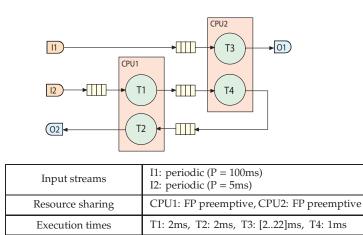

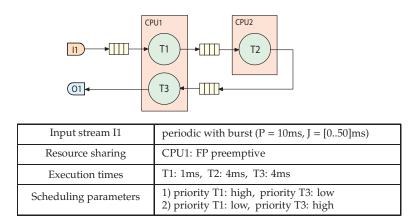

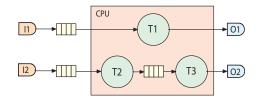

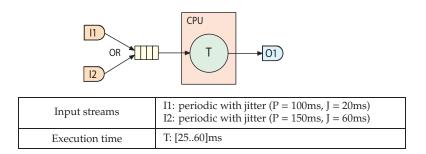

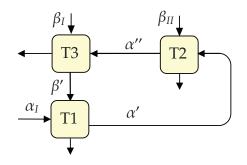

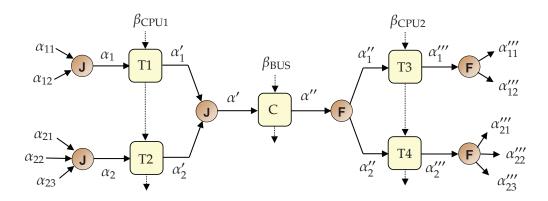

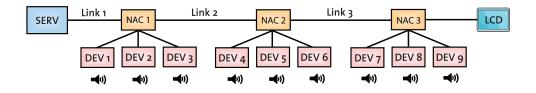

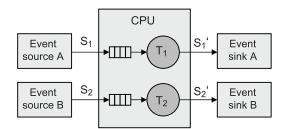

We will illustrate the general modelling approach of MPA by means of a simple example. Consider the system design shown in Figure 3. The system consists of a distributed architecture that processes two concurrent data streams. The data streams consist of data tokens that are generated by the data sources *I1* and *I2*. Both data streams are first processed by dedicated tasks on *CPU1*, then transmitted over a bus, and finally processed further by the tasks of *CPU2*. The processed data tokens are collected by the sinks O1 and O2. In the considered system, each processing or communication unit, i.e. each task on a CPU and each channel on the bus, has a dedicated input buffer which temporarily stores data tokens if the corresponding unit is already busy. We assume that a preemptive fixed priority scheduler is adopted on CPU1 and CPU2 to execute the respective tasks. In particular, we let task T1 have priority over task T2, and task T3 have priority over task T4. For the communication bus, we suppose that a TDMA arbitration scheme is employed to schedule channels C1 and C2. We assume that the data generation patterns of the data sources are known, as well as the worst-case execution (transmission) times of tasks (channels). The goal of the analysis is to safely bound performance characteristics of the system such as the maximum end-to-end delays of data tokens, or the maximum buffer fill levels.

**Fig. 3:** Architecture of example system

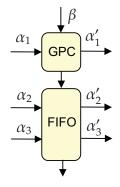

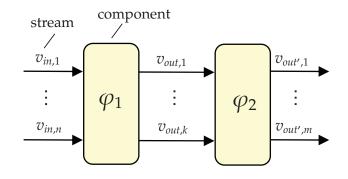

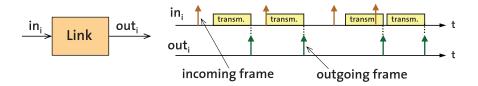

Figure 4 shows the MPA model for the described system. MPA adopts component networks as a basic model of computation. Each compo-

nent represents an individual processing or communication unit of the modelled system. The components communicate via event passing. In particular, the communication is based on infinite FIFO (first-in first-out) event buffers among the components.<sup>1</sup> The components are triggered by input events which represent incoming data tokens that need to be processed. Outgoing data tokens are modelled by means of output events. These events form *event streams*, that is, potentially infinite sequences of timed events. The abstraction of event streams is used in MPA (and other modular formalisms such as SymTA/S) to represent the dataflow in a distributed system. In Figure 4, the event streams are represented by horizontal arrows.

Fig. 4: General MPA model of example system

The MPA formalism also explicitly quantifies the service that is available to individual components in terms of processing or communication resources. This is done by means of *resource streams*. In particular, an input resource stream is used to represent the availability of a resource to a component over time. Similarly, an output resource stream models the resources that are left over by a component. In Figure 4, the resource streams are represented by vertical arrows. Note that scheduling policies for shared resources are typically modelled by the way the resource streams are propagated. For instance, to represent the fixed priority scheduling policy adopted on *CPU1* for the tasks *T1* and *T2*, we connect the resource output of *T1* with the resource input of *T2*. In other words, *T2* gets only the processing service left over by *T1*. An important difference between event and resource streams is that the service cannot be buffered. In other words, resources that are not immediately used by a component are wasted.

<sup>&</sup>lt;sup>1</sup>For the sake of simplicity, these event buffers are not shown in Figure 4 and in all the other MPA models represented in this thesis.

To summarise, in the abstract view of MPA, distributed systems are networks of components that manipulate event and resource streams. More precisely, the individual components model the interplay over time between demanded and available system resources. Hence, the performance model is well suited to derive local and system-wide performance metrics such as latencies or buffer demands.

Next to the general view of performance models in MPA, we obviously also need a (mathematical) formalism that specifies the following points:

- How event and resource streams are represented

- What the transfer functions of different components are

- How performance metrics (e.g. end-to-end delays) are computed

These points will be addressed in Sections 2.2.2 and 2.2.3, where we present two different but closely related alternatives for performance analysis within MPA.

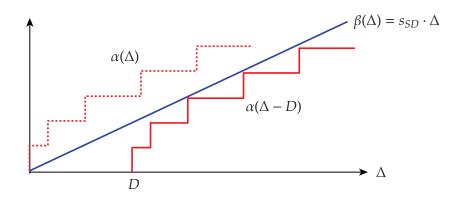

#### 2.2.2 Performance characterization in the time domain

The most natural way to derive the performance of a component network in MPA is to specify the involved streams as well as the transfer functions of the various components in the time domain. In the following, we introduce a simple formalism that allows us to do so.

#### 2.2.2.1 Arrival and service functions

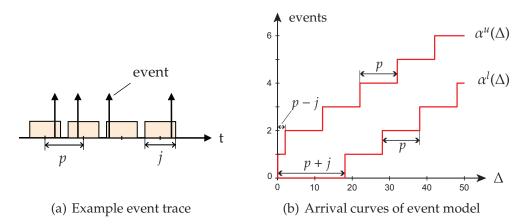

An event trace is, in essence, a timed sequence of event arrivals. More precisely,

- a *timed event* is a pair (e, t) where e is some event and  $t \in \mathbb{R}$  an associated time stamp;

- an *event trace* (or *concrete event stream*) is an (infinite) sequence (*e*, *t*<sub>1</sub>); (*e*, *t*<sub>2</sub>); . . . of timed events which are ordered by non-decreasing time stamps, i.e., *t<sub>i</sub>* ≤ *t<sub>i+1</sub>* for *i* ≥ 1.

In the following, we use the notion of arrival function to characterize event traces.

**Def. 1:** (Arrival Function) An arrival function  $r : \mathbb{R} \times \mathbb{R} \mapsto \mathbb{R}^{\geq 0}$  unambiguously represents an event trace, where r(s, t) for s < t denotes the number of events that arrive in the time interval [s, t), with r(s, s) := 0.

In simpler words, the arrival function r 'counts' the number of event arrivals in a given time interval.<sup>2</sup> Note that the definition of arrival function is not necessarily bound to the above concept of event trace: For a given time interval, an arrival function can also quantify the demanded processing cycles, the bytes to transmit, or any other discrete or continuous workload unit.

For interpretation, it is often useful to consider the following property which holds for any arrival function as defined above:

$$r(s,t) = r(a,t) - r(a,s) \quad \forall a \le s \le t$$

(2.1)

For instance, if only the positive time axis is considered for the arrival of events, one may choose a = 0 in Equation (2.1).

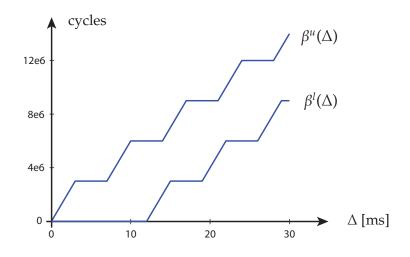

As mentioned above, components typically need resources in order to perform the requested operation. We describe the availability of resources by means of service functions.

**Def. 2:** (Service Function) A service function  $c : \mathbb{R} \times \mathbb{R} \mapsto \mathbb{R}^{\geq 0}$  unambiguously represents a concrete resource stream, where c(s, t) for s < t denotes the number of resource units that are available in the time interval [s, t) with c(s, s) := 0.

Again, we allow a liberal definition of resource units here. The amount of available resources can be specified in resource token, processing cycles, bytes, or any other discrete or continuous quantity.

### 2.2.2.2 Component models

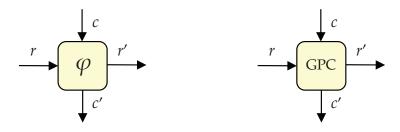

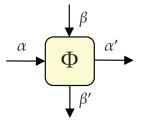

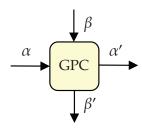

The basic building blocks of performance models are *performance components*. Performance components can be basically seen as deterministic transducers of concrete event and resource streams. More precisely, a general performance component  $\varphi$  receives an input event trace r, and an input resource stream c, and it produces an output event trace r', and an output resource stream c'. This view is illustrated in Figure 5(a). In the figure, we use  $\varphi$  to denote the behaviour of the component.  $\varphi$  is a transfer function from input to output, i.e.,  $(r', c') = \varphi(r, c)$ . The function  $\varphi$  reflects the particular processing semantics of the component. For now, we consider only performance components with a single event input port and a single event output port. However, MPA also supports performance components with multiple event input/output ports (cf. Section 2.2.3).

<sup>&</sup>lt;sup>2</sup>For easier readability, in this thesis we use the letter r to denote both, an event trace and the corresponding arrival function; it is clear from the context to which of the two we refer.

(a) A general performance component (b) Greedy Processing Component

Fig. 5: Performance components

Various components with different behaviours comply with the above general description. One particular performance component which represents the behaviour of many hardware or software units is the *Greedy Processing Component (GPC)*. It models a task that is triggered by the events of the incoming event stream which queue up in a FIFO buffer. The task processes the events in a greedy fashion while being restricted by the availability of resources. In other words, the task processes an event as soon as it receives resources to do so. The graphical representation of a GPC is shown Figure 5(b). Note that often we also denote GPCs with the name of the task they model (cf. Figure 4).

### Thm. 1: (Transfer function GPC) A GPC component has the input/output relations

$$r'(s,t) = \inf_{s \le \lambda \le t} \{ r(s,\lambda) + c(\lambda,t) + b(s), c(s,t) \}$$

(2.2)

$$c'(s,t) = c(s,t) - r'(s,t)$$

(2.3)

where b(s) denotes the initial fill level of the event input buffer.

**Proof.** In any time interval, the output of the component is restricted by the available resources. Hence, we have  $r'(s,t) \leq c(s,t)$  and also  $r'(s,t) \leq r'(s,\lambda) + c(\lambda,t)$ . But at the same time, in any time interval the component cannot output more events than those available at the input. Thus, we have  $r'(s, \lambda) \leq r(s, \lambda) + b(s)$ . If we combine these constraints, we obtain  $r'(s,t) \leq \min\{r(s,\lambda) + c(\lambda,t) + b(s), c(s,t)\}$ . Let us now assume that there is some last time  $\lambda^* < t$  when the input buffer was empty. This implies that all events that arrived up to  $\lambda^*$  are processed by that time, i.e.  $r'(s, \lambda^*) = r(s, \lambda^*) + b(s)$ . In the interval  $(\lambda^*, t)$  the input buffer is never empty, which means that all available resources are being used to produce output events, i.e.  $r'(s,t) = r(s,\lambda^*) + b(s) + c(\lambda^*,t)$ . In the case that the buffer is never empty, we simply have r'(s,t) = c(s,t). As a result, we obtain the transfer function (2.2). On the other hand, relation (2.3) is obvious: the component cannot buffer resources over time. Hence, in any time interval, the remaining resources are simply given by the available resources minus the consumed resources.

An important prerequisite for the above relations is that the workload r and the service c are specified in the same unit. Let us, for instance, assume that r counts the number of arriving input events, but c quantifies the available service in processing cycles. In this case, the mismatch can be resolved by determining the resource demand of each input event in terms of processing cycles, i.e. by converting r to a resource-based representation. In the simplest case, each input event imposes the same workload on the component. Then, the conversion boils down to a simple scaling of the arrival function r (see the Scaler component below).

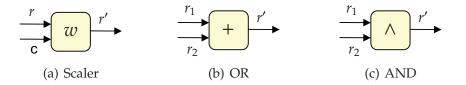

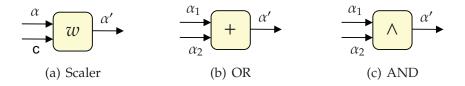

Besides performance components which specify the interplay of event and resource streams, a performance model can also contain simpler components that do not interact with resources. The following list briefly describes a few such *elementary components*. The corresponding graphical representations are shown in Figure 6.

• A *scaler* component is used for converting workload representations (e.g. from events to processor cycles). Its transfer function is given by

$$r'(s,t) = w \cdot r(s,t), \tag{2.4}$$

where *w* is a positive scaling factor.

• An *OR* component produces an output event for every input event. The transfer function is

$$r'(s,t) = r_1(s,t) + r_2(s,t).$$

(2.5)

• An *AND* component produces an output event only if there is an input event on *all* inputs. For two input event streams  $r_1$ ,  $r_2$  the transfer function of the AND component is

$$r'(s,t) = \min\{b_1(s) + r_1(s,t), b_2(s) + r_2(s,t)\},$$

(2.6)

where  $b_1(s)$  and  $b_2(s)$  denote the fill levels of the two input buffers at time *s*.

Fig. 6: Elementary components

We assume that all elementary operations are immediate. In other words, elementary components do not introduce any delay.

25

$\Box$

### 2.2.2.3 Performance Analysis

26

What remains to be specified is how performance characteristics of a system are derived from the performance model. For a GPC component, we can use the following equation to quantify the fill level *b* of the input buffer at time *t*, provided that we know the fill level *b* at initial time *s*:

$$b(t) = b(s) + r(s, t) - r'(s, t)$$

(2.7)

Similarly, we can quantify the delay that an event experiences at a GPC. In particular, the delay d experienced by the last event arriving in the interval [*s*, *t*) is given by:

$$d = \inf\{\tau \ge 0 : b(s) + r(s,t) \le r'(s,t+\tau)\}$$

(2.8)

Once the performance of each individual component of a model has been computed, we can derive system-wide performance metrics by aggregating the individual results. For instance, the end-to-end delay experienced by a particular event is simply given by the sum of the delays experienced at the individual performance components that the event traverses.

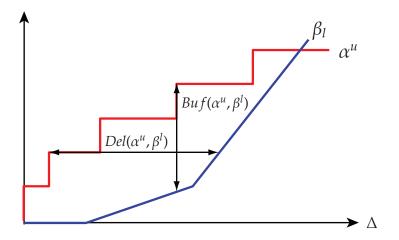

### 2.2.2.4 Limitation