## **ETH** zürich

## Research Collection

#### **Doctoral Thesis**

### An Efficient Platform and Communication Architecture for Eventtriggered Cyber-physical Systems

#### Author(s):

Sutton, Felix

#### **Publication Date:**

2018

#### **Permanent Link:**

https://doi.org/10.3929/ethz-b-000260384 →

#### Rights / License:

In Copyright - Non-Commercial Use Permitted →

This page was generated automatically upon download from the <u>ETH Zurich Research Collection</u>. For more information please consult the <u>Terms of use</u>.

#### Diss. ETH No. 24898

## An Efficient Platform and Communication Architecture for Event-triggered Cyber-physical Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by

FELIX ERNST SUTTON

MSc ETH Zurich

BE(Hons) & BMaCompSc, The University of Adelaide

born April 3, 1982 citizen of Australia and Switzerland

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. Koen Langendoen, co-examiner Dr. Jan Beutel, co-examiner

TIK-SCHRIFTENREIHE NR. 174

Felix Ernst Sutton

## An Efficient Platform and Communication Architecture for Event-triggered Cyber-physical Systems

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich A dissertation submitted to ETH Zurich for the degree of Doctor of Sciences

Diss. ETH No. 24898

Prof. Dr. Lothar Thiele, examiner

Prof. Dr. Koen Langendoen, co-examiner

Dr. Jan Beutel, co-examiner

Examination date: February 9, 2018

### **Abstract**

The interaction of modern cyber technologies with the physical world is widely anticipated to bring significant societal and economic benefits. These cyber-physical systems combine computation and communication technologies to monitor and control complex physical processes, and therefore make it possible to develop smart products and services in industries such as manufacturing, healthcare and agriculture.

The dynamics of many physical processes are inherently unpredictable. This implies that cyber-physical systems must be responsive to non-deterministic events, while remaining energy-efficient for long-term operation and adaptable to the dynamics of the physical process under observation. However, these stringent requirements make it difficult to realize efficient event-triggered cyber-physical systems in practice.

In order to overcome this practical limitation, this thesis presents a new platform and communication architecture for the construction of efficient event-triggered cyber-physical systems with respect to responsiveness, energy-efficiency and adaptability. We make four main contributions:

- We introduce a new platform architecture for composing energy-efficient wireless embedded platforms using a time-predictable processor interconnect called Bolt. The design and prototype implementation of Bolt is presented, which exhibits a throughput of up to 3.3 Mbps and a negligible power overhead of 1.3 μW during periods of inactivity.

- We propose a novel system design methodology for realizing eventtriggered cyber-physical systems, subject to responsiveness, energy efficiency and adaptability design constraints. A prototype of a wireless acoustic emission sensing system is presented, which demonstrates significant improvements to the state-of-the-art with respect to the responsive and energy-efficient detection of acoustic events and their multi-hop dissemination.

- We design and implement ZIPPY, an asynchronous flooding primitive for the rapid dissemination of rare events through a multihop network with unprecedented energy-efficiency. The developed prototype exhibits a dissemination latency as low as 24.4 ms for an 8-bit event packet through a 3-hop network, and a power dissipation of 9.6 μW during periods of inactivity.

• We introduce Blitz, the first communication architecture that combines asynchronous and synchronous flooding primitives to facilitate low latency and energy-efficient multi-hop dissemination of events having adaptable bandwidth requirements. Blitz also incorporates a novel scheme for mitigating erroneous wake-ups, which is shown experimentally to reduce energy consumption. Experiments on a prototype of Blitz show a mean latency as low as 108.9 ms for an 8-bit event packet and its associated data packet of 32 bytes through a 4-hop network, and a power dissipation of 16 μW during periods of inactivity.

### Zusammenfassung

Die Interaktion von modernen Cyber-Technologien mit der realen Welt wird erwartungsgemäss erhebliche soziale und wirtschaftliche Vorteile bringen. Diese Cyber-Physikalischen-Systeme kombinieren Berechnungs- und Kommunikationstechnologien, um komplexe physikalische Prozesse zu überwachen und zu kontrollieren. Diese Systeme ermöglichen es, intelligente Produkte und Dienstleistungen in den Bereichen Fabrikation, Gesundheitswesen und Landwirtschaft zu entwickeln.

Die Dynamiken vieler physikalischer Prozesse sind naturgemäss unvorhersehbar. Deshalb müssen Cyber-Physikalische-Systeme während des Betriebs auf nicht-deterministische Ereignisse reagieren können sowie einen energieeffizienten Langzeitbetrieb und Anpassungsfähigkeit an die Dynamiken des beobachteten physikalischen Prozesses gewährleisten. In der Praxis erschweren diese Anforderungen die Realisierung von effizienten, ereignisgesteuerten Cyber-Physikalischen-Systemen erheblich.

Um die genannten praktischen Einschränkungen zu überwinden, präsentiert diese Dissertation eine neue Plattform- und Kommunikationsarchitektur für die Konstruktion von effizienten, ereignisgesteuerten Cyber-Physikalischen-Systemen in Bezug auf Reaktivität, Energieeffizienz und Adaptabilität. Wir leisten vier Hauptbeiträge zum Forschungsgebiet Cyber-Physikalische-Systeme:

- Wir stellen eine neue Plattformarchitektur für die Erstellung von energieeffizienten, drahtlosen und eingebetteten Systemen vor, welche auf einem deterministischen Prozessor-Bus namens Bolt basiert. Das Design und die prototypische Implementierung von Bolt wird gezeigt. Bolt ermöglicht einen Durchsatz von bis zu 3.3 Mbps, und weist während inaktiven Perioden einen vernachlässigbaren Energieaufwand von 1.3 μW auf.

- Wir präsentieren eine neue System-Design-Methodologie für die Realisierung Cyber-Physikalischenvon ereignisgesteuerten welche Einschränkungen Systemen, strengen Reaktivität, Energieffizienz und Anpassungsfähigkeit unterliegen. Dazu wird Prototyp eines drahtlosen, akustischen Emmissionsvermessungssystems vorgestellt, anhand welchem

deutliche Verbesserungen hinsichtlich der reaktiven und energieeffizienten Erkennung von akustischen Ereignissen sowie deren Multi-Hop-Verbreitung aufgezeigt werden.

- Wir konzipieren und implementieren Zippy, eine asynchrone Flutungsfunktion, welche die rasche Verbreitung von seltenen Ereignissen in einem Multi-Hop-Netzwerk mit einer noch nie dagewesenen Energieeffizienz abwickelt. Der entwickelte Prototyp verfügt über eine Verbreitungslatenz von nur 24.4 ms, um ein 8-bit Ereignispaket in einem 3-Hop-Netzwerk zu verteilen, sowie über eine Verlustleistung von 9.6 μW während Perioden der Inaktivität.

- Wir präsentieren Blitz, die erste Kommunikationsarchitektur, welche asynchrone und synchrone Flutungsfunktionen kombiniert, um geringe Latenzen und eine energieeffiziente Multi-Hop-Dissemination von Ereignissen mit adaptierbaren Bandbreitenanforderungen zu ermöglichen. BLITZ umfasst auch ein neues Schema zur Eindämmung von fehlerhaften Wecksignalen, was den Energieverbrauch verringert, wie experimentell erprobt wird. Experimente mit einem Prototypen zeigen eine niedrige Latenz von nur 108.9 ms für die Verbreitung eines 8-bit Ereignispakets und das damit verbundene Datenpaket von 32 Bytes durch ein 4-Hop-Netzwerk, und eine Verlustleistung von 16 μW während Inaktivitätsphasen.

### Acknowledgments

I would like to express my gratitude to Prof. Dr. Lothar Thiele for giving me the opportunity to conduct research in his institute, and for the exceptional guidance and support offered to me throughout my doctoral studies. I sincerely thank Prof. Dr. Koen Langendoen and Dr. Jan Beutel for their willingness to review this thesis and to serve on my examination committee.

I have had the pleasure to collaborate with many talented researchers and engineers throughout my research. My special thanks to Reto Da Forno, Bernhard Buchli, Marco Zimmerling, Federico Ferrari, Roman Lim, Tonio Gsell, Georgia Giannopoulou, Samuel Weber, Balz Maag, Lukas Sigrist, Andres Gomez, Olga Saukh, Matthias Meyer, Romain Jacob and David Gschwend. I am also thankful to friends who have offered me great support throughout my studies, in particular Sally and Rico Achenbach and Judith Fries.

Last but not least, I would like to express my deepest gratitude to my family in Australia and Switzerland, in particular Susanne and Adrian Sutton, Michelle and Dominik Sutton, Jolanda and Heini Bossert, and Anita and Hansjörg Bossert, for their unrelenting support. This work would not have been possible to complete without the amazing support of my wife, Katharina Bossert.

The work presented in this thesis was scientifically evaluated by the SNSF and financed by the Swiss Confederation and by Nano-Tera.ch. This support is gratefully acknowledged.

## **Contents**

| Al | ostrac  | et e e e e e e e e e e e e e e e e e e                                   | İ  |

|----|---------|--------------------------------------------------------------------------|----|

| Zι | ısamı   | menfassung                                                               | ii |

| A  | knov    | vledgments                                                               | V  |

| Li | st of 1 | Figures                                                                  | i  |

| Li | st of   | Tables                                                                   | X  |

| 1  | Intr    | oduction                                                                 | 1  |

|    | 1.1     | System Requirements                                                      | 4  |

|    | 1.2     | Challenges                                                               | 5  |

|    | 1.3     | Thesis Outline and Contributions                                         | 7  |

| 2  | Con     | nposable and Energy-efficient Wireless Embedded Platforms                | 11 |

|    | 2.1     | Introduction                                                             | 12 |

|    | 2.2     | Background and Related Work                                              | 14 |

|    | 2.3     | Design of Bolt                                                           | 18 |

|    | 2.4     | Prototype Implementation                                                 | 22 |

|    | 2.5     | Formal Timing Analysis                                                   | 25 |

|    | 2.6     | Message Passing Interface                                                | 33 |

|    | 2.7     | Experimental Evaluation                                                  | 37 |

|    | 2.8     | Summary                                                                  | 45 |

| 3  |         | ign Methodology for Efficient Event-triggered Wireless Sensing           |    |

|    | Sys     | tems                                                                     | 47 |

|    | 3.1     | Introduction                                                             | 48 |

|    | 3.2     | Event-triggered System Design                                            | 50 |

|    | 3.3     | Design and Implementation of a Wireless Acoustic Emission Sensing System | 55 |

|    | 3.4     | Case Study: Codetection of Acoustic Events                               | 73 |

|    | 3.5     | Related Work                                                             | 79 |

|    | 3.6     | Summary                                                                  | 80 |

| 4  | On-     | demand Network Flooding                                                  | 81 |

|    | 4.1     | Introduction                                                             | 82 |

|    | 4.2     | Asynchronous Rendezvous                                                  | 84 |

|    | 43      | Overview of Zippy                                                        | 87 |

#### viii Contents

|     | 4.4     | Design and Analysis of ZIPPY                                 | 89  |

|-----|---------|--------------------------------------------------------------|-----|

|     | 4.5     | Experimental Evaluation                                      | 99  |

|     | 4.6     | Related Work                                                 | 111 |

|     | 4.7     | Summary                                                      | 112 |

| 5   | Low     | Latency and Energy-efficient Event-triggered Wireless Commu- |     |

|     | nica    | tion                                                         | 115 |

|     | 5.1     | Introduction                                                 | 116 |

|     | 5.2     | Design of Blitz                                              | 119 |

|     | 5.3     | Wake-up Classification                                       | 123 |

|     | 5.4     | Model-driven Comparative Analysis                            | 138 |

|     | 5.5     | Prototype Implementation                                     | 142 |

|     | 5.6     | Experimental Evaluation                                      | 144 |

|     | 5.7     | Related Work                                                 | 148 |

|     | 5.8     | Summary                                                      | 149 |

| 6   | Con     | clusions and Outlook                                         | 151 |

|     | 6.1     | Contributions                                                | 152 |

|     | 6.2     | Possible Future Directions                                   | 154 |

| Bi  | bliog   | raphy                                                        | 157 |

| Lis | st of l | Publications                                                 | 177 |

| Cι  | ırricu  | lum Vitæ                                                     | 181 |

# **List of Figures**

| 1.1  | An overview of an event-triggered cyber-physical system          | 2          |

|------|------------------------------------------------------------------|------------|

| 2.1  | Overview of the Bolt processor interconnect                      | 19         |

| 2.2  | Simplified hardware block diagram of the Bolt microcontroller.   | 23         |

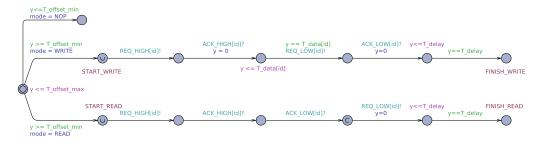

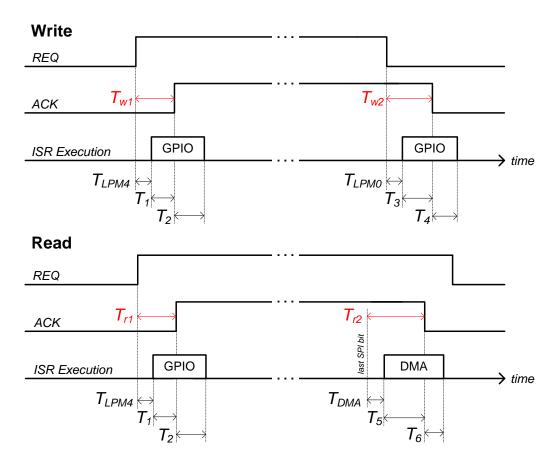

| 2.3  | Signal sequences for write and read operations                   | 24         |

| 2.4  | BOLT software state machine                                      | 25         |

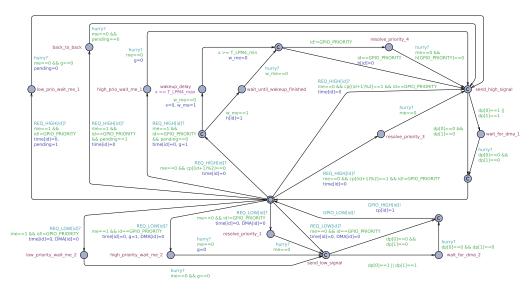

| 2.5  | The platform automaton                                           | 27         |

| 2.6  | The timed automaton                                              | 27         |

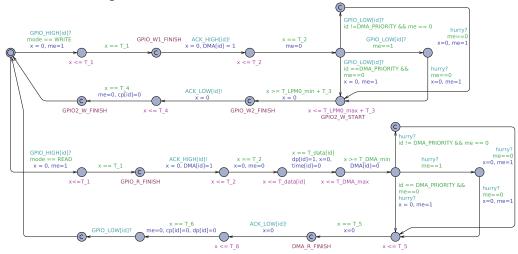

| 2.7  | The GPIO port automaton                                          | 28         |

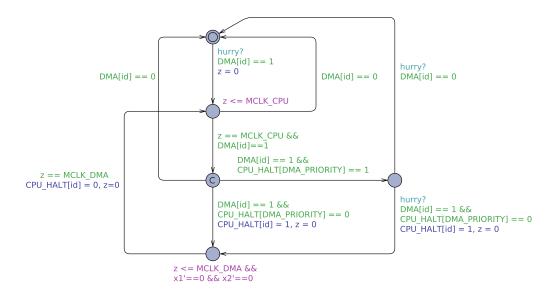

| 2.8  | The DMA channel automaton                                        | 29         |

| 2.9  | Execution of GPIO and DMA interrupt service routines             | 30         |

| 2.10 | Histogram of MCU wake-up and DMA interrupt delays                | 31         |

| 2.11 | Dimensioning Bolt's message queue length                         | 34         |

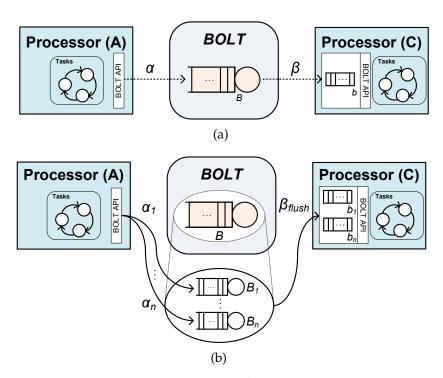

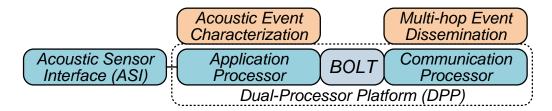

| 2.12 | The Bolt prototype with example processors                       | 37         |

| 2.13 | A custom-built heterogeneous dual-processor platform             | 38         |

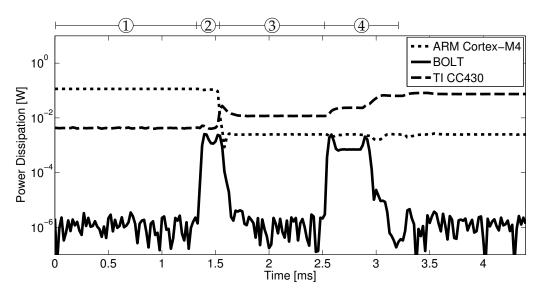

| 2.14 | Power profiles of Bolt and two attached processors               | 39         |

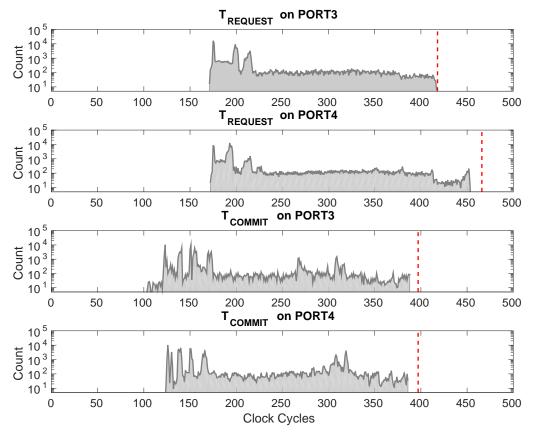

| 2.15 | Histograms of the execution time during message operations       | 40         |

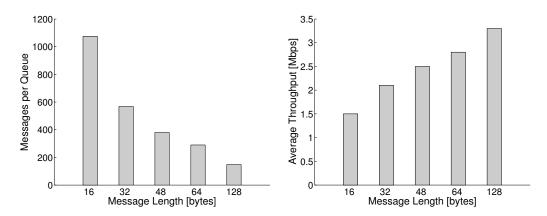

| 2.16 | Maximum queue length and average throughput of Bolt              | 42         |

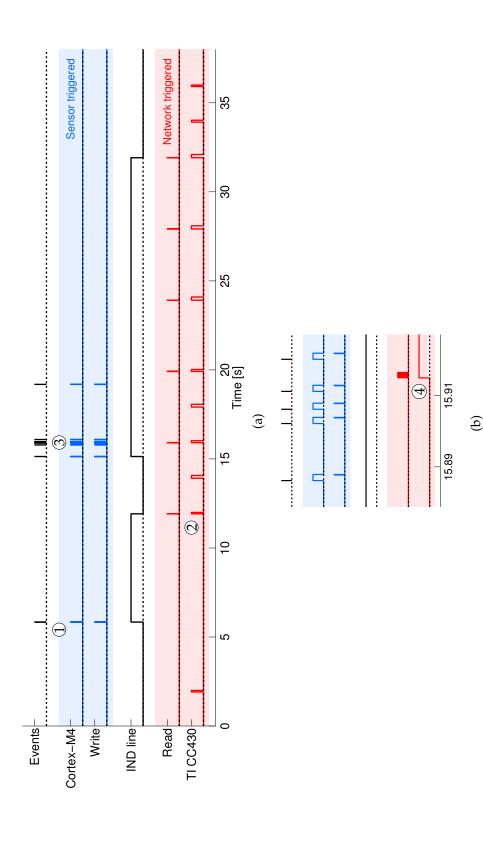

| 2.17 | Signal trace from an example application using Bolt              | 43         |

| 3.1  | Model of a logical event-triggered component                     | 51         |

| 3.2  | Example event stream at the input to a component                 | 52         |

| 3.3  | Example filtering of input events within a component             | 52         |

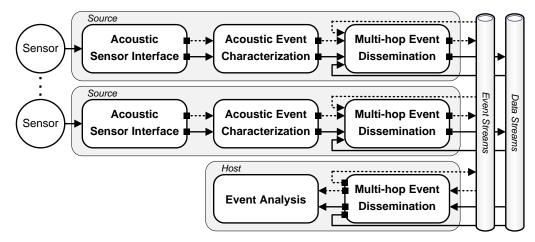

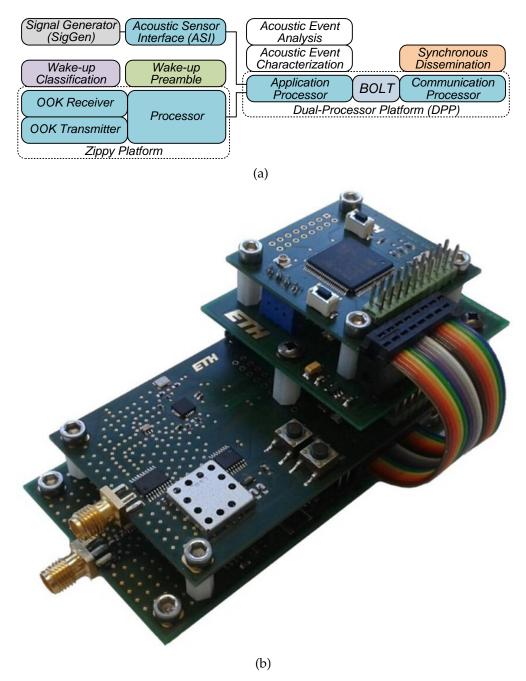

| 3.4  | A wireless acoustic emission sensing system                      | 55         |

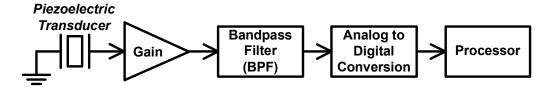

| 3.5  | Block diagram of an always-on acoustic monitoring system         | 56         |

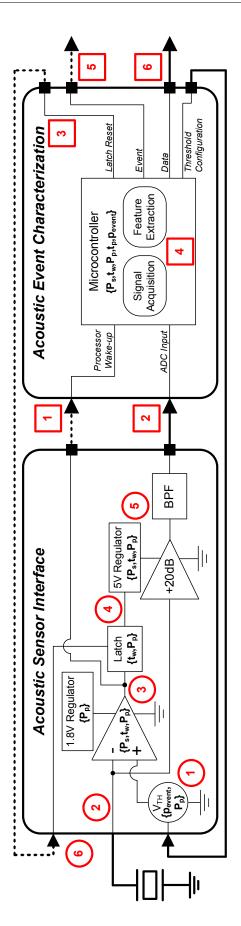

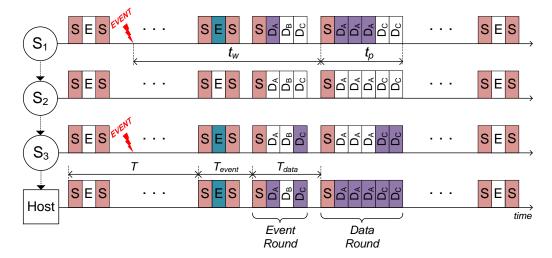

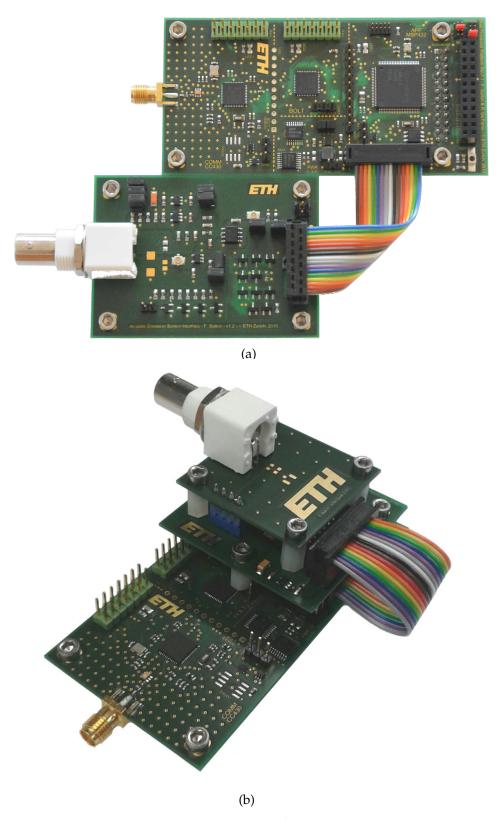

| 3.6  | Block diagram of acoustic sensor interface and characterization. | 57         |

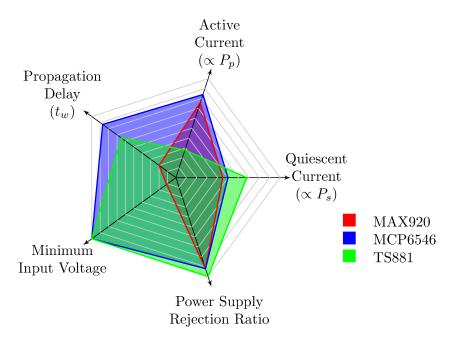

| 3.7  | Visualization of the design space exploration                    | 60         |

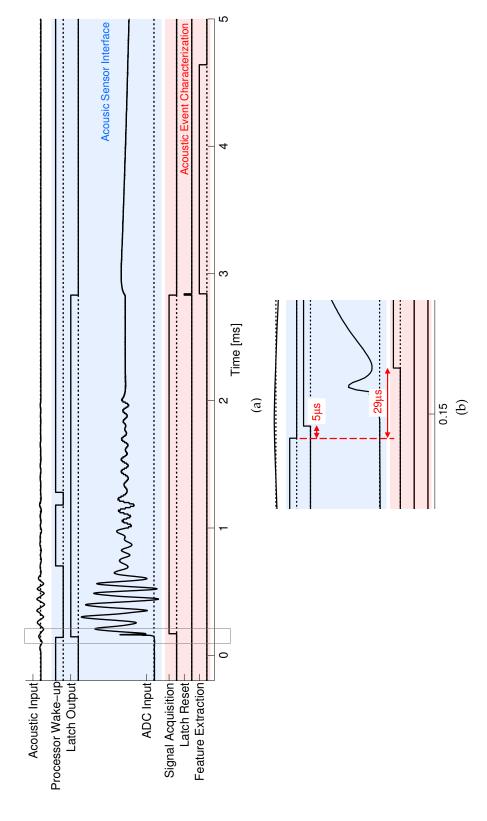

| 3.8  | Signal trace of acoustic sensor interface and characterization   | 61         |

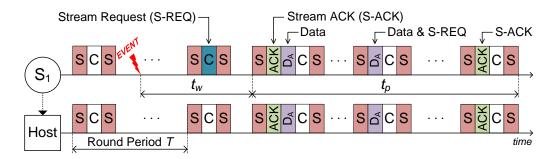

| 3.9  | Example of the Low-power Wireless Bus (LWB)                      | 67         |

| 3.10 | Example of the Event-based Low-power Wireless Bus (eLWB)         | 69         |

| 3.11 | Physical platform architecture of the prototype                  | 71         |

| 3.12 | Prototype implementation of the Dual-Processor Platform          | 72         |

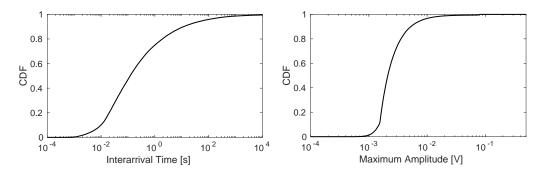

| 3.13 | CDF of interarrival time and maximum amplitude                   | <b>7</b> 3 |

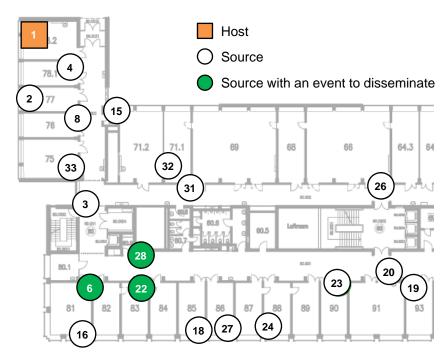

| 3.14 | Map of the FlockLab indoor testbed deployment                    | 74         |

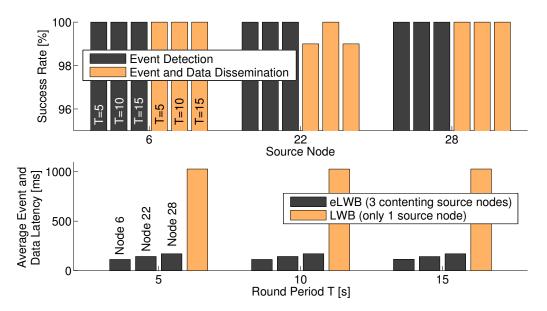

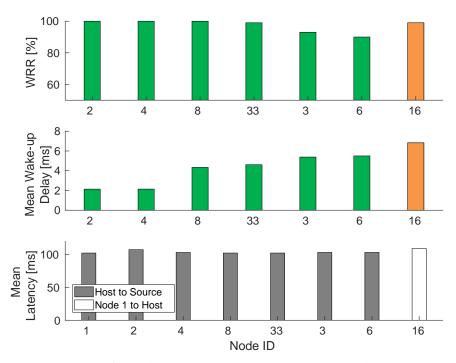

| 3.15 | Results from the indoor testbed evaluation                       | 76         |

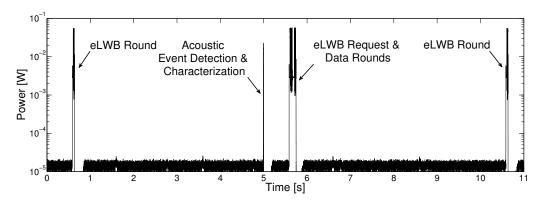

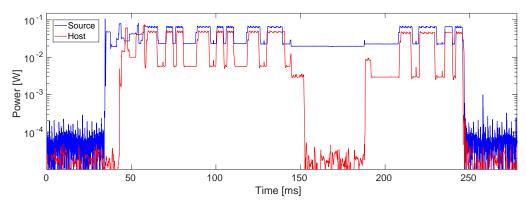

| 3 16 | Power profile of the developed prototype                         | 77         |

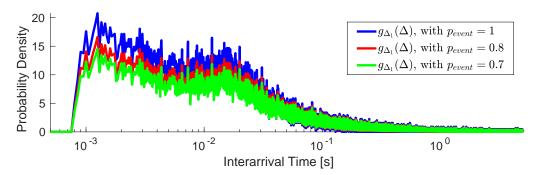

| 3.17                                | PDF of input acoustic events for alternative configurations                                                                                                                                                                                                                                                                           | 78                                     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

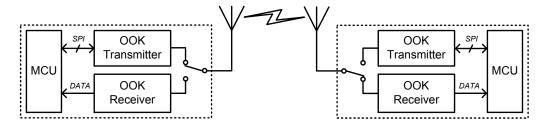

| 4.1                                 | Proposed node architecture for asynchronous rendezvous                                                                                                                                                                                                                                                                                | 85                                     |

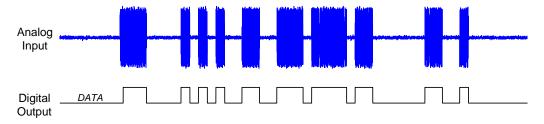

| 4.2                                 | Example analog input and corresponding digital output                                                                                                                                                                                                                                                                                 | 86                                     |

| 4.3                                 | Overview of Zippy in an example 2-hop network                                                                                                                                                                                                                                                                                         | 87                                     |

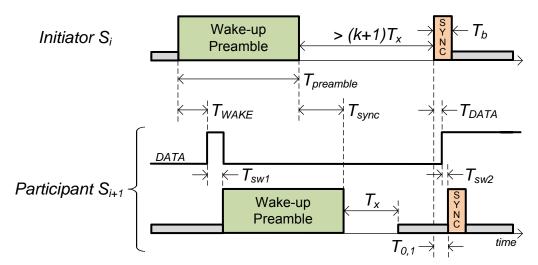

| 4.4                                 | Timing diagram for wake-up and synchronization                                                                                                                                                                                                                                                                                        | 89                                     |

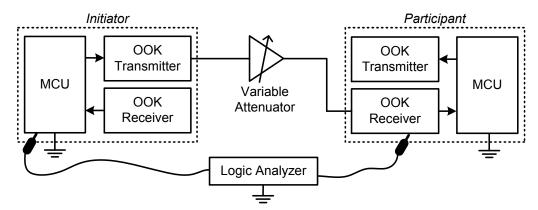

| 4.5                                 | Experimental setup for the timing analysis                                                                                                                                                                                                                                                                                            | 90                                     |

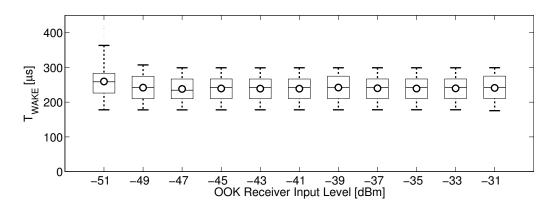

| 4.6                                 | Measured delay to trigger the rising edge of the DATA line                                                                                                                                                                                                                                                                            | 91                                     |

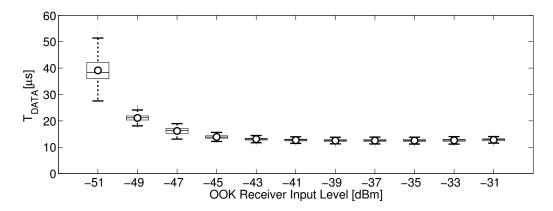

| 4.7                                 | Measured delay to assert the <i>DATA</i> line                                                                                                                                                                                                                                                                                         | 92                                     |

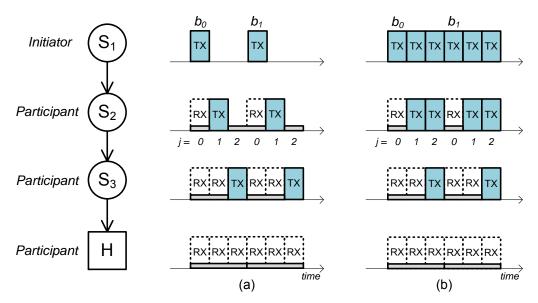

| 4.8                                 | Bit-level dissemination schemes with and without repetition                                                                                                                                                                                                                                                                           | 94                                     |

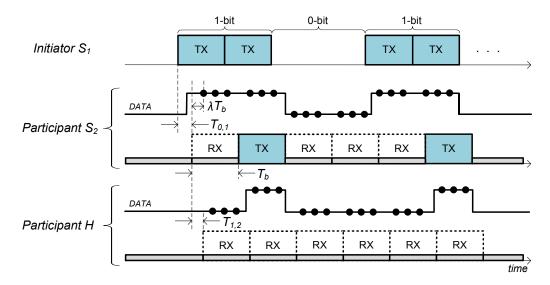

| 4.9                                 | Bit-level dissemination with majority vote sub-bit decoding                                                                                                                                                                                                                                                                           | 95                                     |

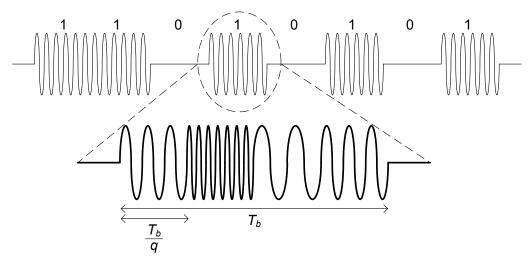

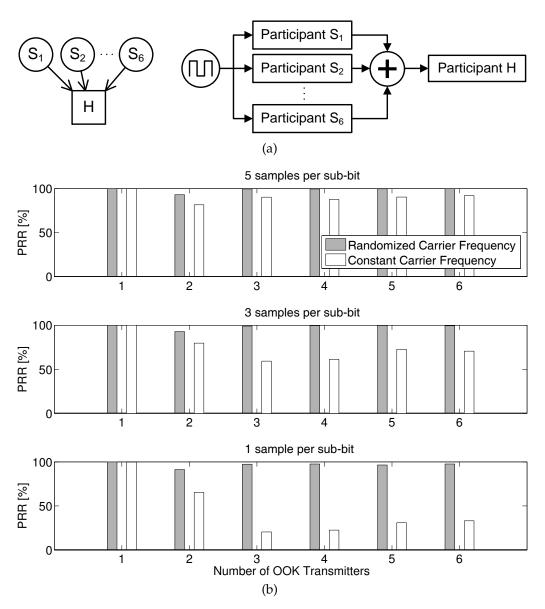

| 4.10                                | OOK transmission using carrier frequency randomization                                                                                                                                                                                                                                                                                | 97                                     |

| 4.11                                | Experimental setup for carrier frequency randomization                                                                                                                                                                                                                                                                                | 98                                     |

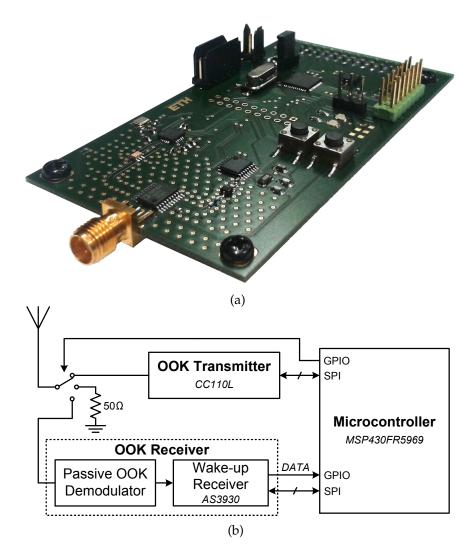

| 4.12                                | Prototype and block diagram supporting ZIPPY                                                                                                                                                                                                                                                                                          | 100                                    |

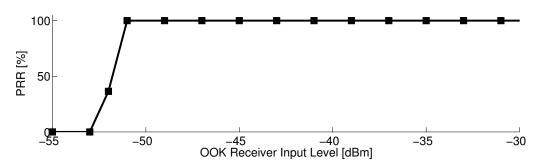

| 4.13                                | Sensitivity measurement of the OOK receiver                                                                                                                                                                                                                                                                                           | 101                                    |

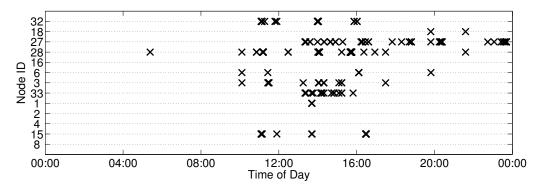

| 4.14                                | Observer erroneous wake-ups during a 24 hour experiment                                                                                                                                                                                                                                                                               | 102                                    |

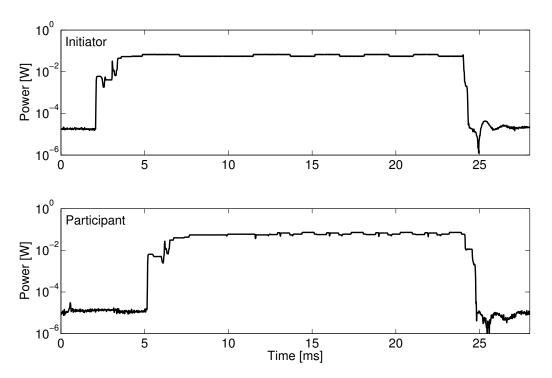

| 4.15                                | Power profile of initiator and participant nodes                                                                                                                                                                                                                                                                                      | 103                                    |

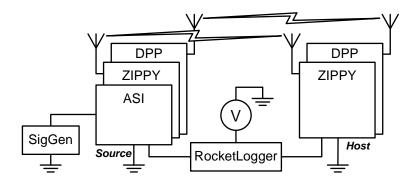

| 4.16                                | Setup for the cabled multi-hop experiments                                                                                                                                                                                                                                                                                            | 104                                    |

| 4.17                                | Results of the cabled multi-hop experiments                                                                                                                                                                                                                                                                                           | 104                                    |

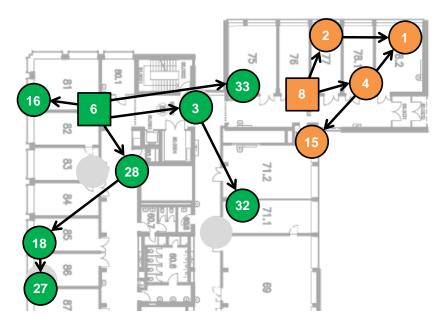

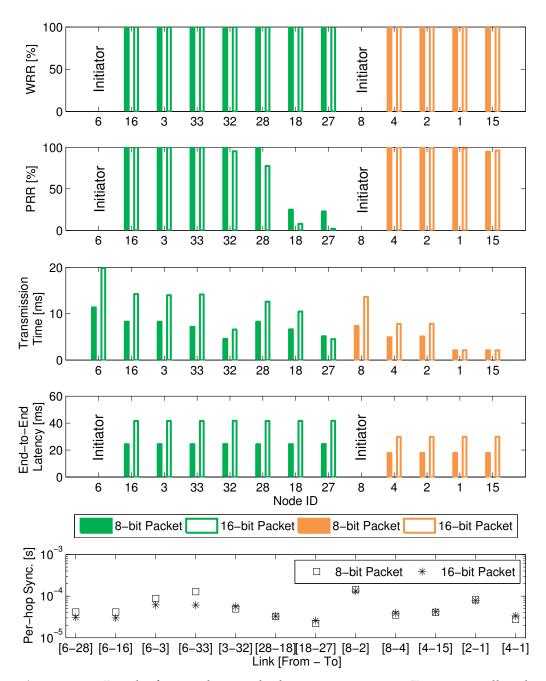

| 4.18                                | FLOCKLAB indoor testbed deployment map for evaluating ZIPPY.                                                                                                                                                                                                                                                                          | 106                                    |

| 4.19                                | Results from indoor testbed experiments using Zippy                                                                                                                                                                                                                                                                                   | 108                                    |

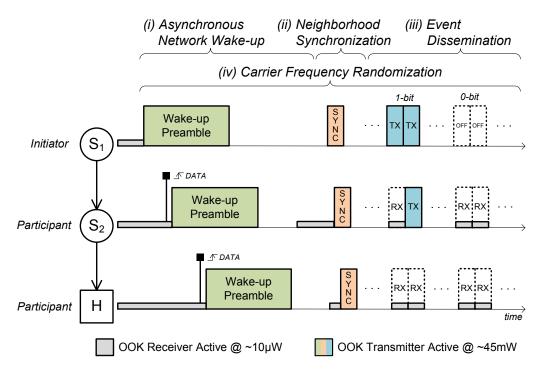

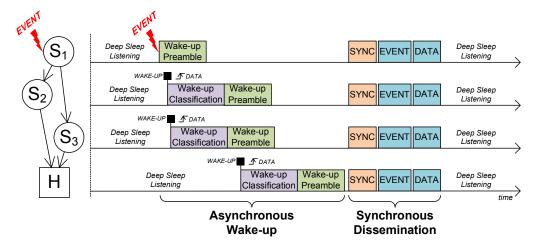

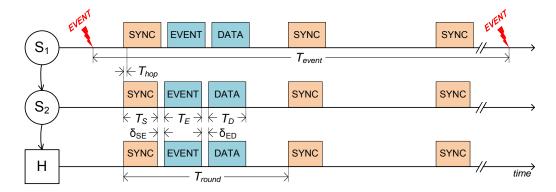

| 5.1                                 | Example multi-hop network and the radio activity of BLITZ                                                                                                                                                                                                                                                                             | 118                                    |

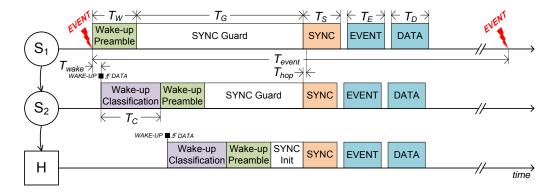

| 5.2                                 | BLITZ asynchronous wake-up and synchronous dissemination                                                                                                                                                                                                                                                                              | 122                                    |

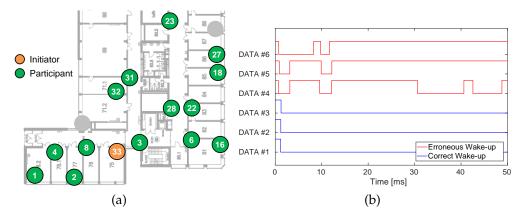

| 5.3                                 | Map of FlockLab deployment and example DATA signals                                                                                                                                                                                                                                                                                   | 125                                    |

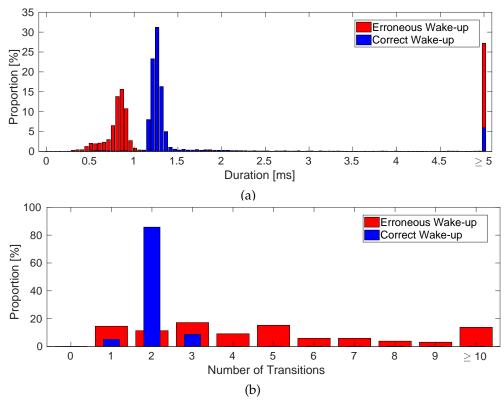

| 5.4                                 | Histogram of first pulse duration and number of transitions                                                                                                                                                                                                                                                                           | 126                                    |

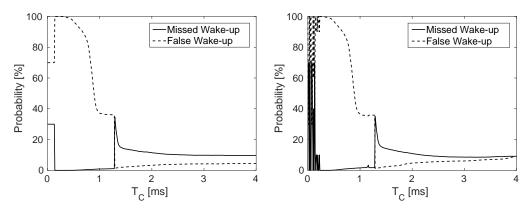

| 5.5                                 | Performance of DT and SVM wake-up classifiers                                                                                                                                                                                                                                                                                         | 128                                    |

| 5.6                                 | FLOCKLAB deployment map and classifier performance                                                                                                                                                                                                                                                                                    | 129                                    |

| 5.7                                 | Network assumed for the wake-up classifier model                                                                                                                                                                                                                                                                                      | 130                                    |

| 5.8                                 | Energy consumption of BLITZ dissemination                                                                                                                                                                                                                                                                                             | 131                                    |

| 5.9                                 | Interference sources assumed in wake-up classifier model                                                                                                                                                                                                                                                                              | 132                                    |

| 5.10                                | Power-optimal wake-up classifier configuration                                                                                                                                                                                                                                                                                        | 134                                    |

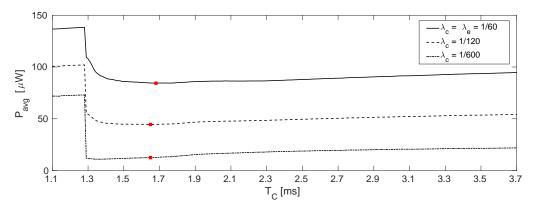

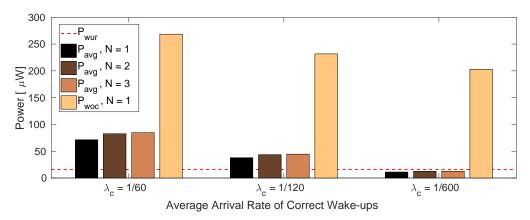

| 5.11                                | Average power dissipation of BLITZ with retransmissions                                                                                                                                                                                                                                                                               | 135                                    |

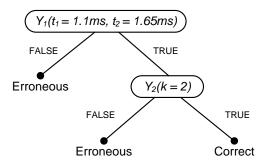

| 5.12                                | Decision tree of the selected power-optimal wake-up classifier                                                                                                                                                                                                                                                                        |                                        |

| 5.13                                | Decision tree of the selected power-optimal wake-up classifier                                                                                                                                                                                                                                                                        | 136                                    |

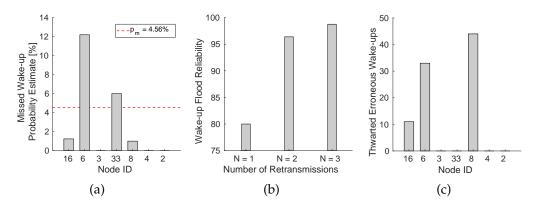

|                                     | Results of evaluating the power-optimal wake-up classifier                                                                                                                                                                                                                                                                            | 136<br>137                             |

| 5.14                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                 |                                        |

| <ul><li>5.14</li><li>5.15</li></ul> | Results of evaluating the power-optimal wake-up classifier                                                                                                                                                                                                                                                                            | 137                                    |

|                                     | Results of evaluating the power-optimal wake-up classifier Radio activity using eLWB for event dissemination                                                                                                                                                                                                                          | 137<br>139                             |

| 5.15                                | Results of evaluating the power-optimal wake-up classifier Radio activity using eLWB for event dissemination Radio activity using BLITZ for event dissemination                                                                                                                                                                       | 137<br>139<br>140                      |

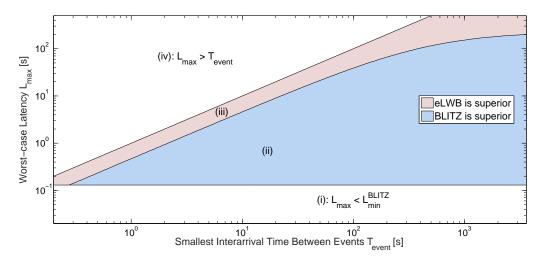

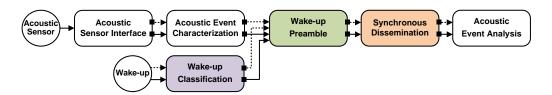

| <ul><li>5.15</li><li>5.16</li></ul> | Results of evaluating the power-optimal wake-up classifier Radio activity using eLWB for event dissemination Radio activity using BLITZ for event dissemination                                                                                                                                                                       | 137<br>139<br>140<br>141               |

| 5.15<br>5.16<br>5.17                | Results of evaluating the power-optimal wake-up classifier Radio activity using eLWB for event dissemination                                                                                                                                                                                                                          | 137<br>139<br>140<br>141<br>142        |

| 5.15<br>5.16<br>5.17<br>5.18        | Results of evaluating the power-optimal wake-up classifier Radio activity using eLWB for event dissemination Radio activity using Blitz for event dissemination Comparison between Blitz and eLWB protocols Logical components of acoustic monitoring system with Blitz Physical platform architecture and prototype supporting Blitz | 137<br>139<br>140<br>141<br>142<br>143 |

## **List of Tables**

| 2.1 | Summary of the timed automata in the Bolt system model           | 29  |

|-----|------------------------------------------------------------------|-----|

| 2.2 | Measured timing parameters of the Bolt system model              | 31  |

| 2.3 | Worst-case number of clock cycles for message operations         | 32  |

| 2.4 | Worst-case execution times for request and commit phases         | 33  |

| 2.5 | Bolt application programming interface                           | 36  |

| 3.1 | Power dissipation of state-of-the-art acoustic sensor interfaces | 56  |

| 3.2 | Parameterization of event-triggered components                   | 63  |

| 3.3 | eLWB parameters used in the FlockLab testbed experiments         | 75  |

| 3.4 | Power dissipation of each component during sleep state           | 77  |

| 3.5 | Average power dissipation with alternative configurations        | 78  |

| 4.1 | ZIPPY configuration used for all testbed experiments             | 107 |

| 5.1 | Discrete and continuous features for wake-up classification      | 127 |

| 5.2 | Performance metrics and relation to the confusion matrix         | 127 |

| 5.3 | Binary features used for the classification of wake-ups          | 128 |

| 5.4 | Parameterization of the wake-up classifier model                 | 134 |

| 5.5 | Parameterization of the eLWB and BLITZ analytical models         | 140 |

### Introduction

It is widely anticipated that the interaction of modern *cyber* technologies, i.e., computation and communication, with the *physical* world, will bring significant societal and economic benefits [RLSS10]. These *cyber-physical systems* promise automated monitoring and control of complex physical processes that govern a wide range of application domains including manufacturing, healthcare, agriculture, logistics and transportation [Lee08]. Consequently, cyber-physical systems are key technological enablers for the Industrial Internet of Things, also referred to as Industry 4.0, which is expected to revolutionize industrial automation toward smart products, smart production and smart services [WSJ17].

The definition of a cyber-physical system is concisely summarized by Lee et al. [LS16] as follows:

Cyber-physical systems are heterogeneous blends by nature. They combine computation, communication, and physical dynamics.

It is evident that these systems are constructed from many different types of components that combine to follow, and possibly influence, the dynamics of physical processes under observation. Computation is required to sense the state of the physical process, characterize the dynamics and determine appropriate actions, while communication is needed to collect the state of the physical process with high-spatial coverage and to close the feedback loop for automated control. While the communication between computing entities of cyber-physical systems may be wired, we focus on wireless technologies due to the potential for high spatial coverage without the high cost and cumbersome deployment associated with cabled systems.

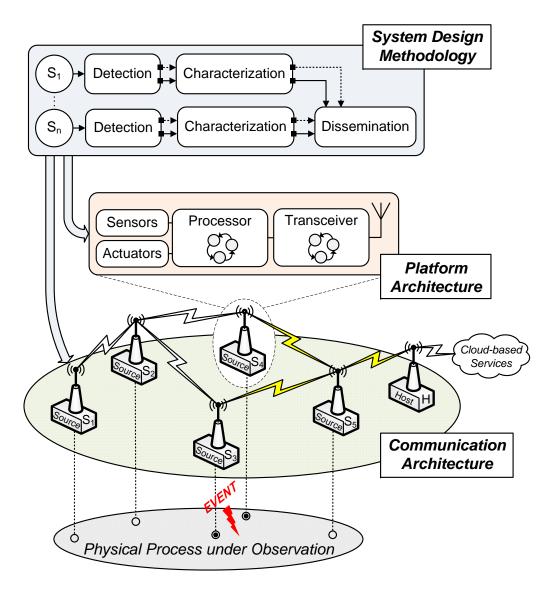

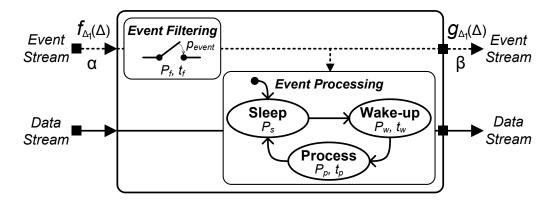

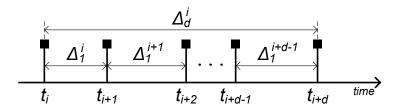

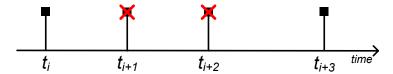

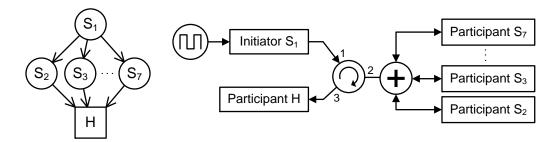

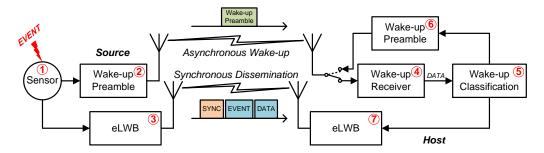

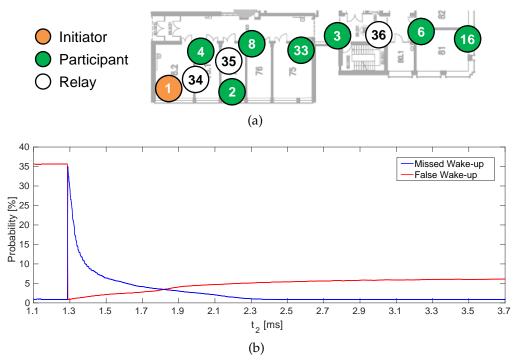

**Figure 1.1:** An overview of an event-triggered cyber-physical system, where a network of wireless embedded platforms monitors and controls a physical process. The platform architecture defines how the wireless embedded platforms are constructed, the communication architecture defines how platforms share information, and the system design methodology assists in the transformation of functional requirements of the system into an efficient implementation.

The realization of cyber-physical systems is, at least in part, a consequence of the past 15 years of research in the field of wireless sensor networks. This multi-disciplinary research community has produced an extensive collection of theoretical concepts and real-world deployments, as survey in [KW07, Amm14, OBR14], that relate to the sensing of physical processes coupled with wireless communication. The wireless sensing systems considered are typically *periodic*, in that the computation and communication entities are activated periodically according to a

specific duty cycle. However, the dynamics of many physical processes do not change periodically, but instead evolve in a non-deterministic manner. Therefore, in order to capture and possibly control these physical processes while conserving precious energy resources, the computation and communication of these cyber-physical systems must be *event-triggered*. That is, these cyber-physical systems monitor and react *on-demand* to non-deterministic events produced by the physical process.

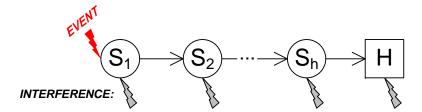

This thesis focuses on event-triggered cyber-physical systems using wireless communication, as depicted in Figure 1.1, where the goal of the system is to monitor and possibly control the dynamics of a physical process. A network of wireless embedded platforms, referred to as source nodes  $S_i$ , are responsible for detecting, characterizing and disseminating events to a host H for analysis. The host serves as a gateway to cloud-based services, which may also be used for application-specific event analysis. Each source node incorporates sensors to detect events, a processor to perform application-specific computations, a transceiver to communicate, and actuators to control the state of the physical process as instructed by the host.

When the state of the physical process under observation changes, an event is produced. Depending on the topology of the network, one or more source nodes detect the event, e.g., source nodes  $S_3$  and  $S_4$  as depicted in Figure 1.1. Once an event is detected, the source node collects additional information on the event so to determine its specific properties. The event, together with its characterization, are then disseminated through the multi-hop network to the host where application-specific analysis is performed. The host, possibly in conjunction with cloud-based services, decides on the appropriate response and instructs one or more source nodes to take action. For example, an event may be deemed inconsequential and all source nodes are instructed to return to an energy-saving mode, source nodes may be instructed to use additional sensing modalities to better characterize the event, or actuators may be activated in order to control the behavior of the physical process under observation.

The construction of an event-triggered cyber-physical system is defined by a *platform and communication architecture*, as represented in Figure 1.1. The platform architecture defines how each node is composed, i.e., how sensors, a processor, a transceiver and actuators are interconnected, while the communication architecture defines how a network of source nodes disseminate events and their associated data to the host over a wireless channel. Equipped with an platform and communication architecture, a *system design methodology* assists the system designer in transforming the functional requirements of an event-triggered cyber-physical system into an efficient implementation.

We next detail the system requirements of event-triggered cyberphysical systems, before detailing the specific challenges associated with achieving the desired requirements of the system. We then present an overview of the thesis contributions and how they address the challenges of realizing efficient event-triggered cyber-physical systems.

### 1.1 System Requirements

In order to realize the full potential of event-triggered cyber-physical systems, it is imperative that the following requirements are satisfied:

- In order to react quickly to the unpredictable dynamics of the physical process under observation, event-triggered cyber-physical systems must be *responsive*. The platform architecture must therefore support rapid detection and characterization of events, while the communication architecture must facilitate low-latency multi-hop dissemination from one or more source nodes to the host.

- Since wireless embedded platforms are typically battery powered, and may not necessarily have the opportunity for energy harvesting, event-triggered cyber-physical systems must be *energy-efficient*. This requires that both platform and communication architecture minimize energy consumption whenever possible in order to maximize the operational lifetime of the system.

- Due to the application-specific nature of wireless embedded platforms, a platform architecture must promote independent design and component-level re-use. Therefore, the platform architecture must facilitate the *composable* construction of wireless embedded platforms without adversely impacting responsiveness and energy efficiency.

- Given the inherent heterogeneity of physical processes, the eventtriggered cyber-physical system must be *adaptable* to changes in the environment. The platform and communication architectures must support on-demand resource and configuration updates, such as the on-demand activation of multi-modal sensors on multiple source nodes or the dynamic bandwidth allocation in response to a detected event.

- In an effort to simultaneously support responsiveness, energy-efficiency, composability and adaptability, a systematic system design methodology is needed to assist the system designer in transforming application-specific requirements into an efficient implementation.

### 1.2 Challenges

**System Design Methodology.** The design and implementation of event-triggered cyber-physical systems is difficult in practice due to the inherent complexity and the conflicting system requirements.

Event-triggered cyber-physical systems consist of a complex combination of analog, digital and software components. This system-wide complexity makes it difficult for a system designer to comprehend all component-level dependencies and how their unique trade-offs influence the performance of the overall system. For example, selecting a component that exhibits a low power dissipation at the cost of a long processing delay may satisfy the component-level requirements of energy efficiency, but based on the component dependencies, this may result in an increase of latency, thus violating the system requirement of responsiveness.

The system requirements of responsiveness, energy-efficiency and adaptability are in conflict with each other. To give a concrete example, we consider two approaches to designing an event-triggered cyber-physical The first is an always-on approach, where all components are active irrespective of whether an event is detected or not. resulting system is indeed responsive and adaptable, as all components are always on they exhibit a minimal response time, and consequently can be reconfigured at any moment. However, the system is not energyefficient, as significant energy resources are consumed regardless of whether an event is produced by the physical process under observation. An alternative is to use a duty-cycled/on-demand approach, where components of the system are only activated periodically or on-demand. The energy-efficiency of the system improves significantly, but adversely impacts responsiveness and adaptability, since components may not be active when an event or a configuration change occurs, or the time to activate components increases latency.

This combination of complexity and conflicting system requirements leads to an interesting dilemma for the system designer. On the one hand, the complex component dependencies make it difficult to perform appropriate component-level trade-offs, but on the other hand, performing these component-level trade-offs is the only way of balancing the conflicting system requirements. Therefore, there is a need for a systematic system design methodology that can introduce structure and use levels of abstraction to guide the system designer through these delicate component-level trade-offs and realize efficient event-triggered cyber-physical systems.

**Platform Architecture.** The typical wireless embedded platform used for wireless sensor network deployments consists of a single processor interfaced to sensors, actuators and a transceiver [SKK+12]. However, the increased processing demands on computation coupled with stringent real-time constraints on communication introduces resource interference. This means that the interleaved execution of sensing, actuation and communication tasks encounter resource interference with respect to time, power and clock domains.

This resource interference adversely impacts the performance of the platform in terms of responsiveness and energy-efficiency. For example, if an event is detected while the communication task is executing, the respective sensing and communication tasks will compete for resources, such as clock cycles, memory and peripherals. In such a scenario, either the delayed execution of the sensing task results in a delayed or missed event detection, or the stalled execution of the communication task impacts the reliability, and possibly the energy efficiency, of the communication protocol. Irrespective of the approach taken by highlevel software constructs, resource interference adversely impacts the responsiveness and energy efficiency of the system.

The emerging trend toward heterogeneous multi-processor platforms fails to circumvent the aforementioned resource interference problem. While shared busses or shared memory facilitate the transfer of information between processors, they still cause resource interference in the time, power and clock domains. Therefore, there is a need for a new platform architecture that takes advantage of processor heterogeneity and facilitates bi-directional information transfer between processors, while avoiding resource interference. As a consequence, application-specific wireless embedded platforms can be realized by composing independent computation and communication components, thereby promoting independent design and component-level re-use.

Communication Architecture. The past decade and a half of wireless sensor network research has produced a variety of energy-efficient multihop wireless communication protocols based on periodic communication, as surveyed in [HXS+13]. Multi-hop dissemination is achieved by coordinating nodes in the network to periodically communicate with their neighbors according to a duty-cycle, which may be statically defined at each node or dynamically initialized using network-wide synchronization techniques.

While this well-studied class of communication protocols has been successfully deployed in the field for multiple years with high reliability and energy-efficiency [BBF+11], this protocol class does however exhibit an undesirable trade-off between responsiveness and energy-efficiency.

That is, in the context of an event-triggered cyber-physical system, in order to reduce the latency of disseminating an event from any source node to the host, the duty-cycle of all nodes in the network must be increased, which results in an increase in energy consumption. In application scenarios where events are deterministic, these radio duty-cycled protocols can, at least in principle, be tuned to the periodicity of the dynamics of the physical processes under observation, and therefore provide low-latency dissemination without superfluous communication. However, when events occur non-deterministically, as is the case for event-triggered cyber-physical systems, significant energy is wasted as periodic communication proceeds regardless of an event being detected.

In order to provide responsive and energy-efficient dissemination of non-deterministic events, the undesirable trade-off between latency and energy efficiency exhibited by modern duty-cycled protocols must be circumvented. Therefore, there is a need for a new communication architecture that supports on-demand multi-hop communication that exhibits both low latency and energy efficiency.

#### 1.3 Thesis Outline and Contributions

In this thesis, we present a platform and communication architecture for the systematic design of efficient event-triggered cyber-physical systems. The main contributions are the following:

Chapter 2: Composable and Energy-efficient Wireless Embedded Platforms. We address the challenges of resource interference by proposing a new platform architecture that supports composable construction of energy-efficient wireless embedded platforms.

The proposed architecture separates computation and communication tasks onto dedicated processors. Information transfer between the two processors is facilitated by asynchronous message passing using Bolt, a processor interconnect with predictable run-time behavior. Predictable information transfer between processors is achieved by tightly bounding the worst-case execution time of Bolt message passing, as verified by formal methods, while decoupling the processors with respect to time, power and clock domains. The predictable run-time behavior of Bolt facilitates the composable construction of heterogeneous wireless embedded platforms, thereby promoting independent design and component-level re-use.

We present the design and prototype implementation of Bolt, which supports a message throughput of up to 3.3 Mbps and a negligible power overhead of 1.3  $\mu$ W during periods of inactivity.

Chapter 3: Design Methodology for Efficient Event-triggered Wireless Sensing Systems. We manage the inherent complexity and evaluate component-level trade-offs by utilizing a combination of well-established design principles together with a design guideline. The proposed four step design process guides the system designer toward an efficient realization of an event-triggered cyber-physical system subject to responsiveness, energy efficiency and adaptability design constraints.

The functionality of an event-triggered cyber-physical systems is first partitioned into a pipeline of logical event-triggered components. Each component is then represented by a logical model that encapsulates responsiveness, energy efficiency and adaptability design constraints, and adheres to an event-triggered interface specification. The design and implementation of each logical component is then performed in isolation using well-known design techniques with an appropriate design guideline. All components are then integrated onto a physical platform architecture, as presented in Chapter 2, without compromising the underlying design constraints.

We demonstrate the benefits of the proposed methodology by realizing a wireless acoustic emission sensing system, consisting of an acoustic sensor interface, an event characterization component and an event-based synchronous protocol termed the eLWB for multi-hop event dissemination. Experiments show that the prototype is capable of detecting an acoustic event with a delay of  $16 \,\mu\text{s}$ , starting to characterize an acoustic event with a delay of  $29 \,\mu\text{s}$ , and disseminating an acoustic event and its associated data over a multi-hop network with an average latency as low as  $113.2 \, \text{ms}$ , while dissipating a total of  $59.7 \,\mu\text{W}$  during periods of inactivity.

Chapter 4: On-demand Network Flooding. We demonstrate the first step toward low-latency and energy-efficient multi-hop communication by circumventing the fundamental trade-off exhibited by modern radio duty-cycled protocols. This is achieved through the design and implementation of an asynchronous flooding primitive for the rapid dissemination of rare events through a multi-hop network, which dissipates less than  $10 \,\mu\text{W}$  during periods of inactivity.

We present ZIPPY, an on-demand flooding protocol based on low-complexity radio hardware. ZIPPY takes advantage of the ultra-low power dissipation and unique timing properties of low-complexity receivers to achieve asynchronous network wake-up, fine-grained perhop synchronization, and efficient multi-hop dissemination of a small event packet to the host.

We detail the design, analysis and experimental evaluation of ZIPPY in a laboratory setting and in an indoor testbed. Experiments show that

ZIPPY supports on-demand flooding of a small event packet through a multi-hop network with an end-to-end latency as low as 24.4 ms for an 8-bit event packet through a 3-hop network, a per-hop synchronization as low as  $21.9 \,\mu\text{s}$ , and a power dissipation of  $9.6 \,\mu\text{W}$  during periods of inactivity.

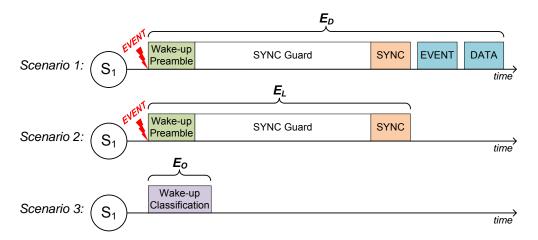

Chapter 5: Low Latency and Energy-efficient Event-triggered Wireless Communication. We combine the asynchronous network wake-up provided by ZIPPY, as presented in Chapter 4, with the synchronous event-based dissemination protocol eLWB, as presented in Chapter 3, to achieve multi-hop event dissemination with unprecedented latency and energy efficiency.

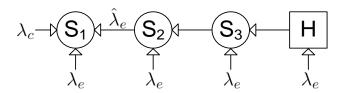

We present BLITZ, the first communication architecture that combines asynchronous and synchronous communication primitives to rapidly wake-up a multi-hop network, arbitrate network bandwidth, and disseminate events having variable bandwidth requirements on-demand. BLITZ takes advantage of ultra-low power wake-up receivers to wake-up all nodes by flooding wake-up preambles, and then proceeds with a synchronous flooding-based protocol for the arbitration of network resources and scheduling of contention-free time-slots for event and data dissemination. In addition, BLITZ integrates a novel classification technique for mitigating erroneous wake-ups, a fundamental limitation of ultra-low power wake-up receivers.

Using an analytical model, we show that BLITZ is more energy efficient and exhibits a lower worst-case latency compared to the eLWB for a wide range of event-triggered application scenarios. The analysis results also highlights that the combination of asynchronous and synchronous primitives, as used in BLITZ, yields superior latency and energy-efficiency compare to the eLWB for both rare and frequent events.

We design and implement a prototype of BLITZ by extending the wireless acoustic emission sensing system presented in Chapter 3. We experimentally evaluate the event-triggered cyber-phyical system in laboratory and testbed conditions. Experiments show that the developed prototype supports a mean latency as low as 108.9 ms for an 8-bit event packet and its associated data packet of 32 bytes through a 4-hop network, while dissipating  $16 \,\mu\text{W}$ , plus an additional  $3 \,\mu\text{W}$  for the acoustic sensor interface, during periods of inactivity.

## Composable and Energy-efficient Wireless Embedded Platforms

Increased processing demands and real-time constraints of modern wireless cyber-physical systems are driving a platform paradigm shift from classical single-processor motes toward heterogeneous multiprocessor platforms. These emerging platforms promise efficient concurrent processing with energy-proportional system performance. However, the use of shared interconnects and shared memory for interprocessor communication causes interference in the time, power, and clock domains. This prevents system designers from fully harnessing these benefits, since the inherent resource interference adversely impacts the responsiveness and energy efficiency of the platform, while hindering modular design and violating separation of concerns.

In this chapter, we address these platform limitations with Bolt, an ultra-low power processor interconnect that facilitates the composable construction of heterogeneous wireless embedded platforms. We present an architectural blueprint for interconnecting two independent processors, while enabling asynchronous inter-processor communication with predictable run-time behavior. We detail a prototype implementation of Bolt, and apply formal methods to analytically derive bounds on the execution time of its message passing operations. Experiments with a custom-built dual-processor platform demonstrate that the Bolt prototype exhibits predictable message passing with empirical bounds that match the analytical bounds to within a few clock cycles, achieves a high throughput of up to 3.3 Mbps, and incurs a negligible power overhead relative to state-of-the-art platforms.

#### 2.1 Introduction

In the early days of sensor networks, platforms featuring a single 8-bit or 16-bit microcontroller, such as Mica [HC02] and Telos [PSC05], spawned the development of a wide range of sense-and-send applications. These platforms offered modest computing resources well matched to the demands of low-rate sensing of physical parameters such as temperature, humidity, light, etc. Low-power operation was achieved by interleaving sensing, data processing, and communication tasks and by carefully managing the power state of hardware components.

Challenges. Although this design approach has been extensively followed to demonstrate the feasibility of wireless sensing applications, through our own experiences in designing, developing, and maintaining large-scale sensor network installations, we have encountered recurring patterns that impede the construction and performance of wireless embedded systems. We have observed that the engineering effort in realizing such systems is labor-intensive with respect to the design, test, and diagnosis of hardware and software components. While difficult to quantify, we argue that these practical complexities lead to implementations that are often unreliable, not readily adaptable to changing requirements, exhibit long development cycles, and are over-dimensioned to satisfy performance targets. This leads us to pose the following question: Why is it difficult to design such systems?

A careful analysis of existing wireless embedded platform architectures, in conjunction with a survey of the state-of-the-art in the embedded systems design literature, reveals that the main problem is rooted in the interference of hardware and software components in the time, power, and clock domains.

One may think that straightforward sense-and-send applications do not suffer from this problem. However, in these scenarios several tasks must execute concurrently, e.g., reading measurements from sensors, processing measurement data, and transmitting packets. Sense-and-react applications such as cyber-physical systems [SLMR05] additionally feature control and actuation tasks. These concurrent tasks interfere when they compete for shared resources such as clock cycles, memory, and peripherals. While labor-intensive engineering may partially handle such resource interference in highly deterministic scenarios, this approach is not only unsustainable in the long term, but also ineffective if tasks are triggered by unpredictable events, e.g., in surveillance or tracking application scenarios [ABC+04]. Furthermore, as the system load increases, the effects of resource interference increasingly affect the timing behavior of individual tasks, which in turn adversely impacts overall

system performance. Additional complexity is added to the system when incorporating power management techniques, which further exacerbates the problem.

Contributions. To address the above challenges, we advocate a novel approach to the construction of future wireless embedded platforms. We propose the functional separation of tasks onto a multiprocessor architecture whereby the tasks interact through asynchronous message passing using a processor interconnect with predictable timing characteristics. Predictability of the interconnect entails that passing a message takes a known, bounded time irrespective of the attached processors. As a result, the proposed architecture decouples processors in the time, power, and clock domains, facilitating the composable construction of customized wireless embedded platforms. Composability not only gives the system designer the flexibility to select hardware and software components satisfying the needs of the application, but also ensures that their interconnection does not change the properties of the integrated parts [Jan06]. Furthermore, predictability of the message passing interface is essential to meeting the performance requirements imposed by certain application domains or wireless standards with tight latency constraints.

This chapter presents Bolt, the first processor interconnect that enables the composable construction of energy-efficient wireless embedded Bolt provides predictable asynchronous communication between two arbitrary processors, and thus decouples the processors in the time, power, and clock domains. Bolt sits between both processors and hides all complexities associated with handling asynchronous message transfers from system developers, while dissipating only negligible power. Two message queues, one for each direction, with firstin-first-out (FIFO) semantics form the basis of this processor interconnect. A signaling protocol facilitates concurrent message reads and writes on both queues, and indicates when there is at least one message ready to be read out from a queue and when a queue is empty. The two message queues and all internal state reside in non-volatile memory, thus preserving the state of Bolt independent of the power states of the two processors. Bolt requires only a minimal software interface with welldefined semantics and predictable timing to be implemented on each processor. This concept of a processor interconnect allows designers to choose arbitrary off-the-shelf or custom processors and "bolt" them together to create a customized dual-processor platform while avoiding resource interference.

This chapter makes the following contributions:

• We present the design of Bolt and detail a prototype implementation

on a state-of-the-art low-power microcontroller.

- We apply formal methods to derive bounds on the worst-case execution time of Bolt's message passing operations.

- We detail Bolt's interface and how it should be used, before experimentally evaluating Bolt's performance with respect to power overhead, timing predictability and message throughput.

Using the presented Bolt prototype, we build a heterogeneous dual-processor platform consisting of a 32-bit ARM Cortex-M4 and a 16-bit TI system on chip. Extensive experiments with this platform demonstrate the following: (i) Bolt achieves power decoupling while incurring a negligible power overhead of  $1.3\,\mu\text{W}$  during periods of inactivity, (ii) the execution times of message passing operations exhibit empirical bounds that match the analytical bounds to within a few clock cycles, (iii) Bolt provides a high throughput of 1.5–3.3 Mbps for inter-processor messages that are 16–128 bytes in length, and (iv) Bolt enables the uninhibited concurrent execution of event-triggered sensing and wireless communication—a scenario that is complex, labor-intensive, and error-prone to implement on current wireless embedded platforms.

### 2.2 Background and Related Work

This section discusses the needs of low-power wireless embedded applications, the corresponding requirements on hardware and software components, and the problem of resource interference in state-of-the-art platform architectures.

#### 2.2.1 Classical Mote Architectures

In the early days of wireless sensor networks, there was substantial interest in new hardware and software architectures for sensor nodes. These so-called *motes* typically provide an interface to sensors/actuators, process and communicate data.

A wide variety of wireless embedded platforms have been developed both in industry and academia that explore different points of the design space, such as Cricket [PCB00], Mica [HC02], Iris [Cro], EYES [vHDHK03], Telos [PSC05], Imote [NKA+05], BTnode [Beu06], TinyNode [DFFMM06], Camazotz [JSK+13], and OpenMote [VTWP15]. Attempts towards adaptability at run-time often utilize multiple resources of the same type having different properties, e.g., multi-radio platforms like BTnode [BDH+04], Opal [JKK+11], OpenMote+ [TPVW16], and Firestorm [AFC16], platforms

with application-specific hardware acceleration like HaLoMote [EK16], and the concept of wake-up receivers [SBS02]. Both the platform architectures and the design principles used to realize them focused on finding the right trade-off between energy efficiency and the application-driven interfaces to sensors, computing and communication requirements, integration of state-of-the-art radios, small form factors, and autonomous operation [JHvdV+09].

#### 2.2.2 Requirements of Modern Platform Architectures

The field of distributed low-power wireless embedded systems has matured to a point where now serious applications of societal and economic importance are within reach, such as the Internet of Things (IoT), industrial process control and supervision, environmental and structural monitoring, smart logistics, personalized medicine, home automation, and traffic control. In many of these applications, measurements are precious and must not be lost [XRC+04], so data must arrive reliably and in real-time [HJT12, RGR07], responses are safety-critical [DGA+05], and deployment and maintenance of a network is labor-intensive and costly. Thus, it is inevitable that distributed low-power wireless embedded systems become a high-quality infrastructure with known and predictable properties.

The requirements for successful hardware and software architectures in these domains are also much better understood than in the early days of Smart Dust [KKP99]. Developing software for heavily resource constrained hardware platforms is known to be highly labor-intensive due to the tight coupling between functional and non-functional properties on the one hand and detailed hardware properties on the other. Despite advances in model-based design techniques, specific models of computation, intensive distributed testing and verification cycles, distributed low-power wireless embedded systems are still error-prone. To make matters worse, the final installations are often deployed into hostile environments that are unknown at design time and exhibit dynamically changing properties.

The application domains differ substantially in their requirements and hence a single platform does not suite them all with respect to computation, communication, memory resources, available energy budget, and degree of integration [AC14]. Nevertheless, we can identify two common trends of modern wireless embedded platforms:

Increasing Resource Demand. The program and data memory required to implement even seemingly straightforward functionality has grown significantly. Similar observations hold for the required

computational resources that very often cannot be fulfilled by the 8-bit or 16-bit microcontrollers that were employed in the first generation of motes.

Need for Adaptability. Application tasks such as sensing, actuation, computation, and communication are highly dependent on the occurrence of events, e.g., from sensor and radio interfaces, and the availability of energy. The same holds for the associated modes of operation such as radio states, microcontroller power modes, duty cycle, and clock frequency.

One of the early attempts to increase the amount of available resources was the Imote2 [NHS+08], at the cost of high sleep currents limiting its use in energy-constrained settings. More recently, there are new MCU generations appearing on the market that combine low sleep currents, short wake-up times, and rich peripherals with a relatively high compute power, such as the ARM Cortex-M family [ARM] used in products from Texas Instruments, NXP, ST Microelectronics, Silabs, Freescale, and Atmel. However, their availability only solves part of the problem inherent to classical mote architectures. Highly adaptive and event-triggered application tasks with widely varying resource requirements interfere on shared resources, and therefore violate the principles of modularity and separation of concerns.

To illustrate this resource interference problem, let us consider an application that requires high-rate sampling of sensors, for example, acoustic sensors in a structural monitoring application [XRC+04]. Due to the fact that the single processing resource, the microcontroller, also needs to handle time-critical events from the wireless communication component, the available computational resources may not be sufficient and interference between tasks is inevitable. As a second example, suppose an application requires a node to react quickly to events, for example, to quickly update an actuator or to localize signal sources depending on the pairwise differences in the arrival of events at different nodes. Again, limited resources and interference on the single processing resource lead to unpredictable behavior in such adaptive scenarios. This kind of resource interference can only be partially hidden by software abstraction layers, e.g., as provided by TinyOS [LMP+05] and Contiki [DGV04], leading to fragile, monolithic, and over-provisioned systems that are tedious to design, implement, debug, and maintain.

### 2.2.3 Modular Multi-processor Platform Architectures

In order to address some of the aforementioned deficiencies, modular platform architectures have been proposed that can be adapted to the needs of various application domains. Examples of such platforms include the 4-layer modular architecture in [PDCDLTR06], the MIT Media Lab modular platform [BP05], the stackable architecture [OBD+05], Epic [DC08], PowWow [BS10], and IHPstack mote [SGG12]. In all of these designs, components communicate via a shared bus or a set of shared standard interconnects such as UART, I2C, SPI, and 1-wire. Novel shared interconnects, such as the M-bus [KPK+14], have been specifically designed for ultra-low power connectivity.

The need for heterogeneous systems consisting of multiple components that dynamically match resources to the specific task at run-time, e.g., sleep modes, clock configuration, voltage scaling, and component deactivation, has been recognized by other communities as well, especially in the area of mobile communications. As a consequence, we increasingly see commercially available designs combining heterogeneous resources for ultra-low power applications, such as the LPC4300 [NXP] from NXP, and the VF3xxR and MKW2xDx [Fre] from Freescale. All these designs use bus-based interconnects or shared-memory communication between the components. One notable exception is the TI F28M3x series [Tex], which is specifically designed for application domains requiring safety certifications. Instead of relying exclusively on shared resources for communication, it contains a FIFO buffer for conflict-free communication at the cost of not being designed for ultra-low power operation.

It has been recognized that whenever multiple resources communicate, the use of shared busses and shared memory seriously hampers modularity [KdNA+14]. The major obstacle for application domains with high dependability and safety requirements, such as automotive and avionics, in adopting multi-core and multi-resource platforms is the inevitable interference on shared resources [KNP+13]. Thus, there is currently no accepted path to certification, which requires guarantees on correct timing and functionality [WGR+09].

The main consequences of using shared memory or shared busses for communication among components are the following:

• Coupling of Power and Clock Domains. To reach the goal of energy-proportional performance, where the energy consumed grows with the amount of useful task execution performed, systems use different power and clock domains. However, a shared bus couples these domains and requires tight coordination of power and clock management. As a result, the principles of separation of concerns and isolation of independent functionalities are violated, and power management requires the interaction of many hardware and software layers [AC14]. As a rule, unnecessary interference and dependencies introduced on the hardware layer can rarely be

decoupled by means of higher-level software constructs.

• Interference in the Time Domain. Using shared memory, constructs like semaphores and locks allow for mutually exclusive access to shared resources. However, they also make the timing of activities on one resource dependent on that of activities on another resource, seriously violating composability and the possibility of independent design. In other words, the system must be redesigned for each newly introduced task. Similarly, the bus as a shared communication medium causes timing interference, leading to highly pessimistic timing bounds, e.g., when using protocols like first-come-first-serve, fixed priority, round-robin, or inefficient communication, e.g., when using partitioned protocols like TDMA or time-triggered architecture [KB03].

Due to these deficiencies, alternatives like distributed memory, asynchronous message passing, and queue-based communication are all well understood in their underlying concepts and widely used in distributed systems, multi-processor systems, and networks on chip [JT03, HGBH09]. However, these concepts have not yet been thoroughly investigated in the context of energy-efficient wireless embedded platforms. This chapter aims to fill this gap.

# 2.3 Design of Bolt

We introduce Bolt, a novel processor interconnect for energy-efficient wireless embedded systems. By providing bidirectional asynchronous message passing with predictable message transfer times, Bolt is a key building block for the communication between components on emerging dual-processor platforms to support energy-efficient applications with high processing demands and stringent timing constraints. Bolt simplifies the design of such applications by completely eliminating, or at least limiting, the interference among different hardware and software components on shared resources. As such, Bolt promotes a paradigm shift toward the composable construction of energy-efficient heterogeneous wireless embedded platforms.

#### 2.3.1 Overview

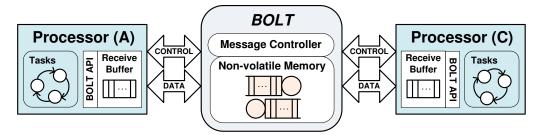

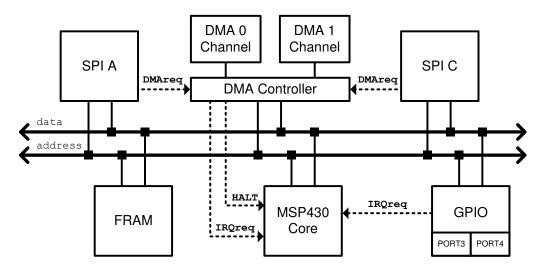

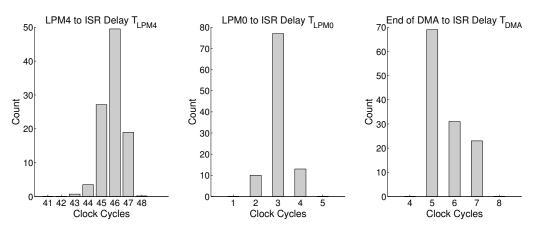

As depicted in Figure 2.1, Bolt is a piece of integrated hardware and software that sits between two processors A and C. Bolt lets processors A and C asynchronously exchange messages while executing within their

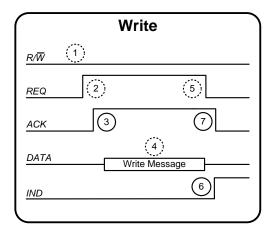

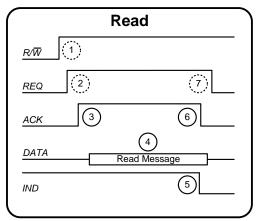

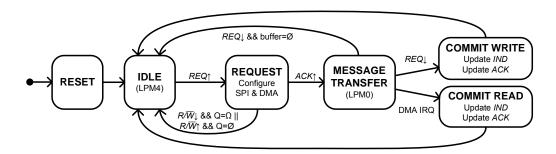

**Figure 2.1:** Overview of the Bolt processor interconnect. Bolt decouples processors A and C in time, power, and clock domains through predictable bidirectional asynchronous message passing.

own time, power, and clock domains. This ensures that each processor can independently write messages into Bolt or read messages out of Bolt. We design and implement Bolt in such a way that the execution time of read and write operations can be tightly bounded. Based on these bounds, we conceive a well-defined software interface by which each processor accesses Bolt in a non-blocking manner to exchange messages of variable length and possibly with different priorities.

The unique properties of Bolt allow for composable system designs. That is, a system designer can choose any two commercially available processors and existing software artifacts and integrate them to create a customized platform that satisfies the application needs, without changing the properties of the integrated parts. These parts can be separately designed, implemented, and validated, thus leading to modular systems that are easier to develop, understand, and maintain.

The key to achieving these advantageous properties is to tackle the problem of interference between different hardware and software components on shared resources. To solve this problem, we take a novel approach that is guided by the following established embedded systems design principles [HS07, Sif13]:

- (1) Try to avoid resource interference.

- (2) If resource interference is unavoidable, try to tightly bound it.

- (3) Specify a formally verified interface with predictable properties.