Departement Informationstechnologie & Elektrotechnik Professur für Technische Informatik Professor Dr. Lothar Thiele

#### Andri Kofmehl Javier Coedo

# Evaluation von Arbitrierungsschemen in Netzwerkprozessoren

Diplomarbeit DA-2003.17 Wintersemester 2002/2003

Betreuer: Simon Künzli Samarjit Chakraborty

Verantwortlicher: Prof. Dr. Lothar Thiele

# Kurzfassung

In den Netzknoten des Internets werden zur Verarbeitung der Paketströme speziell konzipierte Prozessoren eingesetzt. Diese Netzwerkprozessoren sind einerseits auf typische Anwendungen zugeschnitten, bieten aber gleichzeitig ein hohes Mass an Flexibilität. Sie werden aus mehreren Prozessor-, Speicher- und Kommunikationseinheiten kombiniert und als Gesamtsystem auf einem Chip integriert. Den prozessorinternen Datenaustausch unter den Verarbeitungseinheiten kann ein schneller Bus übernehmen. Bei hohem Datenaufkommen wird dieser stark ausgelastet, womit das Scheduling auf Busebene, die sogenannte Arbitrierung, an Bedeutung gewinnt.

In dieser Arbeit wird das Problem der Arbitrierung anhand einer Beispiel-Prozessorarchitektur analysiert und mit Hilfe von Simulationen genauer untersucht. Es zeigt sich, dass die Wahl des Arbiters entscheidend an der resultierenden Prozessorleistung beteiligt ist und überdies auch bei der Einhaltung von Quality-of-Service-Vorgaben eine wichtige Rolle spielt. In diesem Sinne wurden Konzepte ausgearbeitet, welche Paketscheduling und Busarbitrierung kombinieren und als Instrument für den Entwurf und die Konfigurierung moderner Netzwerkprozessoren dienen können. Die erwarteten Vorteile wurden durch Simulationen bestätigt.

# Inhaltsverzeichnis

| Kurzfassung 3 |                               |                   |                                                        |           |    |  |  |

|---------------|-------------------------------|-------------------|--------------------------------------------------------|-----------|----|--|--|

| 1             | Einleitung                    |                   |                                                        |           |    |  |  |

|               | 1.1                           | Netzw             | rerkprozessoren                                        | 3         |    |  |  |

|               |                               | 1.1.1             | Geschichtliches                                        | 3         |    |  |  |

|               |                               | 1.1.2             | Aufgaben eines Netzwerkprozessors                      | 4         |    |  |  |

|               |                               | 1.1.3             | Moderne Netzwerkprozessoren                            | 5         |    |  |  |

|               | 1.2                           | Projek            | ctüberblick                                            | 5         |    |  |  |

| 2             | Net                           | zwerkj            | prozessor-Simulator                                    | 7         |    |  |  |

|               | 2.1                           | Refere            | enz-Architektur                                        | 7         |    |  |  |

|               | 2.2                           | Model             | labstraktion                                           | 8         |    |  |  |

|               | 2.3                           | Komp              | onenten-Modell                                         | 9         |    |  |  |

|               |                               | 2.3.1             | Busarchitektur                                         | 9         |    |  |  |

|               |                               | 2.3.2             | Ethernet-Block (EMAC)                                  | 10        |    |  |  |

|               |                               | 2.3.3             | PLB-OPB-Brücke                                         | 11        |    |  |  |

|               |                               | 2.3.4             | Speicher                                               | 13        |    |  |  |

|               |                               | 2.3.5             | Prozessor-Block                                        | 14        |    |  |  |

|               |                               | 2.3.6             | Zusammenfassung                                        | 17        |    |  |  |

|               | 2.4                           | terte Architektur | 19                                                     |           |    |  |  |

|               |                               | 2.4.1             | Multiprozessoreinheit                                  | 20        |    |  |  |

|               |                               | 2.4.2             | Direct Memory Access Controller                        | 22        |    |  |  |

|               | 2.5                           | Matla             | b-Simulation                                           | 23        |    |  |  |

| 3             | Bus                           | -Arbit            | rierung                                                | <b>25</b> |    |  |  |

|               | 3.1                           | Defini            | tion des Arbiters                                      | 25        |    |  |  |

|               | 3.2 Konzepte zur Arbitrierung |                   |                                                        |           | 26 |  |  |

|               |                               | 3.2.1             | Beispiele von Arbitern                                 | 27        |    |  |  |

|               |                               | 3.2.2             | Prioritäts- oder Bandbreiten-orientierte Algorithmen . | 29        |    |  |  |

|               |                               | 3.2.3             | Mehrstufige Arbitrierung                               | 30        |    |  |  |

|               | 3.3                           | Arbitr            | rierung im Netzwerkprozessor                           | 30        |    |  |  |

|               |                               | 3.3.1             | Ausgangslage                                           | 30        |    |  |  |

|               |                               | 3.3.2             | PLB-Verkehr                                            | 31        |    |  |  |

|   |                          | 3.3.3                                                                    | Systemkapazität und -dimensionierung                                                                                                                                                                              | 33                                                       |

|---|--------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

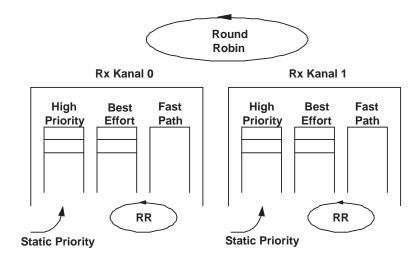

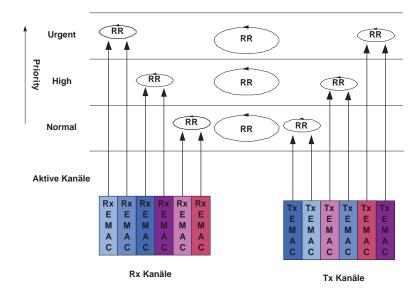

|   |                          | 3.3.4                                                                    | Warteschlangen und Scheduler                                                                                                                                                                                      | 36                                                       |

|   |                          | 3.3.5                                                                    | Bedeutung von Arbitrierung und Scheduling                                                                                                                                                                         | 37                                                       |

|   | 3.4                      | Szena                                                                    | rio I: Minimierung der Paketverzögerung                                                                                                                                                                           | 42                                                       |

|   |                          | 3.4.1                                                                    | Ausgangslage                                                                                                                                                                                                      | 42                                                       |

|   |                          | 3.4.2                                                                    | Scheduling                                                                                                                                                                                                        | 42                                                       |

|   |                          | 3.4.3                                                                    | Arbitrierung                                                                                                                                                                                                      | 43                                                       |

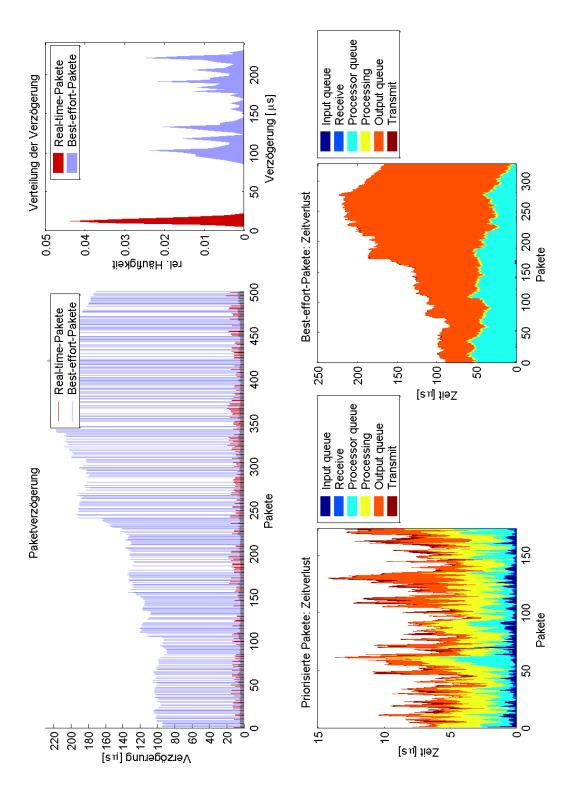

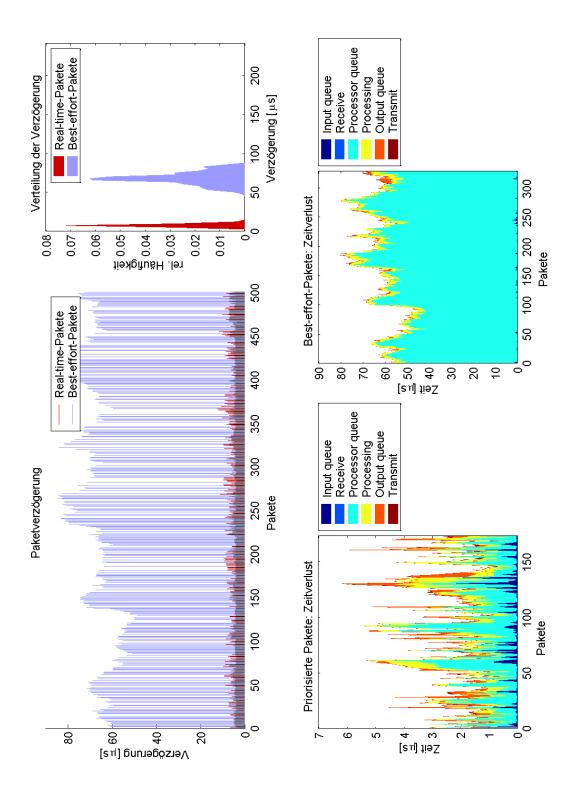

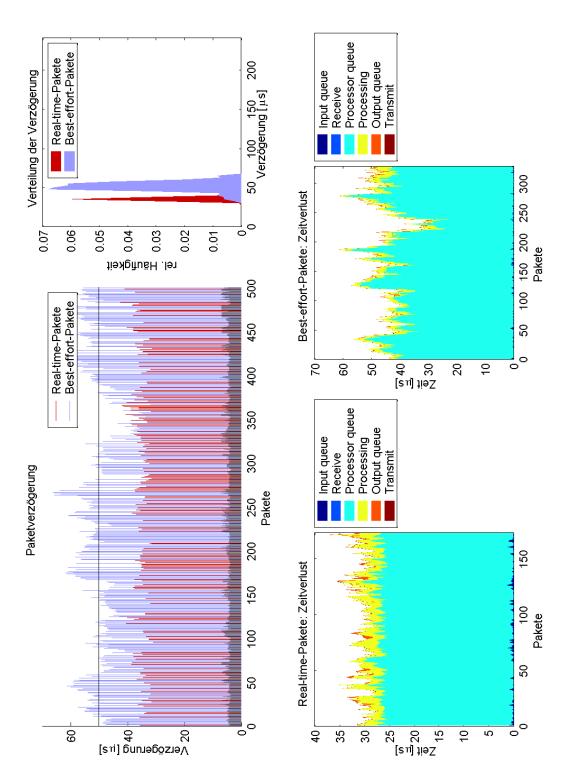

|   |                          | 3.4.4                                                                    | Simulationsergebnisse                                                                                                                                                                                             | 44                                                       |

|   |                          | 3.4.5                                                                    | Schlussfolgerungen                                                                                                                                                                                                | 47                                                       |

|   | 3.5                      | Szena                                                                    | rio II: Best-effort-Optimierung bei gleichzeitigem Real-                                                                                                                                                          |                                                          |

|   |                          | time-V                                                                   | Verkehr                                                                                                                                                                                                           | 52                                                       |

|   |                          | 3.5.1                                                                    | Ausgangslage                                                                                                                                                                                                      | 52                                                       |

|   |                          | 3.5.2                                                                    | Scheduling                                                                                                                                                                                                        | 52                                                       |

|   |                          | 3.5.3                                                                    | Arbitrierung                                                                                                                                                                                                      | 55                                                       |

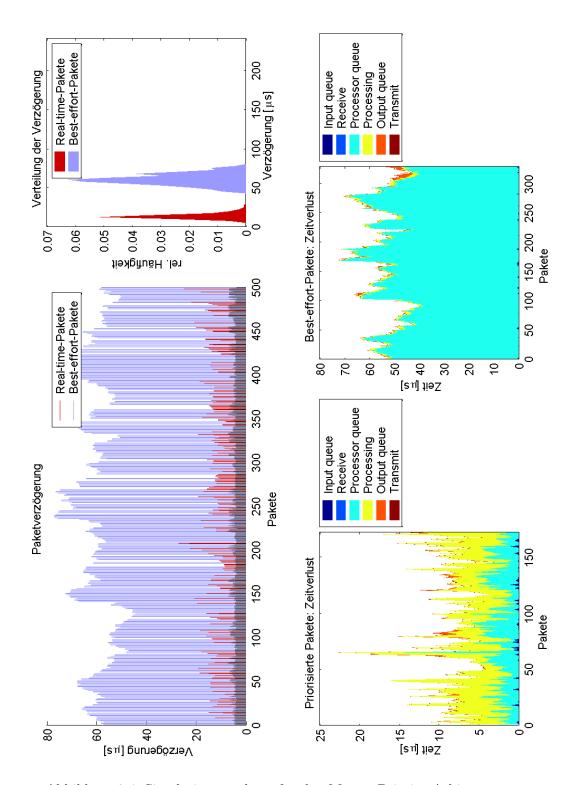

|   |                          | 3.5.4                                                                    | Simulationsergebnisse                                                                                                                                                                                             | 56                                                       |

|   |                          | 3.5.5                                                                    | Schlussfolgerungen                                                                                                                                                                                                | 58                                                       |

|   |                          |                                                                          |                                                                                                                                                                                                                   |                                                          |

| 4 | Soft                     | tware-l                                                                  | Dokumentation                                                                                                                                                                                                     | 61                                                       |

| 4 |                          |                                                                          | Dokumentation<br>nC-Simulator                                                                                                                                                                                     | <b>61</b>                                                |

| 4 | 4.1                      | Syster                                                                   | mC-Simulator                                                                                                                                                                                                      | 61                                                       |

| 4 |                          | Syster<br>Multij                                                         | mC-Simulator                                                                                                                                                                                                      | 61<br>62                                                 |

| 4 | 4.1<br>4.2               | Syster<br>Multip<br>4.2.1                                                | nC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66                                           |

| 4 | 4.1                      | Syster<br>Multip<br>4.2.1<br>Direct                                      | nC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67                                     |

| 4 | 4.1<br>4.2               | Syster<br>Multip<br>4.2.1<br>Direct<br>4.3.1                             | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68                               |

| 4 | 4.1<br>4.2<br>4.3        | Syster<br>Multip<br>4.2.1<br>Direct<br>4.3.1<br>4.3.2                    | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71                         |

| 4 | 4.1<br>4.2               | Syster<br>Multip<br>4.2.1<br>Direct<br>4.3.1<br>4.3.2<br>Arbiti          | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71<br>74                   |

| 4 | 4.1<br>4.2<br>4.3        | Syster<br>Multip<br>4.2.1<br>Direct<br>4.3.1<br>4.3.2<br>Arbita<br>4.4.1 | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71<br>74<br>74             |

| 4 | 4.1<br>4.2<br>4.3        | Syster Multip 4.2.1 Direct 4.3.1 4.3.2 Arbitr 4.4.1 4.4.2                | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71<br>74<br>74             |

| 4 | 4.1<br>4.2<br>4.3        | Syster<br>Multip<br>4.2.1<br>Direct<br>4.3.1<br>4.3.2<br>Arbita<br>4.4.1 | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71<br>74<br>74             |

|   | 4.1<br>4.2<br>4.3<br>4.4 | Syster Multip 4.2.1 Direct 4.3.1 4.3.2 Arbitr 4.4.1 4.4.2 4.4.3 4.4.4    | mC-Simulator prozessormodell Prozessor-Anfragen Memory Access Controller (DMA) PLB-OPB-Brücke DMA-Modul rierung und Scheduling Prozessor-Scheduling Input- und Output-Scheduling PLB-Arbitrierung Verkehrsklassen | 61<br>62<br>66<br>67<br>68<br>71<br>74<br>74<br>76<br>77 |

| 5 | 4.1<br>4.2<br>4.3<br>4.4 | Syster Multip 4.2.1 Direct 4.3.1 4.3.2 Arbitr 4.4.1 4.4.2 4.4.3 4.4.4    | mC-Simulator                                                                                                                                                                                                      | 61<br>62<br>66<br>67<br>68<br>71<br>74<br>74<br>74       |

### Kapitel 1

# Einleitung

Das Internet bietet heute eine Vielzahl von Kommunikationsdiensten an. In den letzten Jahren wurden neue Anwendungen eingeführt, wie zum Beispiel E-Commerce, Video-on-Demand oder Voice-over-IP. Solche Anwendungen haben hohe Dienstgüteanforderungen an das Netzwerk. Die Dienstgüte (Quality-of-Service, QoS) eines Netzes wird normalerweise durch unterschiedliche technische Parameter wie Durchsatz, Verzögerung, Verzögerungsschwankungen (Jitter) und Paketverlustrate charakterisiert [1]. Obwohl sich das Internet im ununterbrochenen Wachstum hinsichtlich der Anzahl Hostrechner, der Vielfalt der Anwendungen und der Kapazität der Verbindungen befindet, bleibt seine Architektur gegenüber seinen frühen Tagen weitgehend unverändert. Das Internet funktioniert als Netzwerk, in welchem Daten in Form einzelner Pakete übertragen werden. Eine maximale Verzögerung der Pakete kann nicht garantiert werden und im Falle von Überlastung können Pakete sogar verloren gehen. Man spricht von einem Best-effort-Dienst. Diese Unzuverlässigkeit des Internet steht nicht im Einklang mit neuen Diensten, welche Qualitätsgarantien benötigen. Die Übertragung von Video- oder Audiodatenströmen beispielsweise kann unbefriedigend ausfallen.

Mit der schnellen Wandlung des Internet in eine kommerziell genutzte Infrastruktur hat sich die Nachfrage nach Mechanismen, welche Qualitätsgarantien bieten, erhöht. Es gibt verschiedene Ansätze mit dem Ziel, QoS im Internet zu unterstützen. Die Internet Engineering Task Force (IETF) [2] hat zu diesem Zweck zwei Modelle entwickelt: Integrated Services (IntServ) [3] und Differentiated Services (DiffServ) [4]. Beide Ansätze basieren auf der Annahme, dass die Bandbreiten-Nachfrage in einer oder mehreren Lokalitäten des Netzes das Angebot übersteigt und somit irgendeine Art von Ressourcen-Reservierung zur Sicherung einer bestimmten Dienstqualität durchgeführt werden muss. Es gibt Stimmen, welche die Notwendigkeit solcher Mechanismen anzweifeln. So wird argumentiert, dass dank moderner Technologien,

wie Wellenlängen-Multiplex (DWDM, Dense Wavelength Division Multiplexing), Bandbreite in Zukunft so reichlich und preiswert vorhanden sein werde, dass die benötigte Dienstgüte automatisch gegeben sei [13]. In der Tat bietet ein einziges Glasfaserkabel eine Bandbreite von 25 bis 30 THz an und ermöglicht damit Übertragungsraten von einigen Terabits (10<sup>12</sup> Bits) pro Sekunde. Theoretisch könnten damit alle Telefongespräche, die weltweit zur selben Zeit geführt werden, problemlos durch ein einziges Glasfaserkabel übertragen werden [5]. Es bleibt aber zu bedenken, dass egal wie viel Bandbreite das Internet jemals zur Verfügung stellt, diese von neuen Anwendungen verwendet werden wird. Folglich werden Mechanismen zur Sicherung der QoS auch in Zukunft erforderlich sein.

Um Dienstgüte im Internet zu garantieren, müssen Betriebsmittel des Netzwerks reserviert werden können. Betriebsmittel sind Netzwerkressourcen wie Bandbreite, Pufferspeicher oder Rechenleistung. Sobald im Netz eine momentane Überlast besteht, werden die Ressourcen gemäss Reservierung den entsprechenden Paketströmen zugewiesen, womit für leistungskritische Anwendungen die verlangte Dienstgüte aufrechterhalten werden kann. Es sind dazu effiziente Scheduling-Mechanismen erforderlich, welche die Abarbeitungsreihenfolge der Pakete in den Netzwerkknoten regeln, und die Betriebsmittel unter den Paketströmen aufteilen.

Scheduling-Algorithmen werden allgemein dazu verwendet, eine Ressource gemäss einer definierten Zielfunktion zu verwalten. Sie treten in verschiedenen Schichten des OSI-Referenzmodells auf. In der Literatur wird das Scheduling-Problem zumeist auf der Netzwerkschicht betrachtet, d.h. es wird untersucht, wie Paketswitches die Verbindungen verwalten sollen (Link Scheduling). Im Sachen Link Scheduling wurde bereits sehr viel Forschung betrieben [7, 8, 9]. So sind am Institut für Technische Informatik der ETH Zürich mehrere Scheduling-Algorithmen entwickelt und publiziert worden, welche eine theoretisch garantierte Performanz aufweisen, wie beispielsweise [6].

Die vorliegende Arbeit beschäftigt sich mit Scheduling-Verfahren für Kommunikationsbusse in Netzwerkprozessoren. Im Falle von Bussen spricht man in der Regel nicht mehr von Scheduling, sondern von Arbitrierung. In der Industrie herrscht die Ansicht vor, dass die Arbitrierung nur eine untergeordnete Rolle spielt. Ziel dieser Arbeit ist es den Einfluss der Arbitrierung auf die Leistung des Netzwerkprozessors aufzuzeigen sowie Lösungen zu erarbeiten, welche die Einhaltung von QoS-Vorgaben unterstützen.

#### 1.1 Netzwerkprozessoren

Ein Netzwerkprozessor ist ein ASIP (Application Specific Instruction Set Processor), welcher auf die Klasse von Netzwerkanwendungen zugeschnitten ist. Netzwerkprozessoren können aus mehreren Rechen-, Kommunikationsund Speichereinheiten auf einem einzigen Chip bestehen. Dies wird als Systemon-a-Chip (SoC) bezeichnet. Recheneinheiten können Mikroprozessor-Blöcke, Micro-Engines oder dedizierte Hardware-Komponenten für spezielle Paketverarbeitungsfunktionen sein. Als Kommunikationseinheiten werden Busse oder Crossbars eingesetzt.

#### 1.1.1 Geschichtliches

Paketswitches der ersten Generation bestanden aus einem PC mit mehreren Netzwerkkarten. Die Pakete wurden über den Systembus in den Hauptspeicher geladen und danach von einem General Purpose Prozessor (GPP) bearbeitet. Als nach und nach Netzwerkgeschwindigkeit und -dichte zunahmen, konnte diese einfache Architektur den steigenden Anforderungen nicht mehr gerecht werden. Leistungsbegrenzend konnten alle Komponenten sein: General Purpose Prozessoren, die Pakete nicht genug schnell bearbeiteten, Hauptspeicher mit zu langen Zugriffszeiten oder Systembusse mit mangelnder Kapazität.

Um diesen Problemen entgegenzuwirken, wurden in der nächsten Generation von Paketswitches Hochgeschwindigkeitsbusse eingesetzt und die Funktionalität wurde in Hardware, auf Basis von ASICs (Application Specific Integrated Circuits) oder FPGAs (Field Programmable Gate Arrays) implementiert. Um die Leistung noch weiter zu erhöhen, wurden gewisse Aufgaben, die in den ersten Paketswitches zentral vom GPP erledigt worden waren, auf die Netzwerkkarten übertragen. Heute werden intelligente Netzwerkkarten eingesetzt, welche über Speicher verfügen und zusätzliche Aufgaben wie das Routing übernehmen. In einem weiteren Schritt wurde der gemeinsame Bus durch ein Durchschaltnetzwerk (Switch Fabric) ersetzt [10]. Diese Architekturen sind auf Leistungssteigerung hin entwickelt und optimiert worden. Sie haben aber den entscheidenden Nachteil, dass sie sehr unflexibel sind. Wie bereits erwähnt, sehen wir heute im Internet eine Entwicklung in Richtung bandbreitenintensive und verzögerungssensitive Anwendungen. Damit das Internet diese neuen Aufgaben gut erfüllen kann, müssen unter anderem neue Protokolle unterstützt werden.

Während also auf der einen Seite möglichst verzögerungsarme Übertragung und möglichst grosser Durchsatz gefordert sind, wird auf der anderen Seite die Flexibilität und die Möglichkeit schneller Anpassungen immer wichtiger. Performanz und die Flexibilität sind gegenläufige Entwurfsziele, sie bilden einen sogenannten Trade-Off. Das bedeutet, dass nie beide zugleich maximiert werden können. Im Bemühen, einen Kompromiss zwischen diesen beiden Entwurfsrichtungen zu finden, wurden die Netzwerkprozessoren geboren. Netzwerkprozessoren vereinigen Vorteile beider oben erwähnten Ansätze, nämlich einerseits die Programmierbarkeit von General Purpose Prozessoren und anderseits die Schnelligkeit von ASICs.

#### 1.1.2 Aufgaben eines Netzwerkprozessors

Da Netzwerkprozessoren speziell für Netzwerke entwickelt sind, liegt es nahe sich zuerst der Aufgaben in einem heterogenen Netzwerk, das aus vielen Teilnehmern besteht, bewusst zu werden. Gemäss [14] lassen sich alle Netzwerkanwendungen in folgende Kernprozesse aufteilen:

- Pattern Matching. Unter Pattern Matching versteht man die Aufgabe, bestimmte Bitmuster in Datenpaketen zu finden. Man vergleicht bei diesem Prozess immer das Datenpaket gegen einen regulären Ausdruck. Das Ergebnis einer solchen Operation ist ein Boolescher Wert, der angibt, ob der gesuchte Ausdruck im Datenpaket enthalten ist.

- Lookup. Als Lookup bezeichnet man die Aufgabe, in einer Datenbank nach einem bestimmten Schlüssel zu suchen. Diese Funktion wird oft in Verbindung mit Pattern Matching benötigt. Eine Beispielanwendung ist die Suche nach dem richtigen Ausgangsport eines Datenpakets in einer Routing-Tabelle.

- Computation. Als Computation bezeichnet man die Aufgabe, für ein Datenpaket einen bestimmten Wert zu berechnen. Dafür gibt es verschiedenste Möglichkeiten. Zum Beispiel muss für die meisten Protokolle eine Prüfsumme bestimmt werden. Diese Werte müssen immer dann neu berechnet werden, wenn sich Werte im Header von Datenpaketen ändern.

- Data Manipulation. Unter Data Manipulation versteht man alle möglichen Aufgaben, die in einem Datenpaket Werte verändern. Dies sind zum Beispiel beim Internet-Protokoll die Dekrementierung des Time-to-Live-Felds, das Einfügen von Sequenznummern bei der Fragmentierung von Paketen bzw. das Zusammenfügen dieser Pakete.

- Queue Management. Unter Queue Management wird das Verwalten von Warteschlangen verstanden. Dies beinhaltet das Scheduling und die Speicherung von ankommenden und abgehenden Paketen. Dieser Prozess ist auch zuständig für das Einhalten von Dropping- und Traffic-Shaping-Regeln in QoS-bezogenen Applikationen.

• Control Processing. Unter Control Processing versteht man verschiedene Aufgaben, welche nicht mit Linkgeschwindigkeit durchgeführt werden müssen. Beispiele dafür sind das Aktualisieren von Tabellen und Statistiken sowie die Behandlung von Ausnahmen.

#### 1.1.3 Moderne Netzwerkprozessoren

Netzwerkprozessoren unterliegen wie alle Systeme gewissen Anforderungen. Um Leistungskriterien zu erfüllen, werden Hochgeschwindigkeitsbusse oder spezielle Kommunikationseinheiten, z.B. Crossbars, eingesetzt, welche die unterschiedlichen Komponenten miteinander verbinden. Ausserdem werden mehrere Recheneinheiten bereitgestellt, die ein Paket parallel oder in einem Pipeline-Modus verarbeiten. Dadurch lässt sich die Leistung eines Netzwerkprozessors erheblich steigern. Zum Beipspiel ist der IBM PowerNP NP2G ein Netzwerkprozessor, der 12 Pikoprozessoren, einen eingebetteten PowerPC und mehrere Hardware-Beschleuniger vereinigt [15]. Um ein weiteres Beispiel zu nennen, sei hier Intels Netzwerkprozessor IXP2850 aufgeführt. Dieser besteht aus 16 Micro-Engines, einem eingebetteten RISC-Prozessor und aus mehreren Hardware-Beschleunigern [16].

Flexibilität ist ebenfalls ein wichtiges Kriterium. Dieses wird durch die Programmierbarkeit von Prozessoren erfüllt. Es ist von grosser Bedeutung, Netzwerkknoten möglichst rasch und kostengünstig an neue Dienste und Protokolle anpassen zu können.

Das System-on-a-Chip-Design bringt weitere Vorteile mit sich, wie die eines geringen Gewichts, eines kleinen Volumens und einer geringen Leistungsaufnahme. Auch die Zuverlässigkeit eines SoC ist sehr hoch. Da es keine schnell getakteten externen Busse gibt, sind weniger elektromagnetische Emissionen zu erwarten. Fortschritte in der Mikroelektronik ermöglichen es heute, mehrere Millionen Transistoren auf einem einzigen Chip zu integrieren. Um diese komplexen Systeme realisieren zu können, hat sich der Entwurf von ICs (Integrated Circuits) gewandelt. Das heutige Vorgehen besteht darin, bereits vorhandene Blöcke auf Systemebene mit selbst entworfenen Blöcken zu einem neuen Gesamtsystem zu kombinieren. Man spricht von einer blockbasierten (core-based) Entwurfsmethode, die hohe Produktivität durch Wiederverwendung bereits vorhandener Blöcke erreicht [17].

### 1.2 Projektüberblick

Diese Arbeit wurde zusammen mit dem IBM-Forschungslabor in Rüschlikon [18] ausgeführt. Für den Entwurf neuer Generationen von Netzwerkprozes-

soren hat IBM SystemC-Modelle [19] einzelner SoC-Blöcke wie Prozessoren, Speichercontroller und Busse erstellt. SystemC ist eine C++-Bibliothek, welche die nötigen Konstrukte zur Verfügung stellt, um Software- und Hardware-Systeme taktgenau zu modellieren. In zwei kürzlich erstellten Arbeiten [20, 21] werden diese Modelle kombiniert und ein Simulator für den Datenpfad eines einfachen Netzwerkprozessors geschaffen.

Die bestehende Simulationsumgebung wurde mit einem Multiprozessorblock zur Modellierung einer parallelen Paketverarbeitung sowie einer DMA-Einheit als zusätzliche Verkehrsquelle und -senke am Prozessor-Speicher-Bus ergänzt. Das ursprüngliche Vorhaben, die Arbitrierung im Netzwerkprozessor mit Hilfe dieses Simulators zu untersuchen, wurde jedoch aufgrund von bereits in der ursprünglichen Programmversion enthaltenen Fehlern verunmöglicht. Da diese nicht innert nützlicher Frist behoben werden konnten, kam für die Analyse der Arbitrierung ein selbstgeschriebener Matlab-Simulator zum Einsatz, der genau auf die entsprechende Problematik zugeschnitten ist.

### Kapitel 2

# Netzwerkprozessor-Simulator

In diesem Kapitel wird der uns zur Verfügung gestellte Simulator eines Netzwerkprozessors beschrieben. Zuerst wird ein Überlick der modellierten Architektur gegeben und danach werden die einzelnen Komponenten erklärt. In einem nächsten Abschnitt sind die am Modell getätigten Erweiterungen beschrieben.

#### 2.1 Referenz-Architektur

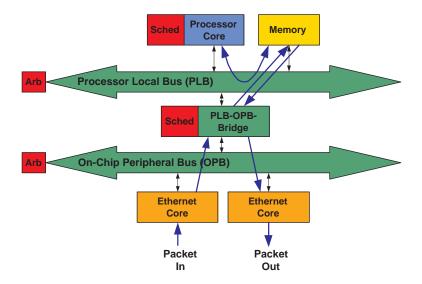

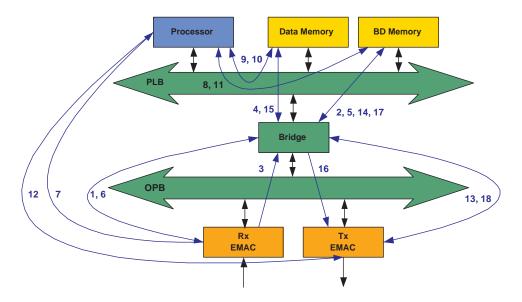

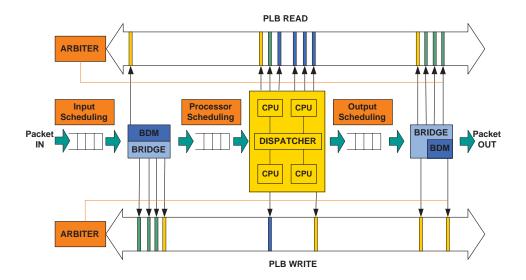

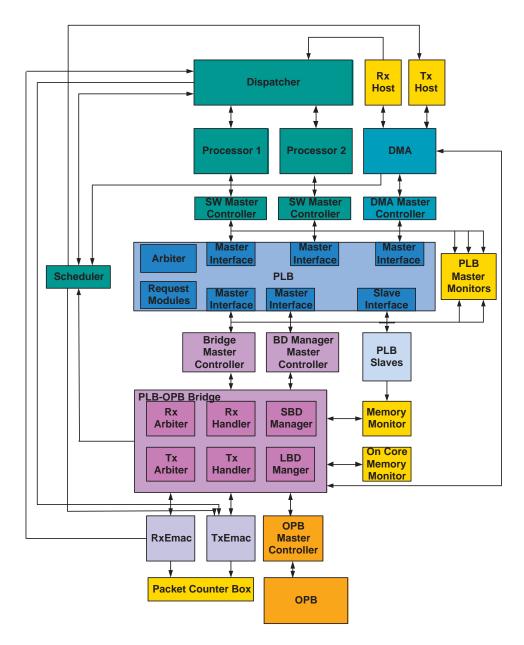

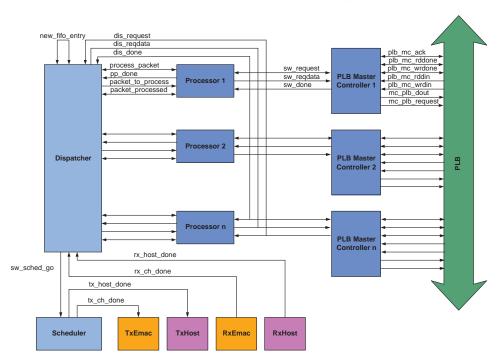

Figur 2.1 zeigt eine einfache Netzwerkprozessor-Architektur, die mit Blöcken aus existierenden Core-Bibliotheken [22, 23] aufgebaut ist. Sie besteht aus einem Prozessorblock, aus mehreren Speichern bzw. Speichercontrollern sowie Ethernet-Blöcken. Kernstück dieses Netzwerkprozessors ist ein Bus-System, das auf der CoreConnect-Architektur [22] basiert. Diese schliesst einen schnellen prozessornahen Bus (Processor Local Bus, PLB) und einen peripheren Bus (On-Chip Peripheral Bus, OPB) ein, welche mittels einer Brücke miteinander verbunden sind.

Der Datenpfad sieht folgendermassen aus: Ein eintreffendes Paket wird von einem Ethernet Core gelesen. Danach wird der Brücke signalisiert, dass ein Paket zur Übertragung bereitsteht. Die Brücke kümmert sich nun darum, das Paket in kleinen Dateneinheiten über den OPB zu lesen und via PLB in den Speicher zu schreiben. In einem nächsten Schritt wird dem Prozessor signalisiert, dass ein Paket zur Bearbeitung bereitsteht. Der Prozessor liest je nach Applikation das ganze Paket oder bloss seinen Header in seinen Cache ein und bearbeitet es. Danach wird es wieder in den Speicher zurückgeschrieben. Zum Abschluss der Verarbeitung ist wiederum die Brücke dafür zuständig, das Paket vom Speicher in einen Ethernet-Block zu schreiben.

Abbildung 2.1: Einfache Netzwerkprozessor-Architektur.

Arbitrierung ist an den Stellen möglich, die in Abbildung 2.1 mit roter Farbe gekennzeichnet sind. In jedem Bus ist ein Arbiter integriert, der jeweils die entsprechenden Busanfragen verwaltet. Ebenfalls mit roter Farbe markiert, sind die Scheduling-Einheiten. Die Brücke verfügt über zwei Scheduler, die das Input/Output-Scheduling durchführen. Der Scheduler auf Prozessor-Ebene entscheidet, welche Pakete verarbeitet werden.

#### 2.2 Modellabstraktion

Unter einem Modell versteht man die formale Beschreibung eines Systems. Dabei werden von einem zu modellierenden Objekt nur bestimmte Eigenschaften berücksichtigt und unerwünschte Details weggelassen – dies in einer Weise, dass die Aussagen über bestimmte Eigenschaften des Modells sich möglichst gut mit den entsprechenden Eigenschaften des realen Systems decken. Dabei möchte man erreichen, dass die Analyse des Modells wenn möglich einfacher ist als die entsprechenden Untersuchungen am realen System. Diesen Vorgang nennt man Abstraktion.

Der uns zur Verfügung stehende Simulator modelliert den Datenpfad des im vorherigen Abschnitt beschriebenen Netzwerkprozessors. Das Modell ist durch eine Vielzahl an Konfigurationsmöglichkeiten sehr flexibel und ermöglicht eine Entwurfsraumexploration, dadurch dass die Busarchitektur eine standardisierte Schnittstelle für unterschiedliche Einheiten, wie Prozessoren, Speichercontroller und Brücken bereitstellt. Diese Eigenschaft steht auch im

Einklang mit der Philosophie des System-on-a-Chip-Entwurfs, nämlich der Kombination bereits vorhandener Blöcke mit selbst eintworfenen Blöcken zu einem neuen Gesamtsystem.

Das Modell entspricht einer taktgenauen Repräsentation des realen Systems und erlaubt es, verschiedene Architekturentwürfe in Bezug auf ihre Leistung zu analysieren. Die Leistung des Systems wird in diesem Fall durch verschiedene Parameter, wie Durchsatz (Pakete pro Zeiteinheit), Verzögerung der einzelnen Pakete und Speicherbedarf charakterisiert. Über die Busse werden jedoch keine wirklichen Daten übertragen; ein Bus entspricht eher einem Verzögerungsglied, das je nach Umfang der zu übertragenden Daten eine Verzögerung generiert, die der realen Bus-Zugriffszeit und -Besetzungszeit entspricht. Pakete werden in der Simulation durch eine Datenstruktur repräsentiert und stehen nicht in Verbindung mit irgendwelchen Speicheradressen. Auf diese Datenstruktur wird mit Hilfe des C++-Zeigerkonzeptes zugegriffen. Für jeden Zugriff werden jedoch die entsprechenden Busanfragen generiert, die auch im realen System erforderlich wären. Dadurch wird der modellierte Paketfluss entsprechend verzögert.

#### 2.3 Komponenten-Modell

In diesem Abschnitt wird ein Überblick der verschiedenen SoC-Komponenten gegeben. Es wird auf Eigenschaften der realen Blöcke eingegangen sowie auf deren Modellierung. Für genauere Informationen verweisen wir auf die Arbeiten [20, 21].

#### 2.3.1 Busarchitektur

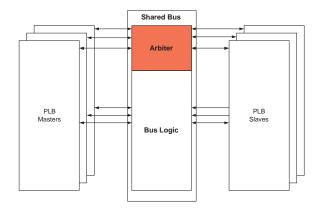

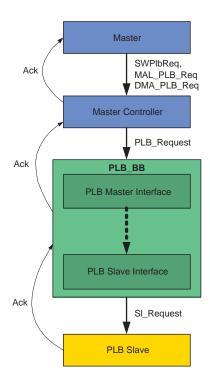

Die Busarchitektur besteht aus zwei Datenbussen, dem PLB und OPB. Zusätzlich ist ein Kontrollbus vorhanden, der in Figur 2.1 nicht eingezeichnet ist und auch nicht modelliert wird, weil er für die vorangehenden Arbeiten wie auch für diese nicht relevant ist. Der PLB ist ein Hochleistungsbus, der eine Schnittstelle für Einheiten bietet, die auf eine hohe Bandbreite und auf eine möglichst kleine Latenz angewiesen sind. Die Kommunikation auf dem PLB ist vollsynchron und es stehen getrennte Leitungen für Lese-, Schreib- und Adresszugriffe zur Verfügung. Anfragen können gepipelined werden. Masters und Slaves teilen sich den Bus, während ein zentraler Arbiter die Zugriffe auf diesen regelt (siehe Abbildung 2.2).

Der OPB ist ein zweiter Bus, der eine Schnittstelle für Eingabe/Ausgabe-Einheiten bietet. In diesem Fall handelt es sich um Ethernet-Blöcke. Der OPB hat im Gegensatz zum PLB keine getrennten Leitungen für Schreib-

Abbildung 2.2: Gemeinsamer Bus.

und Lesezugriffe.

Im Modell lassen sich beide Busse parametrisieren. Die Frequenz des PLB ist frei wählbar, muss aber einem Vielfachen der OPB Frequenz entsprechen. Die zugehörigen Parameter im Modell sind:

- *PLB\_FREQUENCY* (*plb\_params.h*): PLB-Busfrequenz.

- $OPB\_PLB\_CLK\_RATIO$  ( $opb\_params.h$ ): Verhältnis der PLB- zur OPB-Busfrequenz ( $\geq 1$ ).

- NUM\_MASTERS (plb\_params.h): Anzahl PLB Masters.

- NUM\_SLAVES (plb\_params.h): Anzahl PLB Slaves.

Des weiteren lässt sich die Breite der Daten- und Adressleitungen konfigurieren:

- PLB\_DATA\_WIDTH (plb\_params.h): Breite der Datenleitung in bit.

- PLB\_ADDR\_WIDTH (plb\_params.h): Breite der Adressleitung in bit.

- OPB\_DATA\_WIDTH (opb\_params.h): Breite der Datenleitung in bit.

- OPB\_ADDR\_WIDTH (opb\_params.h): Breite der Adressleitung in bit.

#### 2.3.2 Ethernet-Block (EMAC)

Der Ethernet-Block entspricht einer allgemeinen Implementierung des Medium-Access-Control-Protokolls. Zwei FIFOs puffern jeweils Paketdaten für

den Empfangs- und Sendepfad. Der EMAC hat zwei OPB-Schnittstellen, eine für den Zugang auf Konfigurations- und Statusregister, und eine andere bidirektionale Schnittstelle, um Daten zu senden und zu empfangen. Ein Ethernet-Block kann als Eingangs- und Ausgangsport betrachtet werden.

In der Simulation wird aus einer Datei eine reale Verkehrs-Trace gelesen, die auf eine Sequenz von Paketlängen reduziert ist, da weitere Header-Informationen nicht von Bedeutung sind. Die Verkehrs-Trace stammt aus der NLANR Datenbank [24]. Die wichtigsten Parameter zur EMAC-Konfiguration sind die folgenden:

- INPUT\_RATE\_PER\_EMAC (emac\_params.h): Entspricht der Linkgeschwindigkeit, mit der Pakete gelesen werden.

- *IFG (emac\_params.h):* (Interframe Gap) Entspricht der Zwischenankunftszeit der Pakete.

- RX\_CHANNEL\_NBR (Bridge\_params.h): Entspricht der Anzahl Rx-EMACs (Receive EMACs). Ein RxEMAC entspricht repräsentiert den Empfangskanal (Rx-Kanal) eines EMACs.

- TX\_CHANNEL\_NBR (Bridge\_params.h): Entspricht der Anzahl Tx-EMACs (Transmit EMACs). Ein TxEMAC repräsentiert den Sendekanal (Tx-Kanal) eines EMACs.

- *PKT\_NUMBER\_PER\_EMAC* (*emac\_params.h*): Entspricht der Anzahl Pakete, die vom EMAC während einer Simulation gelesen werden.

#### 2.3.3 PLB-OPB-Brücke

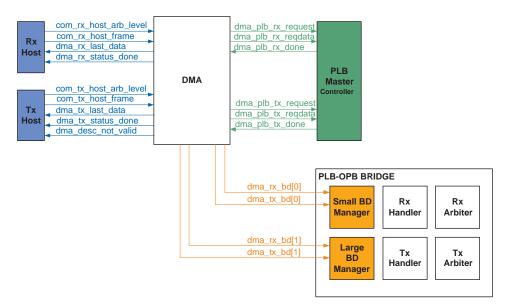

Die Brücke dient als Verknüpfungsglied zwischen den zwei Bussen und ermöglicht eine direkte Kommunikation zwischen peripheren Einheiten und PLB Masters, indem Brücken- und DMA-Funktionalität geboten werden. Ein EMAC kommuniziert mit dem PLB über die PLB-OPB-Brücke. Aus Sicht des OPBs ist ein EMAC ein Slave und hat somit keine Möglichkeit, einen Transfer zu initiieren. Aus diesem Grund gibt es eine weitere Schnittstelle zwischen EMAC und Brücke, über die sogenannte Sideband-Signale übertragen werden, welche die Brücke für eine Paketübertragung triggern. Die PLB-OPB-Brücke überträgt ein Paket vom EMAC in den Speicher in Form von parametrisierbaren Dateneinheiten, sogenannten Bursts. Die entsprechenden Parameter im Modell sind:

• BRIDGE\_RX\_BURST\_SIZE (Bridge\_params.h). Burst im Empfangspfad.

• BRIDGE\_TX\_BURST\_SIZE (Bridge\_params.h). Burst im Sendepfad.

Eine weitere Eigenschaft der Brücke ist, dass diese über zwei Scheduler verfügt. Diese realisieren das Input/Output-Scheduling. Es ist zu beachten, dass für jede zu übertragende Dateneinheit eines Pakets auf OPB-, PLB-und ebenfalls auf Brücken-Ebene arbitriert wird.

Die Brücke kann gleichzeitig einen Empfangs- und einen Sendekanal bedienen (Rx- und Tx-Kanal). Im Empfangskanal wird ein Paket vom Eingangsport in den Speicher geschrieben. Es sind dafür OPB-Lese- und PLB-Schreibzugriffe nötig. Im Sendekanal wird das Paket vom Speicher in einen Ausgangsport geschrieben. Es werden PLB-Lese- und OPB-Schreibzugriffe getätigt. Folgende Kombinationen von gleichzeitigen Busbesetzungen sind aus Sicht der Brücke möglich:

| Rx-Kanal      |                       | Tx-Kanal      |

|---------------|-----------------------|---------------|

| PLB schreiben | $\longleftrightarrow$ | PLB lesen     |

| PLB schreiben | $\longleftrightarrow$ | OPB schreiben |

| OPB lesen     | $\longleftrightarrow$ | PLB lesen     |

Tabelle 2.1: Gleichzeitig mögliche Busbesetzungen.

#### 2.3.3.1 Pufferdeskriptoren-Verwaltung

Die Brücke ist dafür zuständig, für jedes Paket die nötigen Pufferdeskriptoren zu verwalten. Ein Pufferdeskriptor ist eine Datenstruktur, die unter anderem eine Speicheradresse und ein Statusfeld beinhaltet. Deskriptoren selber befinden sich in einem dedizierten On-Chip-Speicher und müssen über den PLB gelesen werden, bevor der entsprechende Pufferspeicher benutzt werden kann. Die Deskriptoren stellen eine gemeinsame Ressource dar, die von mehreren PLB Masters (Brücke, Prozessor) benutzt wird. Folglich müssen Zugriffs- und Synchronisationsregeln eingehalten werden, um mögliche Konflikte zu vermeiden. Der Prozessor sollte zum Beispiel nicht einen Puffer überschreiben, der noch nicht von der Brücke geschrieben worden ist. Zur Vermeidung solcher Fälle dient das Statusfeld, das nach jedem Lesen eines Deskriptors und der Benutzung des entsprechenden Speicherbereichs aktualisiert werden muss. Bei Beendigung einer Paketübertragung muss die Brücke zusätzlich den benutzten Pufferspeicher wieder freigeben.

Im Modell werden zwei parametrisierbare Puffergrössen unterschieden. Mit Hilfe der Parameter

- BRIDGE\_SBD\_DATA\_SIZE (Bridge\_params.h): Speichergrösse der kleinen Puffer.

- BRIDGE\_LBD\_DATA\_SIZE (Bridge\_params.h): Speichergrösse der grossen Puffer.

sind diese konfigurierbar. Im Modell werden Puffergrössen von 64 und 1472 Bytes unterschieden. Je nach Paketgrösse sind demzufolge ungleich viele Pufferdeskriptoren nötig. Der Header eines Pakets, dessen Grösse im Modell stets 64 Byte beträgt<sup>1</sup>, wird in einen kleinen Puffer geschrieben. Für die Payload des Pakets, werden je nach Grösse einer oder mehrere grosse Puffer benutzt.

Es ist zu erwähnen, dass die Brücke auf zwei verschiedene Arten betrieben werden kann. Der Unterschied liegt in der Art, wie die Pufferdeskriptoren verwaltet werden. In einem Fall wird ein Pufferdeskriptor nur bei Bedarf aus dem Speicher gelesen. Im anderen Fall hat die Brücke einen zusätzlichen Cache-Speicher, in welchem mehrere Pufferdeskriptoren für eine spätere Verwendung zwischengespeichert werden können. In dieser Arbeit wurde jeweils der erste Fall betrachtet.

#### 2.3.4 Speicher

Auf Speichereinheiten wird über den PLB zugegriffen. Sie können entweder On-Chip oder Off-Chip sein. Im Modell sind zwei Speicher vorhanden, ein schneller Speicher (z.B. ein SRAM) für die Pufferdeskriptoren und ein langsamerer für die Paketdaten (z.B. ein DRAM).

Das Speichermodell erlaubt es, Latenzen für erste und sequentielle Schreibund Lesezugriffe zu parametrisieren. Diese Parameter werden bei der Initialisierung der PLB-Slave-Module eingestellt. Dadurch lassen sich auf einer hohen Abstraktionsebene unterschiedliche Speichereinheiten modellieren. Wie bereits im vorherigen Abschnitt beschrieben, werden zwei Puffergrössen unterschieden. Die Anzahl Puffer wird durch die Parameter

- BRIDGE\_SBD\_NBR (Bridge\_params.h): Entspricht der Anzahl kleiner Puffer.

- BRIDGE\_LBD\_NBR (Bridge\_params.h): Entspricht der Anzahl grosser Puffer.

#### eingestellt.

<sup>&</sup>lt;sup>1</sup>Die übliche Grösse eines IPv4-Headers beträgt 20 Bytes; maximal sind 60 Bytes möglich, dies falls der optionale Header-Bereich voll ausgeschöpft wird.

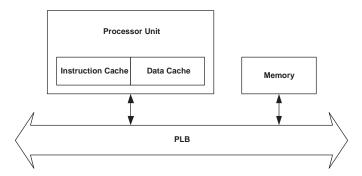

#### 2.3.5 Prozessor-Block

Für die Recheneinheiten stehen zwei unterschiedliche Modelle zur Verfügung. In einem einfachen Modell wird der Prozessor als ein reines Verzögerungsglied modelliert, welches je nach Paketlänge unterschiedlich lange wartet, entsprechend der eigentlichen Bearbeitungszeit. Die einzige PLB-Last, welche vom Prozessor generiert wird, rührt vom Lesen eines Pufferdeskriptors und des Headers sowie dem Schreiben des Pufferdeskriptor-Statusfeldes her.

In einem zweiten Modell, das in [25] detailliert beschrieben ist, werden Speicherzugriffe und somit auch die generierte PLB-Last je nach Prozessor-Anwendung modelliert. Für diesen Zweck werden verschiedene Netzwerkprozessor-Anwendungen bezüglich ihrer Art und Anzahl Instruktionen betrachtet. Die modellierten Anwendungen orientieren sich an den CommBench-Applikationen [26]. CommBench unterscheidet zwei Klassen von Anwendungen, nämlich solche mit Header Processing und solche mit Payload Processing. Je nach Anwendung werden verschiedene Typen von Instruktionen

Abbildung 2.3: Prozessor-Modell.

#### unterschieden:

- Ladeinstruktionen: Instruktionen, die Daten vom Cache oder Hauptspeicher lesen.

- Schreibinstruktionen: Instruktionen, die Daten in den Cache oder Hauptspeicher schreiben.

- Interne Instruktionen: Alle restlichen Instruktionen, die keine externen Zugriffe benötigen.

Die Anzahl Instruktionen hängt von der Anwendung selber und im Falle von Payload Processing zusätzlich von der Paketgrösse ab. Weiter ist für jede Anwendung eine Verteilung der Instruktionen auf drei Phasen gegeben. Je nachdem ob sich das Programm in der Start-, Mittel- oder Endphase befindet, ist die Wahrscheinlichkeit, dass ein bestimmter Typ von Instruktion auftritt, unterschiedlich. Zum Beispiel werden anfangs allgemein mehr Ladeinstruktionen und gegen Ende mehr Schreibinstruktionen auftreten. Die Speicherzugriffe sind von der Anzahl Lade- und Schreibinstruktionen, sowie von der Cachegrösse abhängig. Da der interne Prozessorcache eine partielle Kopie des Hauptspeicher beinhaltet, muss der Prozessor nicht auf externen Speicher zugreifen, sofern sich die Daten im Cache befinden. Da die totale Datenmenge im Cache und nicht sein eigentlicher Inhalt von Bedeutung ist, wird im Modell ein Zähler verwendet, welcher die momentan freie Cachekapazität repräsentiert. Das Prozessormodell ist sehr flexibel aufgrund der Vielzahl an Konfigurationsmöglichkeiten. Die wichtigsten Parameter sind hier aufgeführt:

- NO\_OF\_INSTRUCTIONS\_APP (processor\_params.h): Anzahl Instruktionen je nach Anwendung.

- LD\_FREQUENCY\_APP (processor\_params.h): Anzahl Ladeinstruktionen je nach Anwendung.

- ST\_FREQUENCY\_APP (processor\_params.h): Anzahl Schreibinstruktionen je nach Anwendung.

- PROCESSOR\_SPEED (processor\_params.h): Prozessor-Geschwindig-keit (Taktfrequenz).

- CYCLES\_PER\_INSTRUCTION (processor\_params.h): Anzahl Zyklen pro Instruktion.

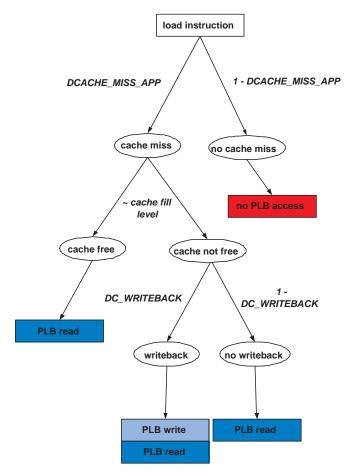

Abbildungen 2.4 und 2.5 zeigen die resultierenden PLB-Zugriffe in Abhängigkeit der einstellbaren Cache-Parameter. Die Parameter

- ICACHE\_MISS\_APP (processor\_params.h): Missrate für den Instruktionscache. Pro Anwendung einstellbar.

- DCACHE\_MISS\_APP (processor\_params.h): Missrate für den Datencache. Pro Anwendung einstellbar.

entsprechen der Wahrscheinlichkeit, dass beim Ausführen einer Ladeinstruktion sich die entsprechenden Daten nicht im Cache vorfinden (Cache Miss). APP ist dabei ein Platzhalter für die verschiedenen Anwendungen, die im Prozessormodell simuliert werden. Abhängig von den Parametern:

- ICACHE\_SIZE (cache\_params.h): Instruktionscache-Grösse

- DCACHE\_SIZE (cache\_params.h): Datencache-Grösse

#### • DC\_WRITEBACK (processor\_params.h)

sind bei einem Cache Miss entweder ein oder zwei PLB-Zugriffe nötig. Falls noch Cachespeicher zur Verfügung steht, können die Daten vom Speicher in den Cache geschrieben werden. Falls kein Cachespeicher mehr frei ist, wird anhand des Parameters  $DC\_WRITEBACK$  entschieden, ob vorhandene Daten überschrieben werden können. Falls nicht, muss ein Teil des Caches in den Speicher zurückgeschrieben werden und es sind zwei PLB-Zugriffe erforderlich – ein Lese- und ein Schreibzugriff.

Beim Ausführen einer Schreibinstruktion wird anhand des Parameters

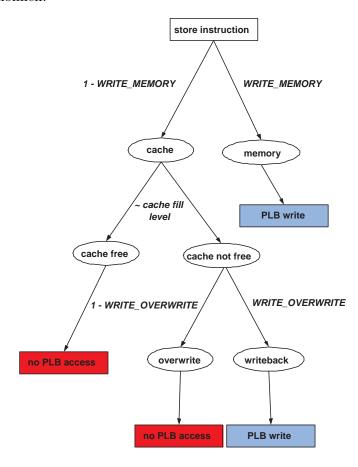

Abbildung 2.4: Ladeinstruktion.

#### • WRITE\_MEMORY (processor\_params.h)

die Wahrscheinlichkeit definiert, dass die Daten in den Hauptspeicher geschrieben und nicht bloss im Cache zur späteren Verwendung zwischen-

gespeichert werden. Falls die Daten im Cache abgelegt werden, spielt der Parameter

#### • WRITE\_OVERWRITE (processor\_params.h)

eine Rolle. Sollte nicht genügend Cachespeicher vorhanden sein, so wird gemäss diesem Parameters entschieden, ob vorhandene Daten überschrieben werden können.

Abbildung 2.5: Schreibinstruktion.

Die Parameter sind derzeit so gewählt, dass ein General Purpose Prozessor simuliert wird.

#### 2.3.6 Zusammenfassung

Anhand der Abbildung 2.6 wird der Datenpfad der modellierten Netzwerkprozessor-Architektur erklärt. Die Beschriftung der Pfeile entspricht der zeit-

Abbildung 2.6: Datenpfad.

lichen Reihenfolge der Schritte, die bei der Abarbeitung eines Pakets durchlaufen werden.

- 1. Nach der Ankunft eines Pakets im EMAC wird die Brücke über Sideband-Signale für eine Paketübertragung getriggert.

- 2. Die Brücke liest einen Pufferdeskriptor. Die Paketübertragung kann beginnen.

- 3. Daten werden vom EMAC über den OPB gelesen.

- 4. Daten werden über den PLB in den Speicher geschrieben.

- 5. Die Schritte 3 und 4 werden solange wiederholt, bis das ganze Paket in den Speicher geschrieben worden ist. Falls nötig, müssen weitere Pufferdeskriptoren gelesen werden. Wenn das ganze Paket übertragen ist, wird das Statusfeld der verwendeten Pufferdeskriptoren aktualisiert.

- 6. Der EMAC wird über Sideband-Signale darauf hingewiesen, dass die Paketübertragung beendet ist.

- 7. Daraufhin triggert dieser über Sideband-Signale den Prozessor, um diesen zu informieren, dass ein Paket zur Bearbeitung bereitsteht.

- 8. Der Prozessor liest die nötigen Pufferdeskriptoren.

- 9. Prozessor liest über den PLB das Paket bzw. nur dessen Header, falls ausschliesslich Header-Processing-Anwendungen ausgeführt werden.

- Schritt 9 wird solange ausgeführt bis das ganze Paket gelesen worden ist. Danach wird es bearbeitet und wieder in den Speicher zurückgeschrieben.

- 11. Statusfelder der Pufferdeskriptoren werden aktualisiert.

- 12. Über Sideband-Signale wird ein TxEMAC getriggert.

- 13. Daraufhin triggert dieser über Sideband-Signale die Brücke, um diese zu informieren, dass ein Paket zur Übertragung bereit steht.

- 14. Die Brücke liest einen Pufferdeskriptor. Die Paketübertragung kann beginnen.

- 15. Daten werden über den PLB gelesen.

- 16. Daten werden über den OPB in den TxEMAC geschrieben.

- 17. Die Schritte 15 und 16 werden so lange wiederholt, bis das ganze Paket in den TxEMAC geschrieben worden ist. Bei Beendigung der Übertragung werden die Pufferdeskriptoren freigegeben.

- 18. TxEMAC wird über Sideband-Signale darauf hingewiesen, dass die Paketübertragung beendet ist.

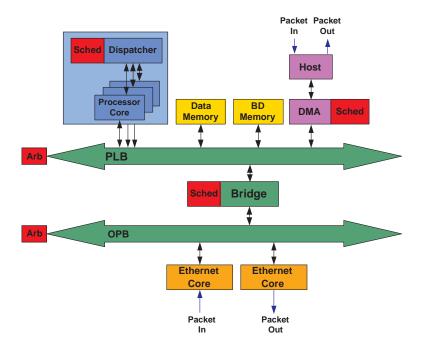

#### 2.4 Erweiterte Architektur

Die bestehende Architektur wurde so ergänzt, dass die getätigten Erweiterungen im Einklang mit modernen Netzwerkprozessor-Architekturen stehen. Wie bereits in Abschnitt 1.1.3 erwähnt, werden in heutigen Netzwerkprozessoren mehrere Recheneinheiten eingesetzt, um den Durchsatz zu erhöhen. Die Referenzarchitekur wurde deshalb um eine Multiprozessoreinheit ergänzt, die in Abbildung 2.7 mit blauer Farbe eingezeichnet ist. Des weiteren wurde das Modell um eine DMA-Einheit erweitert, die in Abbildung 2.7 mit blauer Farbe gezeichnet ist. Dadurch besteht die Möglichkeit einen Netzwerkprozessor in Kombination mit einem DMA-Controller als Netzwerk-Terminal einzusetzen.

Durch diese Erweiterungen ist gleichzeitig eine sinnvolle Umgebung geschaffen worden, um die Arbitrierung auf PLB-Ebene zu analysieren. Damit die Arbitrierung einen merklichen Einfluss auf die Leistung haben kann, muss der PLB eine knappe Ressource darstellen. Dies bedeutet, dass zu gewissen Zeiten der PLB nicht alle Anfragen bearbeiten kann und es zu Konflikten zwischen den anfragenden Masters kommt. Sobald das System einen Zustand der Überlast erreicht, wird die Arbitrierung interessant. Durch die Verwendung effizienter Algorithmen, welche nach gewissen Kriterien die Abarbeitungsreihenfolge der Anfragen bestimmen, sind Gewinne hinsichtlich Durchsatz und mittlerer Verzögerung zu erwarten.

Arbitrierungsfragen auf OPB-Ebene werden hier nicht beachtet, da an diesem Bus nur ein einziger Master angeschlossen ist, nämlich die PLB-OPB-

Brücke.

Abbildung 2.7: Erweiterte Netzwerkprozessor-Architektur.

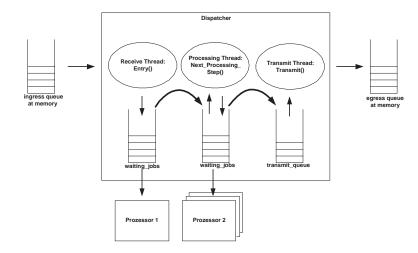

#### 2.4.1 Multiprozessoreinheit

Die Architektur wurde um zusätzliche Prozessoren erweitert, die unter der Kontrolle eines Dispatchers stehen. Dadurch kann die Linkgeschwindigkeit erhöht werden, da genügend Rechenleistung zur Verfügung steht, um die Paketverarbeitung mit der nötigen Geschwindigkeit zu verrichten. Die Anzahl Prozessoren wird durch den Parameter

• NUM\_COPROCESSORS (MultiProcessor\_params.h)

festgelegt. Das Multiprozessormodell kann auf zwei verschiedene Arten betrieben werden: im Run-to-Completion- oder im Pipelining-Modus. Der entsprechende Parameter im Modell ist:

• RUN2COMP (MultiProcessor\_params.h).

Im Run-to-Completion-Modus kann man die Rechneinheiten als gleichwertige General Purpose Prozessoren betrachten, die alle die gleichen Anwendungen ausführen können. Ein Paket wird in diesem Modus jeweils nur von

einem Prozessor bearbeitet. Der Dispatcher ist so etwas wie ein Load Balancer, der die anfallende Last unter den vorhanden Prozessoren aufteilt.

Im Pipelining-Modus kann man die Recheneinheiten als dedizierte Hardware-Einheiten betrachten, die jeweils nur eine bestimmte Paketverarbeitungsfunktion ausführen. Ein Paket wird in diesem Modus von mehreren Recheneinheiten nacheinander bearbeitet. In beiden Modi basieren die einzelnen Recheneinheiten auf dem bereits existierenden Prozessormodell, das in Abschnitt 2.3 beschrieben wurde. Im Pipelining-Modus müssen die einzelnen Verarbeitungsfunktionen auf die entsprechenden Prozessoren abgebildet werden. Dies wird mit Hilfe von

• WHO\_DOES\_IT (MultiProcessor\_params.h).

festgelegt.

Im Run-to-Completion-Modus wird von einem Prozessor folgende PLB-Last generiert: Es werden, je nach Paketgrösse, die nötigen Pufferdeskriptoren gelesen und nach der Bearbeitung deren Statusfeld aktualisiert. Je nach Anwendung wird nur der Header oder das ganze Paket gelesen. Bei Payload-Anwendungen werden nach der Bearbeitung die Daten in den Speicher zurückgeschrieben. Bei Header-Anwendungen wird ein Zurückschreiben des möglicherweise modifizierten Headers vernachlässigt. Zusätzliche PLB-Last ist abhängig von der Cachegrösse und der Cachemissrate.

Im Pipelining-Modus fällt die gleiche PLB-Last pro Pipeline-Stufe an. Das bedeutet, dass ein Paket beim Durchlaufen von vier Recheneinheiten, die jeweils unterschiedliche Anwendungen ausführen, viermal so viel Last erzeugt, wie wenn nur ein Prozessor alle Anwendungen ausführen würde. Die vom Programmfluss abhängigen PLB-Zugriffe (Cachemisses, Memory Writebacks) werden auf die ganze Pipeline verteilt, nehmen aber in ihrer Zahl nicht zu.

Ein weiteres Merkmal der Multiprozessoreinheit ist, dass der Dispatcher als funktionale Einheit eines bestimmten Prozessors unter den vorhandenen betrachtet werden kann. Mit Hilfe des Parameters

• CPU\_COPROCESSOR (MultiProcessor\_params.h).

wird ein Prozessor bestimmt, der mit dem Dispatcher eine Einheit bildet. Durch diese Einstellung wird dem Dispatcher ermöglicht, über die PLB-Schnittstelle des Prozessors den Bus zu benutzen. Im Modell wird von dieser Eigenschaft nicht Gebrauch gemacht. Der Dispatcher wird jeweils als externe Einheit aufgefasst, die eine reine Kontrollfunktion besitzt und nicht auf

den PLB zugreifen muss. Diese Fähigkeit wurde im Hinblick auf mögliche Erweiterungen des Multiprozessormodells implementiert.

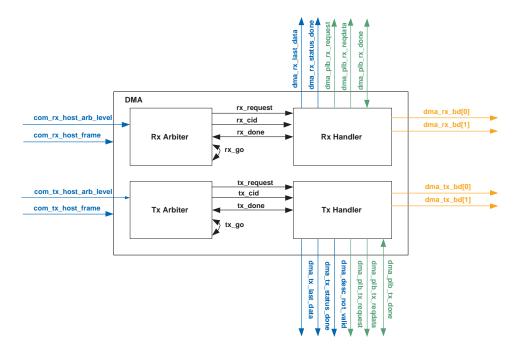

#### 2.4.2 Direct Memory Access Controller

Durch eine DMA-Einheit lassen sich direkt am PLB neue Verkehrsquellen und -senken hinzufügen, um unabhängig vom OPB die PLB-Last zu variieren. Durch diese Erweiterung ändert sich der Datenpfad. Pakete können nun über die DMA-Einheit in das System eingespiesen werden oder das System verlassen.

Das DMA-Modell ist eine vereinfachte Version der PLB-OPB-Brücke. Im Vergleich zur Brücke ist die OPB-Schnittstelle nicht vorhanden. Die DMA-Einheit verfügt des weiteren über eine Schnittstelle zur PLB-OPB-Brücke. Sobald ein Paket beim DMA-Block zur Übertragung bereitsteht, müssen zuerst die erforderlichen Pufferdeskriptoren bezogen werden. Da die PLB-OPB-Brücke diese zentral verwaltet, ist es Aufgabe der Brücke, die Deskriptoren der DMA-Einheit bekanntzugeben. Im realen System sendet die Brücke dem DMA-Block über den Kontrollbus (siehe Abschnitt 2.3) eine Datenstruktur, die auf den nächsten zur Verfügung stehenden Pufferdeskriptor zeigt. Im Modell lässt sich für diesen Vorgang die Latenz konfigurieren, d.h. die Anzahl Taktzyklen, die vom Zeitpunkt der DMA-Anfrage eines Pufferdeskriptors bis zu dessen Verfügbarkeit in der DMA-Einheit vergehen. Der zugehörige Parameter heisst

• LATENCY\_NEXT\_BD (DMA\_params.h).

Am DMA-Block ist ein Host-Modul angeschlossen, das eine Verkehrsquelle und -senke darstellt. Der Host entspricht im Modell einem EMAC-Modul und kann ebenfalls als Eingangs- und Ausgangsport betrachtet werden. Die Kommunikation zwischen Host und DMA-Einheit entspricht der Art und Weise wie ein EMAC mit der Brücke kommuniziert. In diesem Fall ist aber kein OPB vorhanden, und die Pakete stehen der DMA-Einheit zur Verfügung, sobald diese vom Host gelesen wurden.

Durch folgende Parameter ist die DMA-Einheit konfigurierbar:

- HOST\_RATE (DMA\_params.h): Enstpricht der Geschwindigkeit, mit der Pakete vom Host gelesen werden.

- IFG\_HOST (DMA\_params.h): Zwischenankunftszeit der Pakete.

- RX\_HOST\_NBR (DMA\_params.h): Anzahl Verkehrsquellen.

- TX\_HOST\_NBR (DMA\_params.h): Anzahl Verkehrssenken.

- DMA\_RX\_BURST\_SIZE (DMA\_params.h): Grösse der Dateneinheit, die im Empfangspfad von der DMA übertragen wird.

- DMA\_TX\_BURST\_SIZE (DMA\_params.h): Grösse der Dateneinheit, die im Sendepfad von der DMA-Einheit übertragen wird.

#### 2.5 Matlab-Simulation

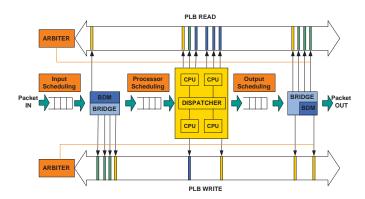

Zur Untersuchung des Datenaustauschs auf dem Processor Local Bus wurde neben der SystemC-Simulation auch eine Matlab-Simulation erstellt. Dieses parallele Vorgehen erlaubte einerseits die Umgehung der Probleme mit der übernommenen SystemC-Simulation, andererseits aber auch eine Fokussierung auf die Umgebung des PLB und damit eine ausschliessliche Simulation der für die Untersuchung der PLB-Arbitrierung relevanten Prozessoreigenschaften. Weiter bietet Matlab den wertvollen Vorteil einer grösstmöglichen Zugänglichkeit zu den Simulationsdaten und dazu eine Vielzahl an spezialisierten Befehlen zur Auswertung und Darstellung der Ergebnisse.

Abbildung 2.8: PLB-Umgebung mit typischem Requestmuster.

Das für die Matlab-Simulation verwendete Modell lässt sich am besten anhand von Abbildung 2.8 erläutern. Dargestellt ist die Umgebung des PLB (dieser ist aufgeteilt in Read- und Write-Bus) mit den involvierten PLB-Masters. Die Pakete durchlaufen den mit grünen Pfeilen markierten Weg von der Bridge (Receive Path) über den Prozessorblock und zurück zur Bridge (Transmit Path). Dieser Prozess verursacht für jedes Paket ein charakteristisches Muster von Requests auf den beiden Komponenten des PLB. Es wurde darauf geachtet, dass dieses Muster so weit als möglich dem im

SystemC-Simulator implementierten Verhalten entspricht<sup>2</sup>, indem die Parameter, welche für die Zahl, den Moment des Auftritts und die Länge der Requests verantwortlich sind, miteinbezogen wurden.

Von zentraler Bedeutung sind die drei Scheduler (Input, Processor und Output Scheduling) sowie die Bus-Arbitrierung. Ziel der Simulation ist die Untersuchung des Zusammenspiels der Arbitrierung mit dem Scheduling der Verarbeitungseinheiten des Netzwerkprozessors. Zu diesem Zweck wurde eine Reihe an Arbitern implementiert, die mit verschiedenen Schedulern kombiniert werden können. Die betrachteten Szenarien mit den entsprechenden Resultaten sind Thema im Kapitel 3.

Wie erwähnt sind die nahezu unbegrenzten Möglichkeiten in Sachen Auswertung ein Pluspunkt der Matlab-Simulation. So erlauben die im Anschluss an die Simulation erzeugten Graphiken einen schnellen Ueberblick der Resultate und bieten gleichzeitig Hand für eine genauere Analyse und weiterführende Erkenntnisse.

<sup>&</sup>lt;sup>2</sup>Es ist hier anzumerken, dass dies nicht in allen Fällen verifiziert wurde, da der SystemC-Simulator nur beschränkt eingesetzt werden konnte. Es kann also nicht mit hundertprozentiger Sicherheit auf eine Übereinstimmung der Resultate gebaut werden.

### Kapitel 3

# **Bus-Arbitrierung**

#### 3.1 Definition des Arbiters

Wie in Kapitel 1.1.3 beschrieben, werden in modernen Netzwerkprozessoren mehrere Recheneinheiten gleichzeitig eingesetzt, um die parallele Verarbeitung von Paketen zu ermöglichen. Der erhöhte Aufwand wird mit einem bedeutend gesteigerten Durchsatz belohnt, womit auch hohe Linkkapazitäten von der Elektronik gemeistert werden können. Mit der Anzahl der involvierten Prozessorblöcke nimmt auch die Komplexität ihrer gegenseitigen Kommunikation zu. Eine vergleichsweise einfache Lösung, welche die relevanten Komponenten verbindet und gleichzeitig einen hohen Grad an Flexibilität (Ausbaufähigkeit und Konfigurierbarkeit) bietet, ist der Einsatz eines Busses. Im vorliegenden Beispiel dient der so genannte Processor Local Bus (PLB) dazu, den Austausch von Daten unter den verschiedenen Komponenten (Rechen- und Speichereinheiten, die PLB-OPB-Brücke) zu ermöglichen.

Da es sich bei einem Bus um eine geteilte Ressource (shared medium) handelt, sind Konflikte beim Zugriff, insbesondere im Falle einer hohen Auslastung, nicht zu vermeiden. Die Aufgabe, eine gleichzeitige Benutzung durch mehrere Masters zu verhindern, obliegt einer dem Bus angegliederten Instanz – dem Arbiter<sup>1</sup>. Dieser arbitriert die Anfragen der Masters, welche zu einem gegebenen Zeitpunkt Daten über den Bus schicken möchten. Der Arbiter entspricht damit einer Funktion, die aus einer vorliegenden Menge von Busanfragen (Requests) diejenige auswählt, welche als nächste abgearbeitet werden soll. Dies erfolgt in der Regel dadurch, dass dem entsprechenden Master die Vollmacht zur alleinigen Benutzung des Busses während einer bestimmten Zeit oder bis zum Zeitpunkt, da dieser ihn nicht mehr benötigt,

<sup>&</sup>lt;sup>1</sup>lat. arbiter = Schiedsrichter

erteilt wird. Als Kriterien für den Entscheid des Arbiters kommen z. B. in Frage:

- die Identität des Masters

- die Identität des Slaves

- die Art des Requests (Priorität, Grösse u.a.)

- der Zustand des Systems (Belastungsgrad, Betriebsmodus)

- die vorhergehenden Arbiterentscheide

Basierend auf den genannten Kriterien sind unzählige Arbitrierungsschemen denkbar. In der Praxis basiert der Entscheid des Arbiters jedoch meist nicht auf mehreren Faktoren, womit der damit verbundene Algorithmus verhältnismässig einfach gehalten werden kann.

#### 3.2 Konzepte zur Arbitrierung

In der Vergangenheit wurden zahlreiche Methoden entwickelt, die das Problem der Arbitrierung in unterschiedlicher Weise angehen. Von den existierenden Algorithmen sollen hier einige kurz vorgestellt werden. Zu ihrer Beurteilung sind die folgenden Kriterien von Bedeutung:

- Fairness.<sup>2</sup> Ein Arbiter ist dann fair, wenn er allen Masters denselben Anteil an Busbandbreite zugesteht, sofern diese ständig neue Requests anbringen. Fairness kann auch in dem Sinne uminterpretiert werden, als dass jedem Master ein gewisser Mindestanteil garantiert wird, der jedoch von Master zu Master variiert. In diesem Fall spricht man von Weighted Fairness.

- Begrenzte Latenz. Eine begrenzte Latenz ist dann gewährleistet, wenn eine obere Zeitlimite für die Abarbeitung eines Requests existiert.

- Busauslastung. Ein Arbiter sollte dafür sorgen, dass die Auslastung des Busses maximal ist, solange von Seiten der Masters Anfragen zur Abarbeitung bereitstehen.

- Komplexität der Implementierung. In der Praxis spielt es eine wichtige Rolle, ob ein Arbitrierungsalgorithmus leicht in schneller Hardware implementiert werden kann. Die entsprechende Komponente

<sup>&</sup>lt;sup>2</sup>Für den Begriff der *Fairness* existieren in der Literatur verschiedene zum Teil relativ umständliche Definitionen. Hier werden wir uns auf eine einfache Formulierung beschränken, welche für die folgende Betrachtung unterschiedlicher Arbiter ausreicht.

sollte ihre Aufgabe möglichst ohne grossen Speicher- und Rechenaufwand in kürzester Zeit erledigen können.

Zur Implementierung ist noch anzumerken, dass gewisse Schemen nicht unbedingt durch eine separate Hardware-Einheit umgesetzt werden müssen, sondern auch verteilt in den Busmasters realisiert werden können, man spricht dann von dezentraler Arbitrierung.

#### 3.2.1 Beispiele von Arbitern

#### 3.2.1.1 Static Priority

Der wohl einfachste Weg, einen Arbitrierungsentscheid zu fällen, besteht darin, sich ausschliesslich auf eine statisch festgelegte Masterpriorität zu konzentrieren. Der Bus wird dem Master überlassen, der in der Rangfolge den obersten Platz belegt unter denjenigen, die den Bus beanspruchen möchten. Ein einziger Master erhält somit die Möglichkeit, den Bus auf alle Ewigkeit zu blockieren, sofern er nicht von sich aus auf weitere Datenübertragung verzichtet. Damit sind Fairness und begrenzte Latenz nicht gegeben. Hingegen kann dieser Arbiter mit einer guten Busauslastung und einer problemlosen Implementierung aufwarten.

#### 3.2.1.2 Round Robin und Weighted Round Robin

Ein Round-Robin-Algorithmus benötigt eine zyklische Liste der involvierten Masters sowie einen Zeiger, der auf einen Listeneintrag zeigt. Bei der Arbitrierung erhält nun derjenige Master Priorität, auf welchen der Round-Robin-Pointer zum aktuellen Zeitpunkt gerade zeigt. Liegt vom entsprechenden Master kein Request vor, so springt der Zeiger zum nächsten Listeneintrag (bzw. Master) bis schliesslich ein Master an der Reihe ist, der auch einen Request bereitliegen hat. Nach der Abarbeitung dieser Anfrage springt der Zeiger für die nächste Arbitrierung auf den darauffolgenden Listeneintrag. Beim einfachen Round-Robin-Algorithmus enthält die zyklische Liste für jeden Master einen Eintrag, während die Gewichtung beim Weighted-Round-Robin-Algorithmus durch mehrfache Einträge gewisser Masters erreicht werden kann. Der (Weighted-)Round-Robin-Arbiter ist gleichzeitig fair und garantiert eine begrenzte Latenz. Seine Implementierung ist nicht besonders schwierig, benötigt er doch nur wenig Speicherplatz (für die zyklische Liste und den Zeiger) und keine komplexen Rechenoperationen.

#### 3.2.1.3 First-come-first-served-Arbiter (FCFS)

Der FCFS-Arbiter arbeitet mit einer First-in-first-out-Warteschlange. Requests werden also in der Reihenfolge ihres Eintreffens abgearbeitet. Wird eine einzige Warteschlange verwendet, so ist die durchschnittliche Wartezeit pro Request für alle Masters gleich (es sei denn, diese treten nach einem zeitlich korrelierten Muster auf). Der einem Master zur Verfügung stehende Bandbreitenanteil richtet sich nach dem Verhältnis seines Requestaufkommens zur gesamten Menge an Requests pro Zeiteinheit. Damit erfüllt das Verfahren das Kriterium der Fairness nicht, da Masters mit hohem Requestaufkommen die den restlichen Masters zur Verfügung stehende Bandbreite schmälern. Die Latenz hängt stark vom gesamten Requestaufkommen ab; es kann jedoch eine obere Grenze angegeben werden, sofern der Bus so ausgelegt ist, dass pro Master nur eine begrenzte Zahl Requests gleichzeitig vorliegen kann. Obwohl der FCFS-Arbiter vom Gedanken her simpel daherkommt, kann sich seine Implementierung durch die Notwendigkeit einer zentral verwalteten Warteschlange relativ aufwändig gestalten.

#### 3.2.1.4 Request Priority Arbiter

Anstelle einer Priorisierung aufgrund der Master-Identität kann auch eine Bevorzugung anhand der Request-Identität in Betracht gezogen werden. Dies ist insbesondere dann von Interesse, wenn die auftretenden Anfragen von der Verarbeitung von Daten unterschiedlicher Dringlichkeit herrühren. Ist also ein bestimmter Master beispielsweise im Begriff, ein zeitkritisches Paket zu verarbeiten, so kann er eine unerwünschte Verzögerung beim Buszugriff durch das Markieren seiner Requests verhindern bzw. eindämmen. Über ein längeres Zeitintervall betrachtet, entsteht ein Szenario ähnlich demjenigen der statisch zugewiesenen Masterpriorität, jedoch mit dem Unterschied, dass die Masterpriorität dynamisch variieren kann. Der zusätzliche Aufwand besteht darin, vom Master eine zusätzliche Leitung zum Arbiter zu führen, welche die Priorität des aktuellen Requests signalisiert. Sofern nicht zahlreiche Prioritätsstufen gleichzeitig zum Einsatz kommen, sind bei hoher Busauslastung Konflikte von Requests gleicher Priorität zu erwarten. In diesem Fall muss der Arbiter für seine Entscheidung auf eine andere Ebene zurückgreifen können. So wird beispielsweise bei einem Patt die Masterpriorität oder ein Round-Robin-Schema zu Rate gezogen. Die Kriterien der Fairness und der begrenzten Latenz müssen dann anhand dieser zweiten Ebene beurteilt werden.

#### 3.2.1.5 Random Arbiter

Als letztes Beispiel soll hier noch der Random Arbiter aufgeführt werden. Ein solcher wählt aus den anstehenden Requests nach dem Zufallsprinzip einen aus und schert sich nicht um weitere Faktoren. Der Algorithmus ist zwar theoretisch gesehen nicht fair und verfügt auch nicht über eine begrenzte Latenz, verhält sich jedoch über längere Zeit betrachtet ähnlich wie ein FCFS-Arbiter. Seine Umsetzung verlangt die Integration eines Zufallsgenerators, was im Hinblick auf den fehlenden speziellen Nutzen unverhältnismässig erscheint. Hingegen kann der Random Arbiter als Referenzalgorithmus beigezogen werden, um in vergleichenden Simulationen die Nützlichkeit massgeschneiderter Algorithmen zu demonstrieren.

#### 3.2.2 Prioritäts- oder Bandbreiten-orientierte Algorithmen

Die vorgestellten Arbitrierungsschemen können in zwei verschiedene Klassen eingeordnet werden:

- Priority Oriented Algorithms. Arbiter, die für ihren Entscheid auf einen Prioritätsparameter zurückgreifen, sind dann angebracht, wenn der Buszugriff eines bestimmten Masters von übergeordneter Wichtigkeit ist und damit die Unterdrückung aller anderen Requests rechtfertigt. Wird die Prioritätszuordnung auf Request-Ebene vorgenommen, so macht dies beispielsweise dann Sinn, wenn in einem Netzwerkprozessor gleichzeitig priorisierte und nicht-priorisierte Pakete in Verarbeitung sind.

- Shared Bandwidth Algorithms. Soll in einem Prozessor die zur Verfügung stehende Buskapazität unter den Masters gleichmässig oder nach einem bestimmten Schlüssel aufgeteilt werden, so kann dies durch einen geeigneten Arbiter bewerkstelligt werden. An dieser Stelle sollte man zwischen Algorithmen unterscheiden, die bloss mit gewissen Einschränkungen die Kriterien der Fairness und der begrenzten Latenz erfüllen und solchen, die effektive Garantien bezüglich der pro Master zur Verfügung stehenden Bandbreite abgeben. Liegt eine klar begrenzte Latenz vor sowie eine minimale Anzahl garantierter Requests pro Zeit, so haben die Masters die Gewissheit, ihr Datenaufkommen in einer im Voraus abschätzbaren Zeit übermitteln zu können.

Von den im vorhergehenden Abschnitt beschriebenen Arbitern gehören zwei in die Klasse der Prioritäts-orientierten Algorithmen (Static Priority und Request Priority), während die restlichen der Bandbreiten-orientierten Klasse zuzuordnen sind. Unter letzteren erfüllt der (Weighted-)Round-Robin-Arbiter die Garantie-Anforderungen bezüglich minimalem Bandbreitenan-

teil und maximaler Latenz. Der FCFS-Arbiter kann mit vergleichbaren Qualitäten aufwarten, sofern die Anzahl gleichzeitig vorhandener Requests pro Master begrenzt ist.

#### 3.2.3 Mehrstufige Arbitrierung

Wie bereits erwähnt, kann es bei der Arbitrierung nach einem primären Schema zu Situationen kommen, die einen Entscheid anhand eines sekundären Schemas erfordern. Darüber hinaus ist die Verwendung von zusätzlichen Ebenen auch ein mögliches Mittel, einen differenzierteren Arbiterentscheid zu fällen, als es ein einfacher Arbiter erlauben würde. Beispielsweise könnte ein einzelner Master aufgrund seiner Wichtigkeit über alle anderen priorisiert werden, während unter den übrigen Masters ein Round-Robin-Schema für die Arbitrierung sorgt. Eine mehrstufige Praxis ermöglicht damit eine Arbitrierung, die auf die Eigenschaften des Systems und dessen Aufgabe zugeschnitten ist. Abhängigkeiten zwischen den einzelnen Systemkomponenten und Bandbreitenbedürfnissen kann dadurch optimal Rechnung getragen werden. Der Preis einer ausgeklügelten Arbitrierung ist jedoch stets die erhöhte Komplexität. Hier wird es oftmals notwendig, zugunsten einer implementierbaren Lösung Abstriche zu machen.

#### 3.3 Arbitrierung im Netzwerkprozessor

Das Thema der vorliegenden Arbeit ist die Untersuchung der Arbitrierung am konkreten Beispiel eines Netzwerkprozessors. Als Vorlage einer Prozessorarchitektur dient das in Kapitel 2 beschriebene Modell. Nun soll in erster Linie der Einfluss der Bus-Arbitrierung auf die Verzögerung der Pakete bei der Verarbeitung durch den Prozessor nachvollzogen und beschrieben werden, während in einem zweiten Schritt eine optimale Lösung in Bezug auf die Arbitrierung für verschiedene Szenarien erarbeitet werden soll.

#### 3.3.1 Ausgangslage

Für die folgende Untersuchung ist eine Paketverarbeitung im parallel ablaufenden Run-to-completion-Modus vorgesehen, d.h. mehrere Pakete werden gleichzeitig von einer Anzahl (identischer) Prozessoren verarbeitet, wobei jeweils alle auszuführenden Anwendungen vom selben Prozessor vorgenommen werden, ein einzelnes Paket also immer nur einen Prozessor durchläuft. Vor der Verarbeitung wird das Paket über die PLB-OPB-Brücke in den Speicher geschrieben, am Ende wird es wieder von der Brücke gelesen und an einen EMAC weitergeleitet. Um die Situation fürs erste möglichst über-

schaubar zu halten, wurde auf den Einsatz einer DMA-Einheit als zusätzliche Verkehrsquelle und -senke verzichtet. Weiter wird angenommen, dass alle ankommenden Pakete einer einzigen Trace entstammen, somit also keine Konflikte zwischen unterschiedlichen Input- und Output-Strömen auftreten.

Im Zentrum der Untersuchung steht die Verwaltung des Datenverkehrs auf dem PLB und ihr Einfluss auf den Paketfluss. Um sicherzustellen, dass äussere Faktoren eine untergeordnete Rolle spielen, wurde angenommen, dass die Kapazität des OPB keinen begrenzenden Faktor darstellt. Weiter wollen wir uns ausschliesslich auf Header Processing Applications (HPA) beschränken und die durchzuführenden Anwendungen für alle Pakete gleich halten. Tabelle 3.1 enthält die wichtigsten Parameter wie sie weiter unten für die Simulationen gewählt wurden.

Was den eintreffenden Paketfluss angeht, so besteht eine Variabilität in folgenden drei Punkten:

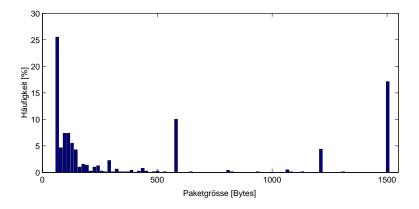

- Paketgrösse. Die Paketgrösse variiert gemäss einer vorgegebenen Internet Traffic Trace [2]. Ihre Verteilung ist in Abbildung 3.1 ersichtlich.

- Interframe Gap. Der Abstand zweier aufeinanderfolgender Pakete richtet sich nach einer Exponentialverteilung mit gegebenem Mittelwert.

- **Priorität.** Nach dem Zufallsprinzip wird ein gewisser Anteil der Pakete als priorisierte Daten markiert, welche bestimmten Quality-of-Service-Ansprüchen genügen sollen.

Es kann weiter angenommen werden, dass der Paket-Trace durch so genannte Arrival Curves Grenzen gesetzt sind in Bezug auf die Menge an Paketen bzw. Daten, die in einem gewissen Zeitintervall maximal ankommen dürfen. Eine solche Begrenzung entspricht beispielsweise den Tspec-Kurven [28].

In den betrachteten Simulations-Szenarien wurde jeweils angenommen, dass nur eine EMAC-Einheit Pakete in den Netzwerkprozessor speist und nach ihrer Verarbeitung weiter überträgt.

#### 3.3.2 PLB-Verkehr

Der zu verarbeitende Paketstrom wird auf dem PLB eine charakteristische Last erzeugen. Anhand von Abbildung 3.2, welche bereits zur Illustration des Matlab-Modells diente, soll hier genauer erläutert werden, welches Verkehrsaufkommen bei der Verarbeitung eines Pakets generiert wird (siehe dazu auch Kapitel 2, Abschnitt 2.3.6).

Abbildung 3.1: Verteilung der Paketlänge in der verwendeten Trace.

Abbildung 3.2: Verkehr auf dem PLB.

Der Prozess lässt sich in drei Etappen unterteilen: Transfer des Pakets in den Speicher, Verarbeitung des Pakets durch einen Prozessor sowie Transfer des Pakets aus dem Speicher heraus zur weiteren Übertragung.

#### 3.3.2.1 Transfer in den Speicher (Receive Path)

In dieser Etappe beginnt nach einem Zugriff des Pufferdeskriptoren-Verwalters auf den Read-Bus der eigentliche Transfer des Pakets (Header und Payload) in den Speicher. Am Schluss steht ein Status-Write-Zugriff auf den

Pufferdeskriptor-Speicher. Als Masters sind der Pufferdeskriptoren-Verwalter und vor allem die Brücke aktiv. Der überwiegende Teil des Verkehrs wird auf dem Write-Bus verursacht; bei Paketen, deren Grösse den Umfang des Headers deutlich übersteigt, ist die Buslast in etwa proportional zur Paketgrösse.

#### 3.3.2.2 Paketverarbeitung durch den Prozessor