Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

# Samuel Nobs

# **Prototype Board for Reconfigurable** OS

Student Thesis SA-2003.22 Summer Term 2003 Tutor: Herbert Walder

Supervisor: Prof. Dr. Lothar Thiele

4.7.2003

# *XFBOARD*

Institut für Technische Informatik und Kommunikationsnetze Computer Engineering and Networks Laboratory

# Contents

| 1   | Intro | oduction | 1                   | 7  |

|-----|-------|----------|---------------------|----|

|     | 1.1   | Prelimi  | naries              | 7  |

|     | 1.2   | Backgro  | ound                | 7  |

|     | 1.3   | Motivat  | tion                | 8  |

| 2   | Syst  | em Desig | gn                  | 11 |

|     | 2.1   | Target A | Application         | 11 |

|     | 2.2   | Design   | Requirements        | 11 |

|     | 2.3   | Design   | Decisions           | 12 |

|     |       | 2.3.1    | FPGAs               | 12 |

|     |       | 2.3.2    | I/O Devices         | 12 |

|     |       | 2.3.3    | Memory              | 14 |

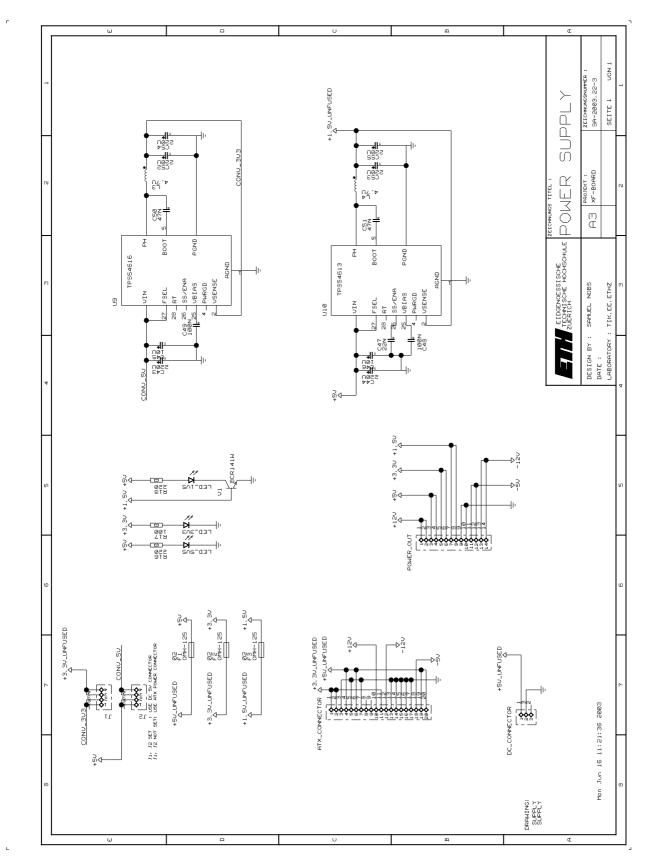

|     |       | 2.3.4    | Power Supply        | 16 |

| 3   | Sche  | ematic E | nfrv                | 19 |

| · · | 3.1   |          |                     | 19 |

|     | 5.1   | 3.1.1    | CPU FPGA            | 19 |

|     |       | 3.1.2    | Ethernet            | 20 |

|     |       | 3.1.3    | 1M x 32 SRAM        | 21 |

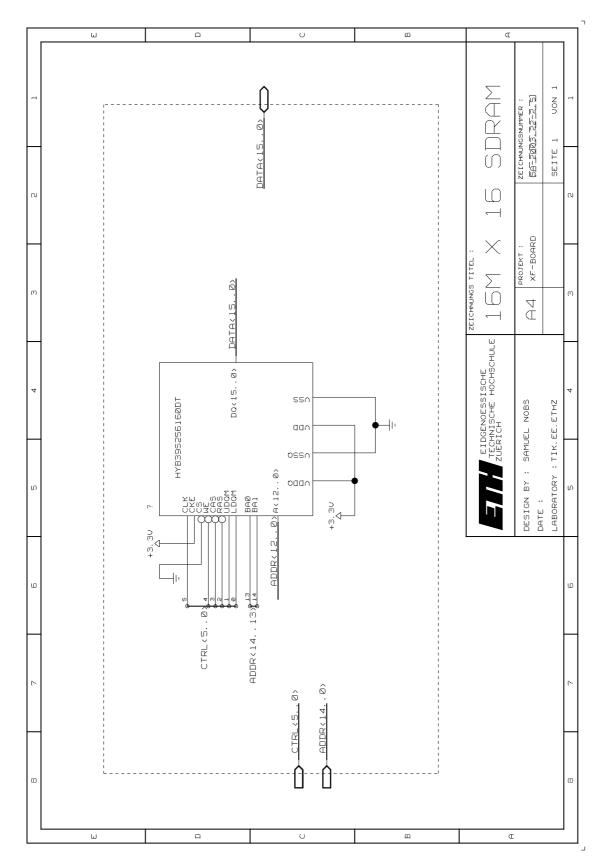

|     |       | 3.1.4    | 16M x 32 SDRAM      | 21 |

|     |       | 3.1.5    | 4M x 32 FlashRAM    | 22 |

|     |       | 3.1.6    | Keyboard and Mouse  | 22 |

|     |       | 3.1.7    | Simple VGA Output   | 22 |

|     |       | 3.1.8    | RS-232 Double Port  | 22 |

|     |       | 3.1.9    | I/O Header          | 24 |

|     |       | 3.1.10   | Switches            | 24 |

|     |       | 3.1.11   | JTAG Header         | 24 |

|     | 3.2   | XF Bot   |                     | 24 |

|     |       | 3.2.1    | Reconfigurable FPGA | 24 |

|     |       | 3.2.2    | Audio CoDec         | 25 |

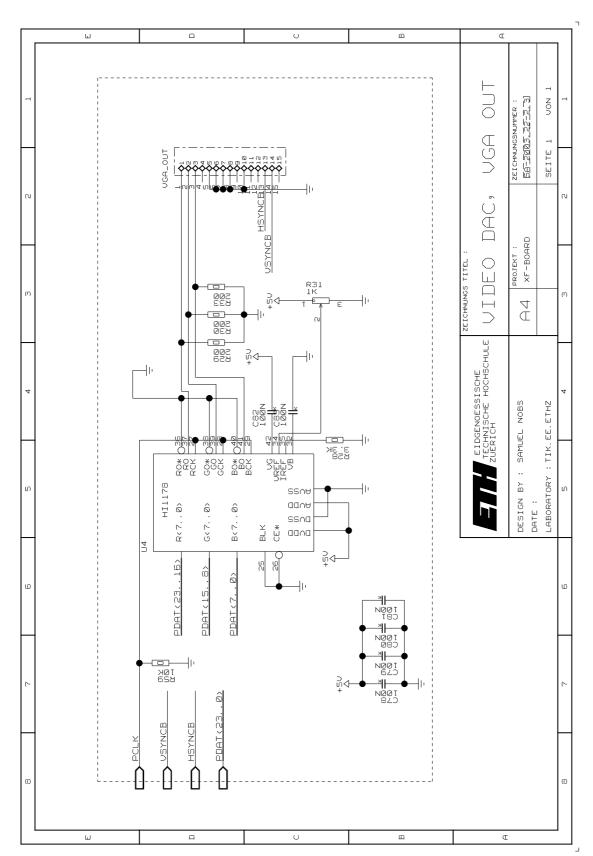

|     |       | 3.2.3    | Video DAC, VGA Out  | 26 |

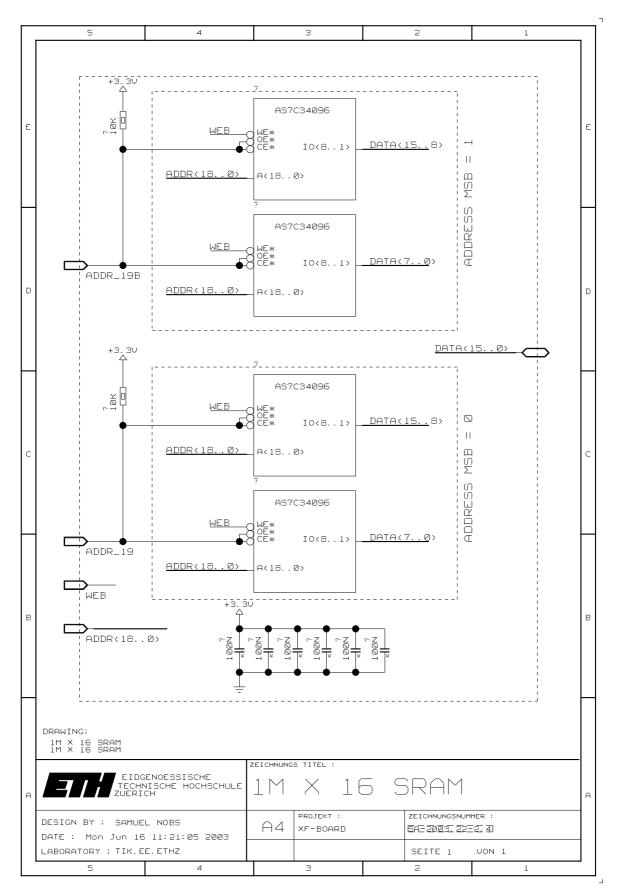

|     |       | 3.2.4    | 1M x 16 SRAM        | 26 |

|     |       | 3.2.5    | 16M x 16 SDRAM      | 26 |

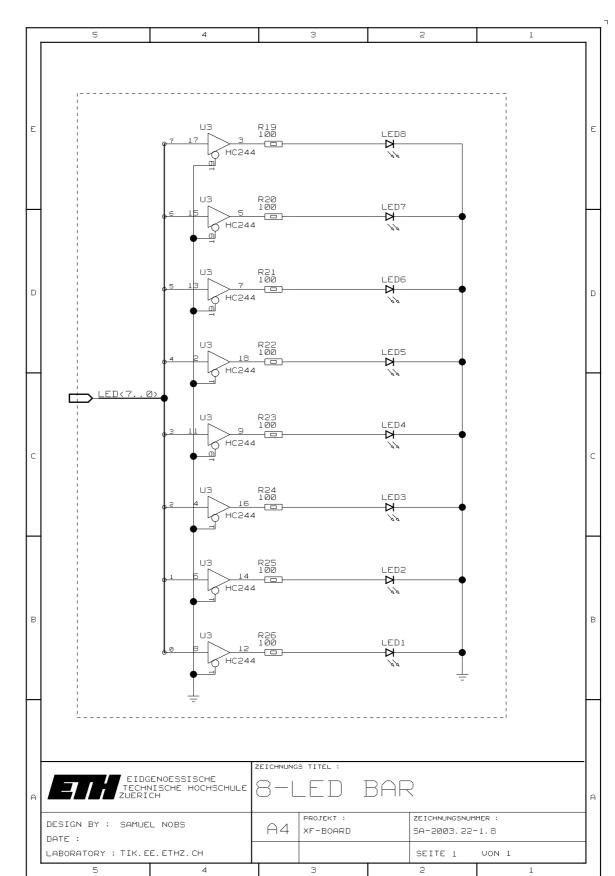

|     |       | 3.2.6    | 8-LED Bar           | 26 |

|     |       | 3.2.7    | I/O Slot            | 26 |

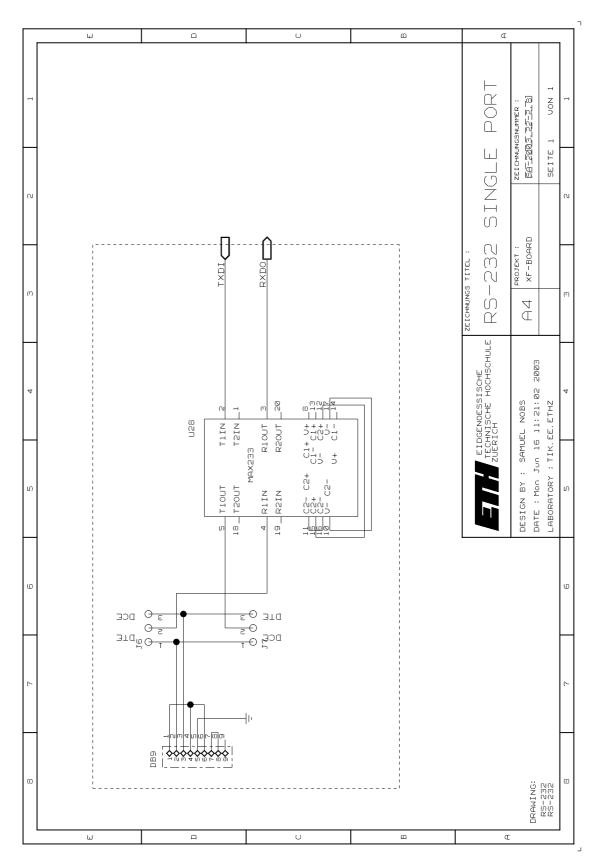

|     |       | 3.2.8    | RS-232 Single Port  | 27 |

|     |       | 3.2.9    | (Ethernet)          | 27 |

|     |       | 3.2.10   | (Switches)          | 27 |

|     |       |          |                     |    |

|   |      | 3.2.11 (JTAG Header)                                                                                                                                                                                           | 27                                                                         |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 3.3  |                                                                                                                                                                                                                | 27                                                                         |

|   |      |                                                                                                                                                                                                                |                                                                            |

| 4 | •    |                                                                                                                                                                                                                | 29                                                                         |

|   | 4.1  | 1 0                                                                                                                                                                                                            | 29                                                                         |

|   | 4.2  |                                                                                                                                                                                                                | 29                                                                         |

|   | 4.3  | Maximum Trace Length                                                                                                                                                                                           | 29                                                                         |

| 5 | Proc | gramming Model                                                                                                                                                                                                 | 33                                                                         |

| 5 | 5.1  |                                                                                                                                                                                                                | 33                                                                         |

|   | 5.1  |                                                                                                                                                                                                                | 33                                                                         |

|   |      | <b>e</b>                                                                                                                                                                                                       | 36                                                                         |

|   |      |                                                                                                                                                                                                                | 36                                                                         |

|   |      |                                                                                                                                                                                                                | 37                                                                         |

|   |      |                                                                                                                                                                                                                | 37                                                                         |

|   |      |                                                                                                                                                                                                                | 37<br>39                                                                   |

|   |      |                                                                                                                                                                                                                | 39<br>40                                                                   |

|   |      | 1                                                                                                                                                                                                              |                                                                            |

|   |      |                                                                                                                                                                                                                | 40                                                                         |

|   |      |                                                                                                                                                                                                                | 40                                                                         |

|   |      | ······································                                                                                                                                                                         | 41                                                                         |

|   |      |                                                                                                                                                                                                                | 42                                                                         |

|   |      |                                                                                                                                                                                                                | 42                                                                         |

|   |      |                                                                                                                                                                                                                | 43                                                                         |

|   | 5.2  | Development Cycle                                                                                                                                                                                              | 44                                                                         |

| 6 | Out  | look and Acknowledgements                                                                                                                                                                                      | 49                                                                         |

|   | 6.1  | Future Work and Improvements                                                                                                                                                                                   | 49                                                                         |

|   | 6.2  | Lessions Learned                                                                                                                                                                                               | 49                                                                         |

|   | 6.3  |                                                                                                                                                                                                                | 50                                                                         |

|   | G.1. |                                                                                                                                                                                                                | <b>7</b> 1                                                                 |

| A | Sche |                                                                                                                                                                                                                | <b>51</b><br>53                                                            |

|   |      |                                                                                                                                                                                                                |                                                                            |

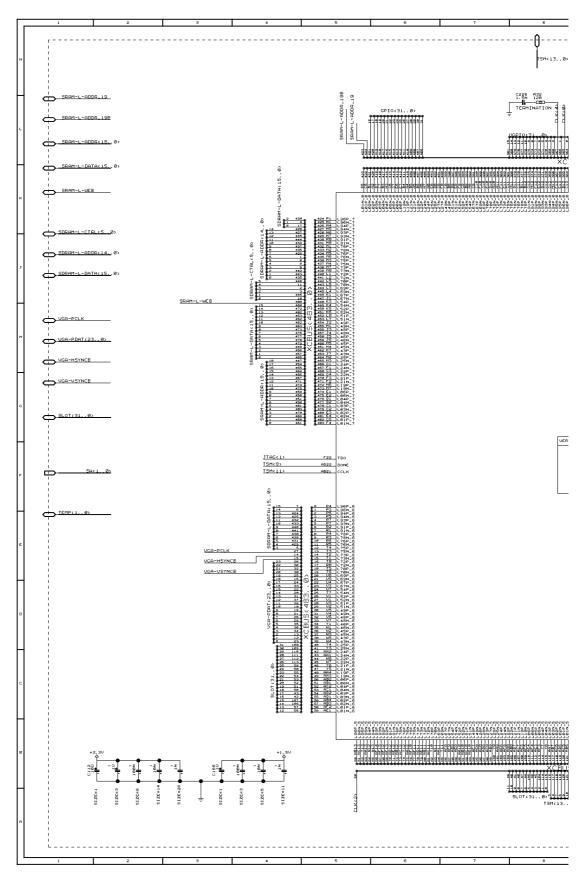

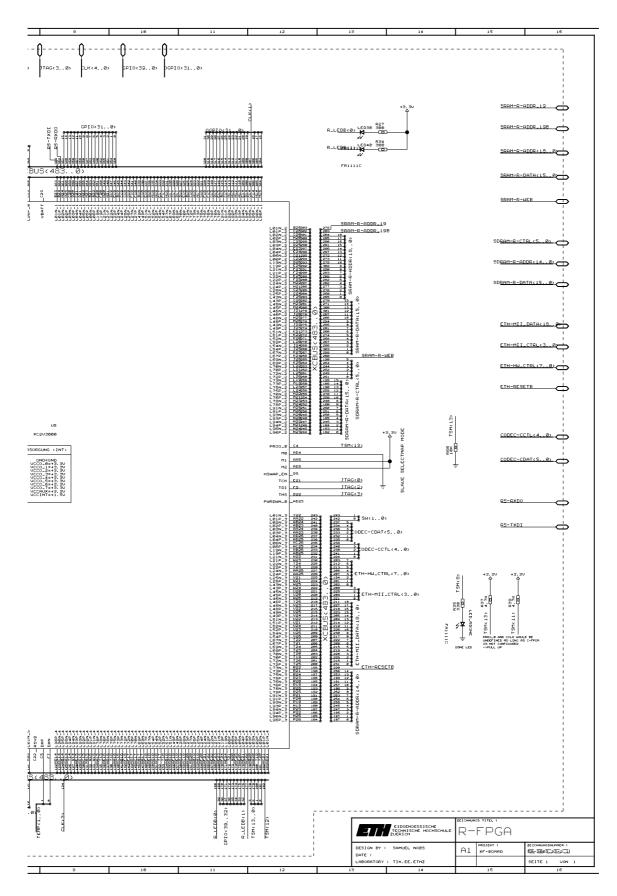

|   |      | X H- LOD                                                                                                                                                                                                       | 53                                                                         |

|   |      |                                                                                                                                                                                                                | E 1                                                                        |

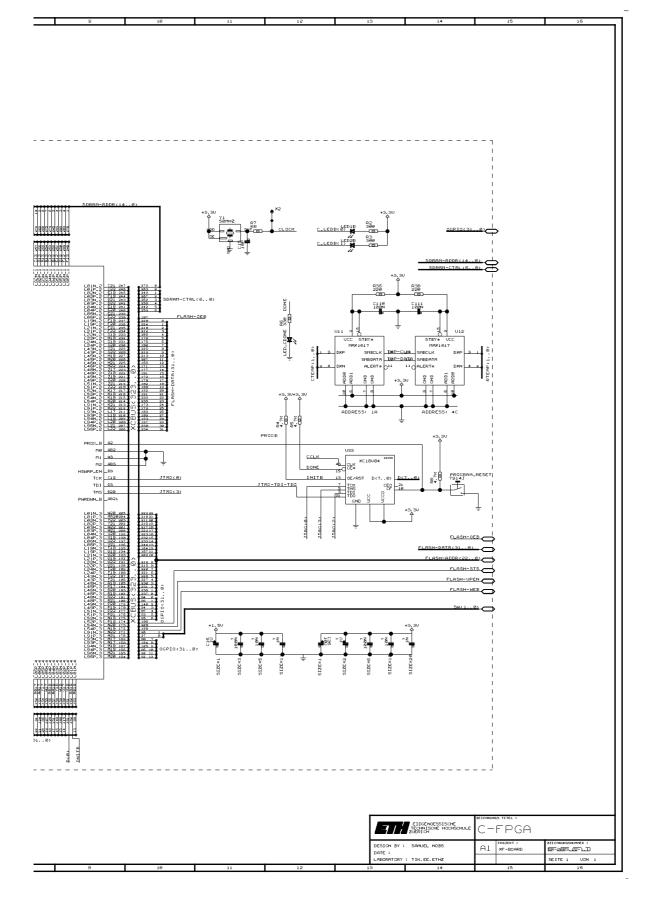

|   |      | C-FPGA                                                                                                                                                                                                         | 54                                                                         |

|   |      | C-FPGA                                                                                                                                                                                                         | 56                                                                         |

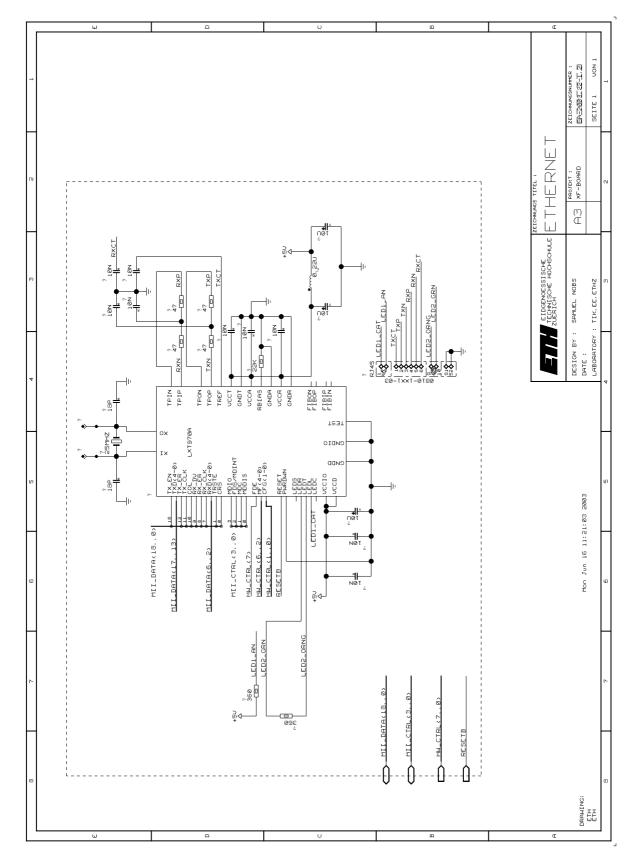

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57                                                                   |

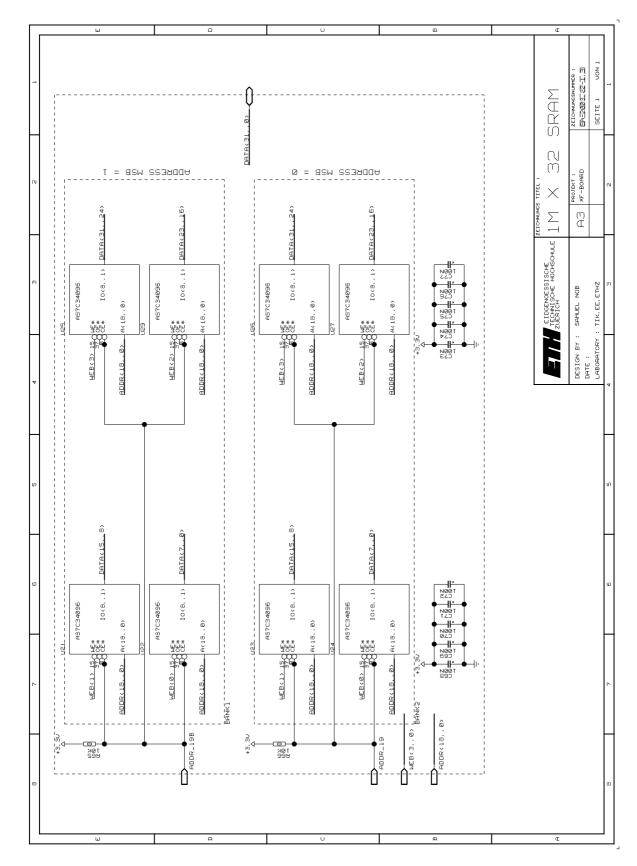

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58                                                             |

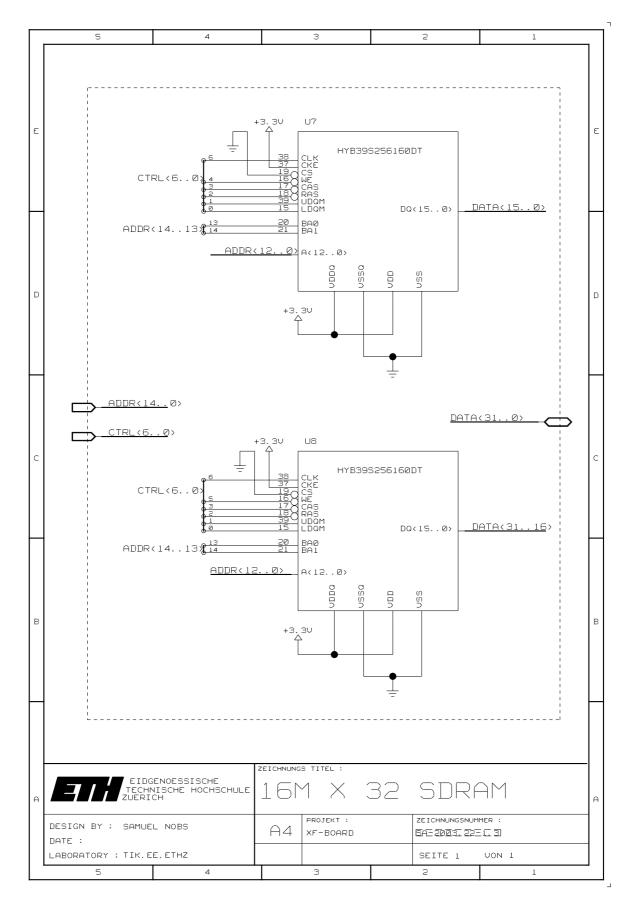

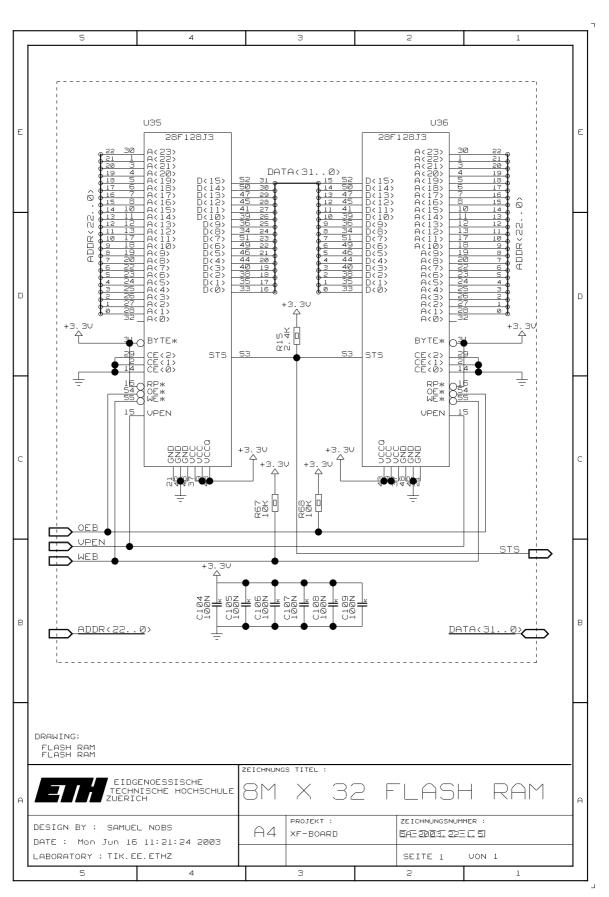

|   |      | C-FPGA<br>Ethernet<br>1M x 32 SRAM<br>16M x 32 SDRAM<br>8M x 32 FlashRAM                                                                                                                                       | 56<br>57<br>58<br>59                                                       |

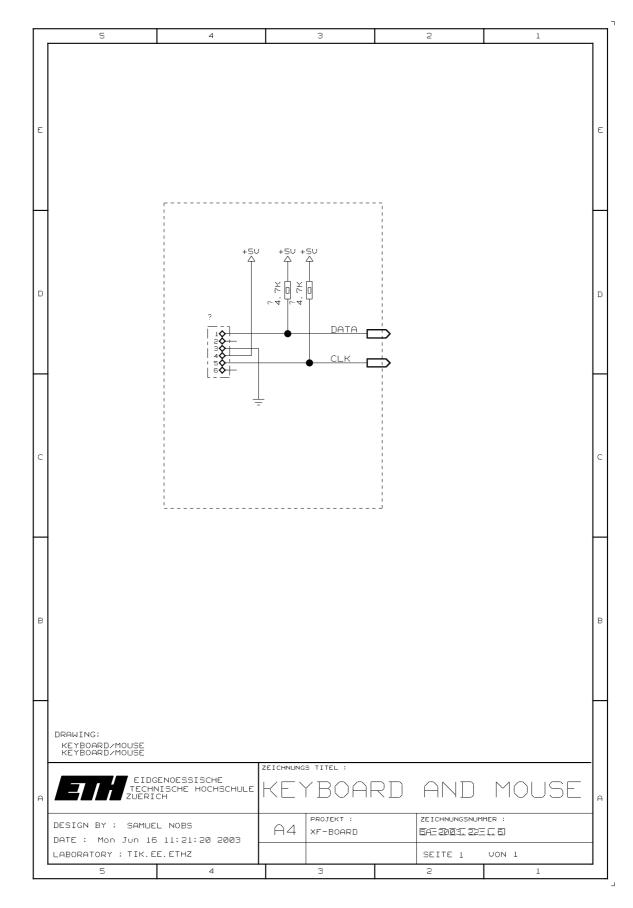

|   |      | C-FPGA<br>Ethernet<br>1M x 32 SRAM<br>16M x 32 SDRAM<br>8M x 32 FlashRAM<br>Keyboard and Mouse                                                                                                                 | 56<br>57<br>58<br>59<br>60                                                 |

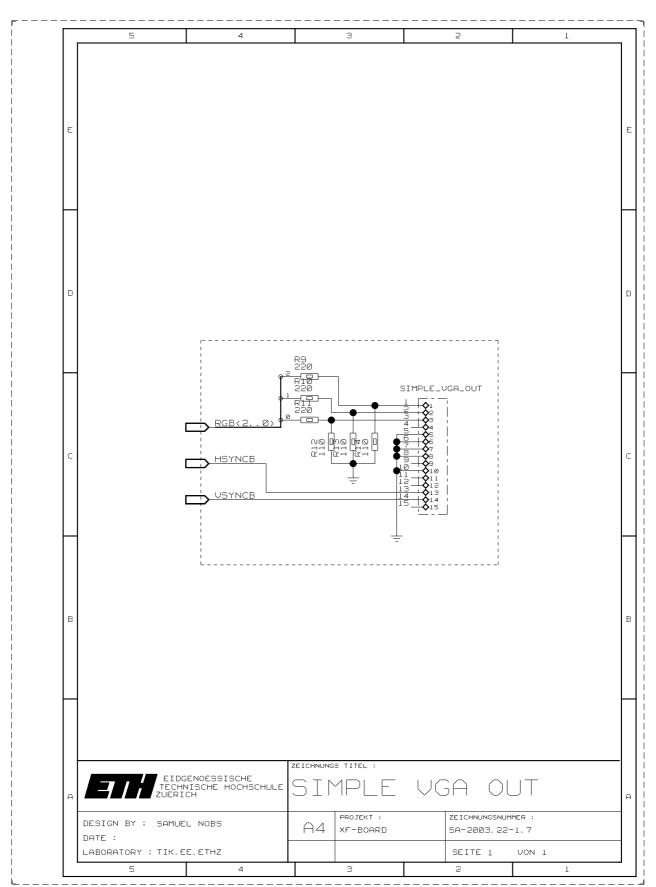

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61                                           |

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62                                     |

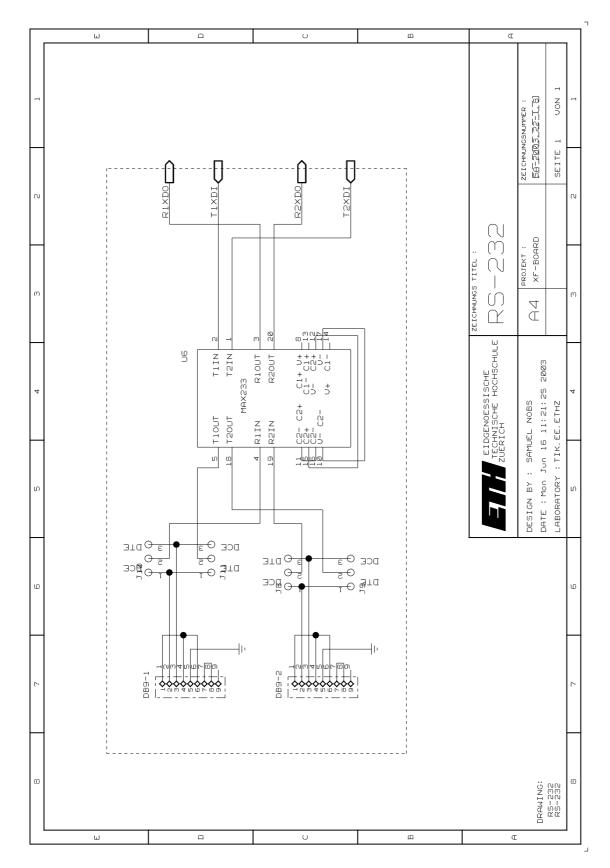

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63                               |

|   |      | C-FPGA<br>Ethernet<br>1M x 32 SRAM<br>16M x 32 SDRAM<br>8M x 32 FlashRAM<br>Keyboard and Mouse<br>Simple VGA Out<br>RS-232<br>32Pin Header<br>Switches                                                         | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64                         |

|   |      | C-FPGA<br>Ethernet<br>1M x 32 SRAM<br>16M x 32 SDRAM<br>8M x 32 FlashRAM<br>Keyboard and Mouse<br>Simple VGA Out<br>RS-232<br>32Pin Header<br>Switches                                                         | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63                               |

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64                         |

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65                   |

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66             |

|   |      | C-FPGA<br>Ethernet                                                                                                                                                                                             | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67       |

|   |      | C-FPGA<br>Ethernet<br>1M x 32 SRAM<br>16M x 32 SDRAM<br>8M x 32 FlashRAM<br>Keyboard and Mouse<br>Simple VGA Out<br>RS-232<br>32Pin Header<br>Switches<br>JTAG Interface<br>XF-Bottom<br>Audio CoDec<br>R-FPGA | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68 |

4

|     |             | 8-LED Bar                           | 73<br>74<br>75<br>77 |

|-----|-------------|-------------------------------------|----------------------|

|     |             |                                     |                      |

| B   |             | Tables                              | 79                   |

|     | <b>B</b> .1 | Pin Tables for the C-FPGA           | 79                   |

|     |             | Clock Input                         | 79                   |

|     |             | Clock Output                        | 79                   |

|     |             | Control LEDs                        | 79                   |

|     |             | Ethernet Transceiver                | 79                   |

|     |             | FlashRAM                            | 80                   |

|     |             | GPIO and LED-Bar                    | 82                   |

|     |             | OGPIO and Header                    | 83                   |

|     |             | PS/2 Ports                          | 83                   |

|     |             | RS-232 Interface                    | 84                   |

|     |             | SDRAM bank                          | 84                   |

|     |             | SelectMap connection to R-FPGA      | 85                   |

|     |             | Simple VGA Output                   | 86                   |

|     |             | SRAM bank                           | 86                   |

|     |             | Switches                            | 87                   |

|     |             | Temperature sensors                 | 87                   |

|     | <b>B</b> .2 | Pin Tables for the R-FPGA           | 88                   |

|     |             | Audio CoDec                         | 88                   |

|     |             | Clock Inputs                        | 88                   |

|     |             | Control LEDs                        | 88                   |

|     |             | Ethernet Transceiver                | 88                   |

|     |             | GPIO and LED-Bar                    | 89                   |

|     |             | I/O Slot                            | 90                   |

|     |             | left SDRAM bank                     | 91                   |

|     |             | left SRAM bank                      | 92                   |

|     |             | OGPIO and Header                    | 92                   |

|     |             |                                     | 93<br>94             |

|     |             | right SDRAM bank                    |                      |

|     |             | right SRAM bank                     | 94                   |

|     |             | RS-232 Interface                    | 95                   |

|     |             | Switches                            | 96                   |

|     |             | Video DAC/VGA Output                | 96                   |

| С   | Initi       | al Operation                        | 97                   |

|     | <b>C</b> .1 | Preparations                        | 97                   |

|     | C.2         | DC/DC Converter Tests               | 97                   |

|     | C.3         | Onboard Oscillator and Quartz Tests | 99                   |

|     | <b>C</b> .4 | JTAG Interface Tests                | 99                   |

| Bil | bliogr      | raphy                               | 101                  |

5

CONTENTS

# Chapter 1

# Introduction

This chapter offers an overview of the background and the motivation of this semester thesis. As this thesis mainly consists of designing a printed circuit board (PCB) for the desired system, the underlying concepts and theoretical aspects are not the main key of concern, therefore the corresponding texts are kept short as these topics are dealt with in other documents in detail [1],[7].

## **1.1 Preliminaries**

To prevent possible confusions, the following terms have to be defined:

- **M**, **k** In memory context, the prefix k means a factor of  $1024 = 2^{10}$ , and M means a factor of  $1024 \cdot 1024 = 2^{20}$ . When talking about throughput and bandwidth, k is equivalent to a factor of 1'000, while M means a factor of 1'000'000.

- word Throughout this text, there exist 16 bit words and 32 bit words depending on the component context.

### 1.2 Background

Silicon process technologies used for FPGA design have been constantly improved over years: layout densities and clock frequencies have been significantly increased and, in the meantime, reached a level where a 32 bit CPU including controllers and peripherals fits into such an FPGA without even using all available resources. For example, the Xilinx Virtex-II family is built on a 0.15 micron, 8-layer metal process with highspeed 0.12 micron transistors. The largest device in this family, the XC2V8000, offers 8 million system gates<sup>1</sup> in 23'296 configurable logic blocks (CLB), and the highest speed grade is suited for clock frequencies above 200 MHz.

Furthermore, current FPGA technologies allow for partial reconfiguration. This allows a device being altered in certain areas at runtime, leaving other areas untouched. So FPGAs are in a position now to be used as dynamically allocatable resources. Computationally complex hardware tasks that might be unefficiently treated by a general

<sup>&</sup>lt;sup>1</sup>System gates are a combination of logic, memory, and custom circuit resources that would be utilized in a typical design. This term is used as a measure of FPGA density

| core                                                          | area [CLB] |

|---------------------------------------------------------------|------------|

| UART [4]                                                      | 50         |

| 100-tap FIR filter [26], 12 bit data & coefficients           | 250        |

| ADPCM [5]                                                     | 250        |

| DCT [27]                                                      | 600        |

| Triple-DES processor [26]                                     | 800        |

| 256 point complex FFT [26]                                    | 850        |

| minimal protocol stack [4], Ethernet-MAC, IP, UDP             | 1050       |

| MIDI Synthesizer [6], additive, 8 harmonics                   | 1086       |

| Discrete Wavelet Transform [27]                               | 1800       |

| LEON Sparc-V8 core, 32 bit mem I/F [28], 2Kbit I-cache, 2Kbit | 2000       |

| D-cache                                                       |            |

| MPEG2 video decoder [27]                                      | 3650       |

Table 1-1: Area requirements for typical FPGA cores (mainly taken from [2])

purpose microprocessor can be implemented in dedicated hardware and loaded or unloaded on demand, boosting performance by orders of magnitude if the time lapse needed for (re-)configuration can be kept short. A selection of area requirements of such circuits, the so called HW-Tasks, is listed in table 1-1. When comparing these values with the FPGA densities available it comes clear that it is desirable to have several HW-Task running concurrently on an FPGA.

The special forms of resource allocation needed in the abovementioned application of FPGAs ask for a reconfigurable hardware operating system (RHWOS) providing an abstraction from the underlying technology by offering services like device drivers for I/O compontents (Ethernet, Audio), doing the bookkeeping about free user space on the FPGA and assign this space to HW-Tasks to be loaded, and managing task requests to internal (block RAM, FIFOs) and external memory. For more details about RHWOS's you might want to refer to [1].

## **1.3** Motivation

Configurable boards with FPGAs and CPLDs have become an important means for rapid prototyping and system development. A huge number of manufacturers (Xess, BurchED, XeSys, Memec Design, Sundance, etc.) are exploiting this market and offer a broad range of such prototype boards. None of the products found in this range fulfills the special board architecture demands of a RHWOS.

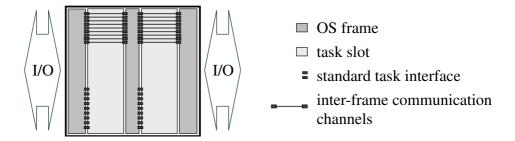

Due to the limitation of partial reconfiguration of the Xilinx FPGAs to chip scanning<sup>2</sup> and the desired topology of the architecture inside the FPGA (see figure 1-1), all I/O devices should be connected to an OS frame on the left and the right side of the FPGA. These OS frames will be left untouched during the reconfiguration process, so the connections to the I/O devices will persist. None of the commercially available boards respects this constraint.

To maximise the useability of such a board, all I/O devices and memory modules should be adressable independently, a requirement that is not consequently met on the

8

<sup>&</sup>lt;sup>2</sup>Column-wise reconfiguration

Figure 1-1: Location of FPGA I/Os suitable for RHWOS

board currently at hand, the XSV Board by XESS Corp.[8]: e.g. to use the LED bar, you have do disable the FlashRAM on the board.

The drawbacks being inherent in all these boards led to the decision to design a custom board that is tailored to the needs of a RHWOS.

CHAPTER 1. INTRODUCTION

# Chapter 2

# System Design

The design steps from the specification of the application concept and the hardware requirements of the board to the selection of design details will be rendered more precisely in this chapter. Up to that point, no schematic has been designed; please refer to chapter 3 for an explanation of the schematic.

## 2.1 Target Application

Mainly, this board will be used as a demonstrator for an RHWOS. The performance of such a system shall be proved by the implementation of computationally intensive and data trough-put-oriented tasks. These tasks can be found in the high-performance computing application domain:

- networking

- audio/video streaming

- multimedia

- encrypting/decrypting algorithms

- real-time signal processing

## 2.2 Design Requirements

The system should consist of a CPU coupled with an FPGA. The FPGA will be configured via the CPU. To allow for high-speed (partial) configuration and readback, broadband and bidirectional access to the SelectMAP configuration port (see [10] for details) is needed. The CPU needs to receive and send data (i.e. configuration bitstreams) to an external host, and some basic debugging mechanisms must be provided. Memory large enough to hold several configurations (full and partial) for the OS and for the various tasks has to be present, and this memory should be fast enough to allow for high-speed (re)configuration. For communication between the CPU and the FPGA a sufficiently high number of general purpose lines should be implemented. To allow for the target applications, I/O devices such as an audio CoDec, a video D/A-converter, an ethernet port and an additional data I/O port like RS-232 are mandatory. As the internal block RAMs of the FPGA don't offer enough capacity for most of the applications, a huge amount of external memory is needed. For the reasons mentioned in section 1.3, all I/O devices should be connected to the left and the right side of the reconfigurable FPGA.

## 2.3 Design Decisions

#### 2.3.1 FPGAs

Instead of using some standard CPU (e.g. ARM, PIC, MCore), we decided to use an FPGA and to implement a soft CPU core on it. With such soft cores, flexibility is much higher since they can be tightly adapted to our needs, and their detailed implementation may evolve during the lifetime of the *JXFBOARD*. As soon as an update of the CPU is due, there is no need to solder out the component and replace it by an other one: the new configuration is downloaded to the FPGA, and in the next second the renewed CPU is up and running. Xilinx offers a 32 bit RISC processor suitable for our needs, the MicroBlaze soft processor core [11]. This processor core can be customized using a software tool provided by Xilinx, the Embedded Development Kit (EDK).

We decided to use the Xilinx FPGAs because Xilinx is the market leader in the sector of reconfigurable logic. Also, the Computer Engineering and Networks Laboratory has been using Xilinx products for years and therefore has some experience with those devices. Moreover, almost nothing is said about other manufacturer's FPGAs in research communities and forums.

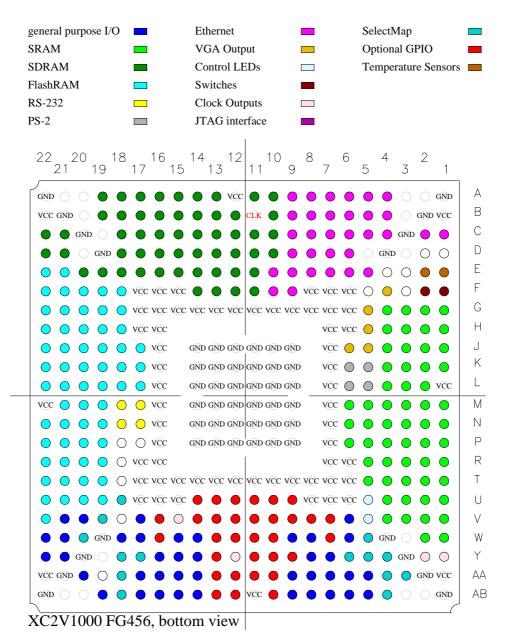

The logic area needed by the MicroBlaze and the number of I/Os (for a detailed listing refer to section 3.1.1) used by the CPU's periphery dictate the minimum size and the package of the CPU FPGA (let's call it C-FPGA from now on): a Xilinx Virtex-II XC2V1000 in the FG456 package which contains 1M system gates (for a definition of this term refer to section 1.2) and offers 324 I/Os. Since this FPGA will behave like a general purpose processor, a rather fast speed grade is needed. Speed grades -4, -5 and -6 are available, with -6 being the fastest, supporting clock frequencies above 200 MHz<sup>1</sup>. We decided to use the -5 speed grade being a good compromise between speed and cost. The C-FPGA will be offered a 50 MHz clock which can be internally multiplied by an integer fraction using the FPGA's builtin digital clock managers (DCM)[10].

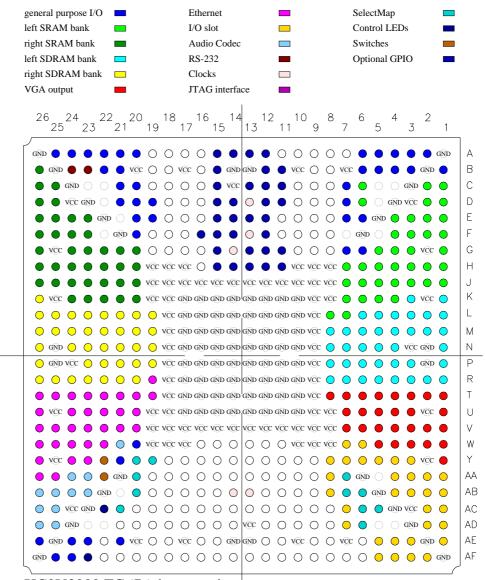

For the reconfigurable FPGA (R-FPGA), the number of I/Os used by the I/Odevices governs the package size: a Xilinx Virtex-II XC2V3000 in the FG676 package with 3M system gates and 484 I/O pins is needed due to the fact that only I/Os located at the package's left and right side may be used (refer to sections 1.3 and 3.2.1). As efficient and dedicated logic will be implemented on this FPGA, having a high clock frequency is not as crucial as with the C-FPGA, so the speed grade -4 has been chosen to prevent costs from exploding. The R-FPGA will have 4 clock frequencies offered by the C-FPGA and an additional 50 MHz clock from an external oscillator.

#### 2.3.2 I/O Devices

In this subsection, some specific characteristics of the I/O devices chosen will be denoted. For the exact device types and their manufacturers, please refer to chapter 3 and have a look at the text for the corresponding schematic.

<sup>&</sup>lt;sup>1</sup>A maximum clock frequency is not that easy to declare as the longest path in the circuit highly depends on the design implementation

#### C-FPGA

For the communication from the external host to the C-FPGA, mainly used for the transmission of configuration data, a 100Mbps fast ethernet transceiver with an RJ45 connector has been selected.

To download the bitstream to the configuration PROM, a JTAG test access port is present. The C-FPGA is also connected to this JTAG chain to allow for an emergency configuration if all other means failed.

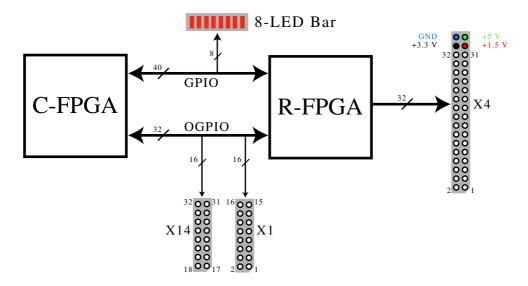

To communicate with the R-FPGA, a general purpose I/O (GPIO) bus is installed. This GPIO is 40 bits in width, e.g. for 32 bit data and 8 control signals. Additional 32 bits, the optional general purpose I/O (OGPIO), may be used if partial reconfiguration of the R-FPGA is not needed. Moreover, two 16 pin expansion headers are connected to the OGPIO bus that may be used even when partial reconfiguration of the R-FPGA is used.

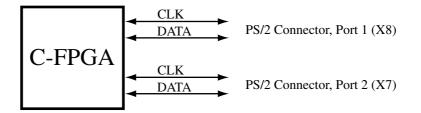

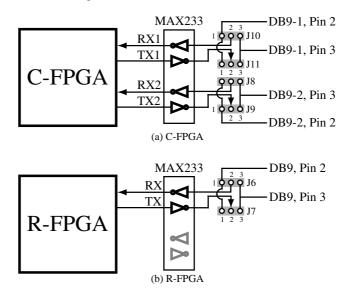

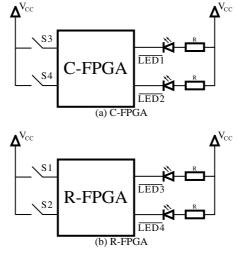

The following debugging channels are provided: for a very basic input and output, two push-buttons and two LEDs are present on the board. For advanced debugging, two PS/2 connectors for a mouse and a keyboard and a simple 8 color VGA Output<sup>2</sup> are installed. For debugging using a host PC, two RS-232 ports can be accessed. An 8-LED bar monitors the level of 8 out of the 40 GPIO signals; this LED bar may be used for visual feedback. The two 16-pin headers connected to the OGPIO are available for debugging purposes, too.

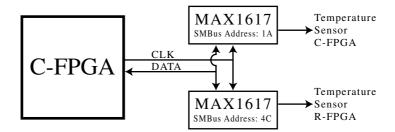

Temperature sensors to monitor the core temperature of both FPGAs are installed.

#### **R-FPGA**

A 100Mbps fast ethernet transceiver with an RJ45 connector is used to send packets to the R-FPGA and to receive packets from the R-FPGA. This ethernet port is essential for all streaming and networking applications.

The R-FPGA is planned to be configured by the C-FPGA using the SelectMAP configuration method. In case of failure of this method, this task can be accomplished using the separate JTAG test access port for the R-FPGA.

For audio and signal processing applications, an audio CoDec working with CDquality<sup>3</sup> audio data is installed. Two inputs and one output are available. Two inputs are needed whenever adaptive filtering of stereo signals is needed. The inputs and outputs can be used concurrently.

For video output, a VGA port driven by a video DAC is mounted to the **DXFBOARD**. This DAC has three separate 8 bit pixel inputs, one each for red, green and blue video data. This DAC does not contain a built-in color lookup table, as this table may be implemented using the on-board memory or the SelectRAM blocks of the R-FPGA, if needed.

An RS-232 port is installed for communication with a host PC or another RS-232aware device. This port can be used for debugging.

As mentioned above, the R-FPGA is connected with the C-FPGA by a 40 bits wide GPIO bus and a 32 bits wide OGPIO bus that may be used if the R-FPGA is not used for reconfiguration.

For a simple visual output, an 8-LED bar is connected to the GPIO signal. Furthermore, there are two push-buttons and another 2 LEDs connected for basic input and

$<sup>^{2}</sup>$  for 8 colors, the video DAC can be omitted. The red, green and blue signals may be directly fed with logic signals that have accurate levels.

<sup>&</sup>lt;sup>3</sup>44.1 kHz sampling frequency, 16 bit quantization.

output purposes.

A 36 pin expansion header is with 32 data lines, 3 power lines (+5 V, +3.3 V, +1.5 V) and a common ground can hold any extension board supporting 3.3 V LVC-MOS signal levels.

#### 2.3.3 Memory

#### **Memory Types**

As memory requirements highly differ between the various HW-Tasks and the CPU duties, we decided to use various memory types on the **DXFBOARD**. Furthermore, there exist a significant tradeoff between memory speed an costs per bit. In other words, the faster your memory is, the lower the memory size you get for the same amount of money. These considerations combined with some FPGA-intrinsic conditions led to the following memory selection:

- *SelectRAM blocks*. The fastest memory available on the board will be the FPGA's built-in SelectRAM blocks as the signal propagation paths are pretty short and these blocks can be clocked at the FPGA's system clock because they behave like registers. The fact that these RAMs are dual-ported is responsible for a substantial speed-up too. The number of such blocks is determined by the FPGA's type and size, the dimension of the SelectRAM blocks is not a completely free design parameter.

- *Static RAM (SRAM)*. For fast computations needing not too much memory space, fast static RAM is needed. SRAM works with a fast and simple protocol to read and write data. As a drawback, these memory modules are large and expensive compared to SDRAM.

- Synchronous Dynamic RAM (SDRAM). For operations on large amounts of data with moderate speed, SDRAM is the correct type of memory. SDRAM is cheap, and they are available in higher densities than SRAM. The amount of storage bits fitting into a given package size when using SDRAM is the 16<sup>th</sup> fold of the density possible with SRAM technology. The SDRAM data transfer is not as simple as with SRAM modules and needs more clock cycles for a read or write transaction. Fortunately, they support a so-called burst mode where larger amounts of contiguous data may be read or written, one word on each rising edge of the clock<sup>4</sup>, which speeds up the data transfer.

- *FlashRAM*. To hold configuration bitstreams and application data even when no power supply is present, some non-volatile RAM modules are needed. FlashRAM is our choice because of the simple protocol used to read and write data. By mischance, access speed is very low, so these modules are even slower than the SDRAM elements. FlashRAM is rather expensive, but high densities are available.

- *Configuration PROM*. To enable automatic configuration of an FPGA on powerup, a configuration PROM that will hold the corresponding bitstream must be

$<sup>^4</sup>$ The modules present on the board (see section 3.2.5) allow for a burst length of at most 8 consecutive words

installed. As soon as the power supply is present, the FPGA will read the corresponding data from the PROM. The PROM must be programmable from the outside world.

For high-speed computations, ZBT-RAM has been considered which is able to follow a read cycle by a write cycle<sup>5</sup> without the obligatory idle cycle known from regular SRAM modules. But the speed increase is not that extraordinary to justify the significantly higher expenses yielded by ZBT-RAM.

#### Memory Structure C-FPGA

To load the MicroBlaze CPU soft core and a minimal bootstrap, a configuration PROM is connected to the C-FPGA. A full configuration bitstream for the XC2V1000 is 499 kB in size [14], so a module providing 512 kB is adequate. To store the microcode for the CPU, the SelectRAM blocks are extended with external SRAM memory. This memory will be used for the buffers of the ethernet protocol stack too. We decided to implement a generous 4 MB SRAM memory to allow for fairly large programs to be run on the MicroBlaze while still leaving enough free space for the ethernet protocol stack and eventually some frames for the VGA-Output.

As the VGA-output meant for debugging purposes only supports 8 colors (3 bits), we need the following amount of memory, assuming a resolution of 640 by 480 pixels:

$640 \cdot 480 \text{ px} \cdot 3 \text{ bit} = 112.5 \text{ kB}$

Several configuration bitstreams for the R-FPGA will be stored in the non-volatile FlashRAM, because at least the RHWOS must not be lost whenever a shut-down occurs. A full configuration bitstream for the XC2V3000 is 1.25 MB in size [14], so 16 MB of FlashRAM can hold 12 full configurations and even more partial configurations, which will be sufficient. The access times for FlashRAM are too high to enable a satisfyingly fast (re)configuration, so we decided to have the CPU load the configuration data from the FlashRAM into the SDRAM on startup, where it may be read from much faster. Alternatively, the SDRAM may be used as a video frame buffer too.

As a consequence of the MicroBlaze's 32 bit architecture, all memory modules are connected to provide 32 bit words.

| memory type        | C-FPGA         | R-FPGA         |

|--------------------|----------------|----------------|

|                    | (32 bit words) | (16 bit words) |

| SelectRAM Blocks   | 90 kB          | 216 kB         |

| SRAM               | 4 MB           | 4 MB           |

| SDRAM              | 64 MB          | 64 MB          |

| FlashRAM           | 16 MB          | 16 MB          |

| Configuration PROM | 512 kB         | -              |

Table 2-1: Memory Sizes present on the Board

#### Memory Structure R-FPGA

Because the R-FPGA gets configured by the C-FPGA, there is no need for memory holding configuration data at all, so there is no PROM and no FlashRAM connected

<sup>&</sup>lt;sup>5</sup>and vice versa, of course

with the R-FPGA. For fast computations with moderate memory requirements, some SRAM is needed, and as a bulk memory to store larger amounts of data, SDRAM is used. To allow for as much parallelity and concurrency as possible, SRAM and SDRAM are each split in two halves to form two physically independent banks: if we had a handful of tasks one of which is time critical, one memory bank might be dedicated to that particular task while serving the other tasks with the second bank.

To calculate the proper dimension of the memory, we picked the target application consuming most of the memory: multimedia and video operations. To store one frame in the SRAM,

$$640 \cdot 480 \,\mathrm{px} \cdot 16 \,\mathrm{bit} = 600 \,\mathrm{kE}$$

are needed, assuming a resolution of 640 by 480 pixels and a 16 bit quantization of the color space<sup>6</sup>. Keeping this number in mind, 2 MB memory should be sufficient for each SRAM bank, providing enough space for 3 video frames at a time for fast and computation intensive video processing. As soon as it comes to buffering (frame buffering, video streaming), much more memory is needed, as the following calculation reveals:

$640 \cdot 480 \text{ px} \cdot 16 \text{ bit} \cdot 25 \text{ fps} = 14.7 \text{ MB}$

must be available to buffer one second of uncompressed video material, assuming a frame rate of 25 fps which corresponds to the PAL standard. As timing requirements are not that demanding for buffering purposes, buffering will be performed using SDRAM. So 32 MB per SDRAM bank, equivalent to 2 s buffering time, should be adequate.

The other half of multimedia, the audio sector, is not that challenging, as the memory space needed for one second of audio material in CD quality is only

44.1 kHz 16 bit 2 channels = 172 kB

Consistent with most signal processing applications, all memory devices are connected to work with 16 bit words. For an overview of the memory types and their dimensions refer to figure 2-1.

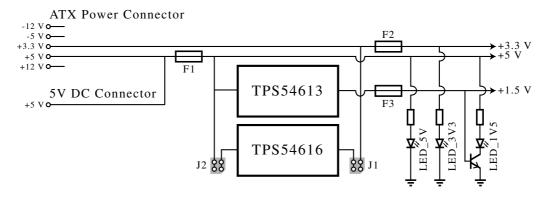

#### 2.3.4 Power Supply

We decided to use standard PC power supplies with a 20-pin ATX connector for the **XFBOARD**. Since the XESS board uses the same supply, the it may be used for the **XFBOARD**. The ATX supply delivers +3.3 V and +5 V, so the only voltage that has to be generated is +1.5 V. This voltage gets derived from the +5 V present on the ATX connector. All voltages on the ATX connector,  $\pm 12$  V,  $\pm 5$  V and  $\pm 3.3$  V, are tied to an additional header which may be used to feed external devices, e.g. a hard drive.

Alternatively, we decided to include a connector for a +5 V supply, because these low voltage supplies with only one fixed voltage are much more handy than the large ATX devices. Whenever this option is chosen, the +3.3 V also have to be derived from the +5 V provided by the +5 V feed.

Please read section 5.1.13 carefully for a detailed description on how to connect the power supply as any connection error may destroy the circuit!

16

$<sup>^{65}</sup>$  bits for the red color information, 5 bits for blue and 6 bits for green due to our eye's increased sensitivity for green light

#### 2.3. DESIGN DECISIONS

There is an LED for each voltage on the **JXFBOARD** which is lit when the corresponding voltage is present. For current measurements, there are fuses that may be removed to open the circuit to connect measurement gear.

# Chapter 3

# **Schematic Entry**

This chapter explains the schematic of the *IXFBOARD*. It basically describes the schematic sheets in appendix A. The numbering of the sections is consistent with the numbering of the corresponding sheet in all digits except the first one, e.g. section 3.1.4 delineates the sheet with the drawing number SA-2003.22-1.4. For rather conceptual considerations and reasons for the presence of particular I/O components refer to section 2; especially section 2.3 might serve your needs .

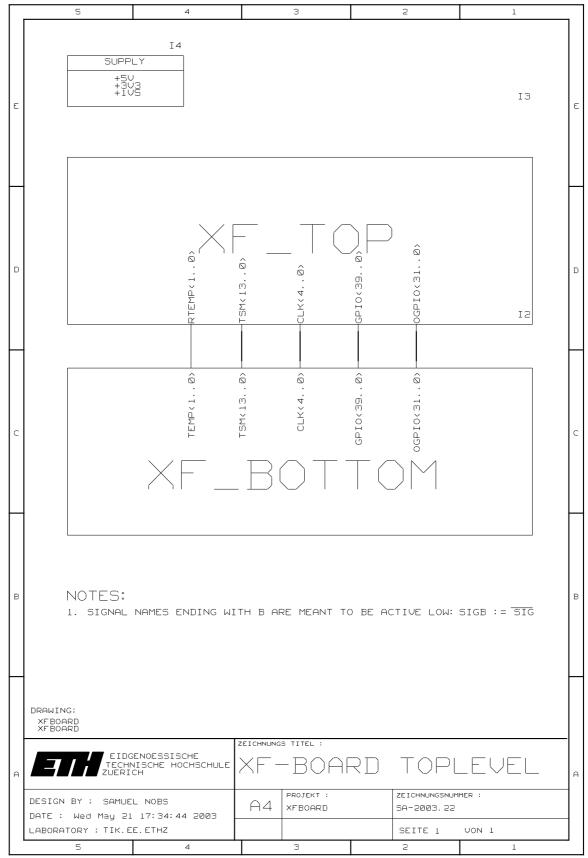

## **3.1 XF Top**

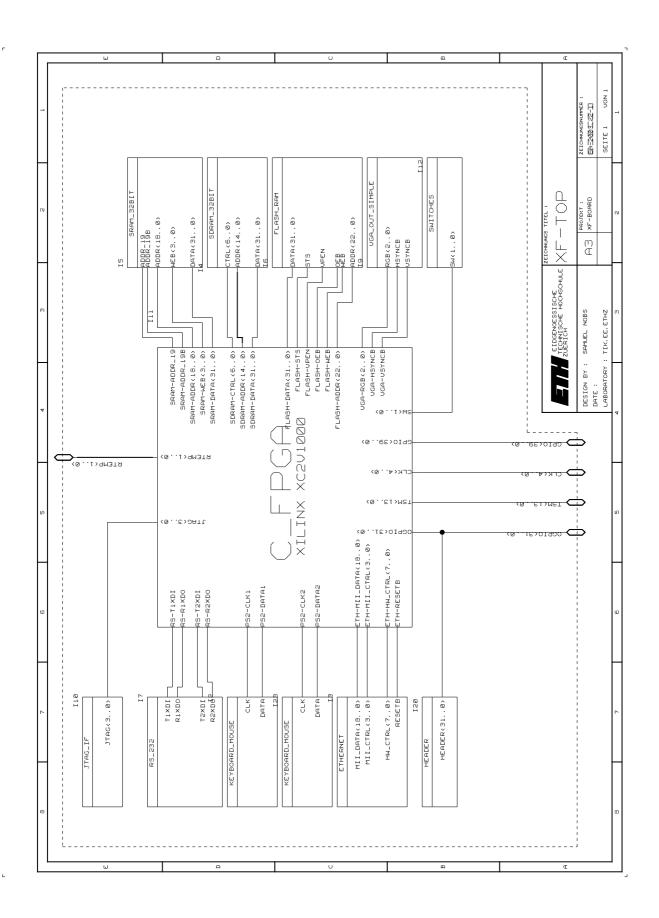

#### 3.1.1 CPU FPGA

The FPGA used as the boards CPU and configuration mechanism for the board's reconfigurable part is an XC2V500 of the Virtex-II series by Xilinx [9]. As this device has a huge number of I/O's, decoupling of the  $V_{CC}$  pins is crucial. Following Xilinx's application note on power distribution systems design [12], the number of decoupling capacitors needed highly depends on the application and the number of I/O's used simultaneosly. Due to the fact that the device is reconfigurable, the I/O usage is hardly predictable. To play it safe, I decided to assume full I/O usage, i.e. all I/O's available are used. This indeed overly pessimistic assumption results in the need for approximately one capacitor per  $V_{CC}$  pin. Given the number of discrete capacitors needed, a distribution of capacitor values adding up to that total number must be determined. Fortunately [12] does give me a hand: 50% of the total number of capacitors needed should be covered by 0.001  $\mu$ F capacitors, and this number should be divided by two for every decade of increase in size up to 100  $\mu$ F. This calculation yields the distribution shown in table 3-1. As my assumption concerning I/O usage is rather pessimistic I took the liberty of rounding off any noninteger result.

The FPGA is connected to be configured in Master Serial mode as described in the Virtex-II user guide [10]. Configuration data is read from an XC18V04 configuration PROM by Xilinx [14] which is connected to the same JTAG chain as the FPGA, being the first element in the chain and the FPGA the second element. A reset facility is provided by the program reset button, erasing the FPGA and initiating the configuration process. DONE and INIT are pulled to  $V_{CC}$  to guarantee defined signal levels at any time. To monitor the status of DONE, an LED is installed.

As there is no need for runtime reconfiguration of this FPGA, all I/O pins except

| Capacitance value | $V_{CC_{int}}$ pins | $V_{CC_o}$ pins |

|-------------------|---------------------|-----------------|

| 10.0 µF           | 0                   | 1               |

| 1.0 µF            | 1                   | 2               |

| $0.1  \mu F$      | 3                   | 6               |

| 0.01 µF           | 5                   | 10              |

| 0.001 μF          | 11                  | 20              |

Table 3-1: Number of decoupling capacitances used for the C-FPGA

| Device                         | Pin Count |

|--------------------------------|-----------|

| VGA Port                       | 5         |

| Switches                       | 2         |

| Control LEDs                   | 2         |

| Ethernet Tx/Rx                 | 32        |

| RS-232 Double Port             | 4         |

| 2x PS/2 Port                   | 4         |

| SRAM                           | 57        |

| SDRAM                          | 54        |

| FlashRAM                       | 59        |

| Clock                          | 1         |

| Clocks for R-FPGA              | 4         |

| Configuration                  | 2         |

| SelectMAP connection to R-FPGA | 14        |

| General Purpose I/O            | 40        |

| Optional General Purpose I/O   | 32        |

| Temperature Sensors            | 2         |

| Pins used                      | 314       |

| Pins available                 | 324       |

| Pins left unused               | 10        |

Table 3-2: Pin accounting for the C-FPGA

for those dedicated to the Master Serial configuration mode can be used. A summary of the pin usage is given in table 3-2.

To allow simple optical signalling and monitoring, active low LEDs are connected to two I/O's. The 50 MHz oscillator providing the clock for the two FPGAs is also included in this schematic.

The clock signal coming from the quarz oscillator is AC terminated as recommended in [25]. AC termination adds a capacitive load to the driver and a delay due to the RC time constant, however, it consumes low power. The termination elements have to be placed as near as possible to the FPGA's clock input pin in the layout.

#### 3.1.2 Ethernet

The **JXFBOARD**'s Ethernet Tx/Rx Block has been built around the LXT970A Ethernet PHY by Intel [16] which supports full-duplex operation at 10 and 100 Mbps. The

fact that we decided to use the 0810-1XX1-03 Integrated Connector Module by Bel Fuse Inc.[15] made my life much more easier as this module includes the magnetics needed for operation. Additionally, it features two LEDs for signalling purposes. Some concepts have been adopted from the XSV manual [8].

Because the driver level of the PHY's Media Independent Interface (MII) is reduced, no termination resistances are needed at its outputs. The inputs for the fiber transceiver are left unconnected as we don't use the fiber interface.

The yellow LED of the connector module is connected to the active low pin LEDL of the PHY to indicate Link Valid status during 10 Mbps operation, and scrambler lock and receipt of valid idle codes during 100 Mbps operation, respectively. The two-color LED is connected to the active low pins LEDT and LEDR to indicate receiver activity with green light and transmitter activity with orange light.

The decoupling of the supply pins has been implemented as suggested in Figure 21 (Typical Interface Circuitry) in [16]. For debugging purposes, test pins have been provided at the quarz inputs of the Ethernet PHY, IX and OX.

#### 3.1.3 1M x 32 SRAM

We decided to use the AS7C34096 by Alliance Semiconductor [20] for the SRAM block. As this memory module offers 512k halfwords (512k x 8 bits), I needed to merge the address space of two such blocks to get the desired 1M addresses. To get 32 bit words instead I had to connect two such pairs in parallel and concatenate their 8 bit data ports to the 32 bit wide signal DATA<31..0>.

To merge the address space of two such blocks, two alternatives have been considered:

• Extend the address width from 19 to 20 bits and use the MSB as a chip enable signal for the modules, inverted for the first module and non-inverted for the second module.

While it would be nice to have a block looking like a 1M x 32 bits block from the outside, the drawback of this approach is the glue logic needed: the inverter is likely to introduce some unwanted delay in the order of 2-5 ns. As the memory modules used offer cycle times of 15 ns, this approach is not an option.

• Preserve the address width as it is and use two additional signals to select and deselect the appropriate memory module.

Using this approach I don't need any glue logic, but there is now the possibility to have both memory modules enabled by mistake, resulting in bus contention in read mode. To avoid potential damage, the memory manager implemented in the FPGA has to guarantee never to activate both memory modules at a time.

Following this second approach, the memory block now has the address inputs ADDR<18..0> for the first 19 address bits and  $ADDR_19$  and  $\overline{ADDR_19}$  for the MSB. For this purpose, there is no need to drive  $\overline{CE}$  and  $\overline{OE}$  with different signals, so these two inputs are shorted.

#### 3.1.4 16M x 32 SDRAM

To get 32 bit wide memory entries, two HYB39S256160CT by Infineon Technologies [21] had to be connected in parallel because these devices offer 16M x 16 bit.  $\overline{CS}$  is tied to GND and CKE to  $V_{CC}$  to permanently enable the memory modules.

| Pin Number | Function      |

|------------|---------------|

| 1          | Data          |

| 2          | Not connected |

| 3          | GND           |

| 4          | VCC           |

| 5          | Clock         |

| 6          | Not connected |

Table 3-3: Pin assignment for the 6 pin Mini-DIN connector

#### 3.1.5 4M x 32 FlashRAM

The FlashRAM used in this circuit consists of Intel's 28F640J3 StrataFlash devices [24] which is organized as 16M x 8 bit or 8M x 16 bit. To get 8M x 32 bit, 2 such devices are connected in parallel, and the  $\overline{\text{BYTE}}$  pins are tied to +3.3 V to enable 8M x 16 bit operation. In 8M x 16 bit operation, A<0> is ignored, so A<23..1> is connected to ADDR<22..0>.

CE0, CE1 and CE2 are tied to GND and  $\overline{RP}$  is connected to +3.3 V because there is no need to deactivate the device. Also,  $\overline{OE}$  is connected to GND because we don't want to deactivate the outputs as there is no other device that might want to drive these signals.

The status signal STS is an open drain output and is high impedance when the device is ready, so the two pins can be shorted and pulled up using a resistor. So STS is high only when both devices are ready.

#### 3.1.6 Keyboard and Mouse

For the PS/2 ports, no additional components are needed except for two pullup resistors as the DATA and CLK signals are connected to an open drain output. For the connector pin assignment refer to table 3-3.

#### 3.1.7 Simple VGA Output

A very simple 8 color VGA signal can be generated without even the use of a video DAC by connecting three digital 1 bit signals directly to the connector. Refer to table 3-4 for information on connector pin assignment.

#### 3.1.8 RS-232 Double Port

The transmitting and receiving pins TXDI and RXDO are brought to the correct signal level using the Maxim MAX233A [17] and connected to RD and TD at the DB9 connector (for pin assignment refer to table 3-5).

While the normal PC hardware might well run with just TD, RD and GND connected, most driver software will wait forever for one of the handshaking lines to go to the corrrect level. Depending on the signal state it might sometimes work, other times it might not. The reliable solution is to loop back the handshake lines if they are not used. When the lines are handshake looped, the RTS output from the PC immediately activates the CTS input - so the PC effectively controls its own handshaking. For this reason I connected RTS with CTS and DTR with DSR and DCD.

| Pin Number | Function         |

|------------|------------------|

| 1          | Red              |

| 2          | Green            |

| 3          | Blue             |

| 4          | Monitor ID bit 2 |

| 5          | GND              |

| 6          | GND              |

| 7          | GND              |

| 8          | GND              |

| 9          | Not connected    |

| 10         | GND              |

| 11         | Monitor ID bit 0 |

| 12         | Monitor ID bit 1 |

| 13         | Horizontal sync  |

| 14         | Vertical sync    |

| 15         | Not connected    |

Table 3-4: Pin assignment for the VGA DB15 high density connector

| Pin Number | Short Name | Function            |

|------------|------------|---------------------|

| 1          | DCD        | Data Carrier Detect |

| 2          | RD         | Received Data       |

| 3          | TD         | Transmit Data       |

| 4          | DTR        | Data Terminal Ready |

| 5          | GND        | Signal Ground       |

| 6          | DSR        | Data Set Ready      |

| 7          | RTS        | Request To Send     |

| 8          | CTS        | Clear To Send       |

| 9          | RI         | Ring Indicator      |

Table 3-5: Pin assignment for the RS-232 DB9 connector

Often it is desirable to interchange the RD and TD lines of the connector. Two jumpers have been provided for that purpose.

#### 3.1.9 I/O Header

Two 16 pin headers are connected to the optional general purpose I/O lines which may be used to extend the capabilities of the board

#### 3.1.10 Switches

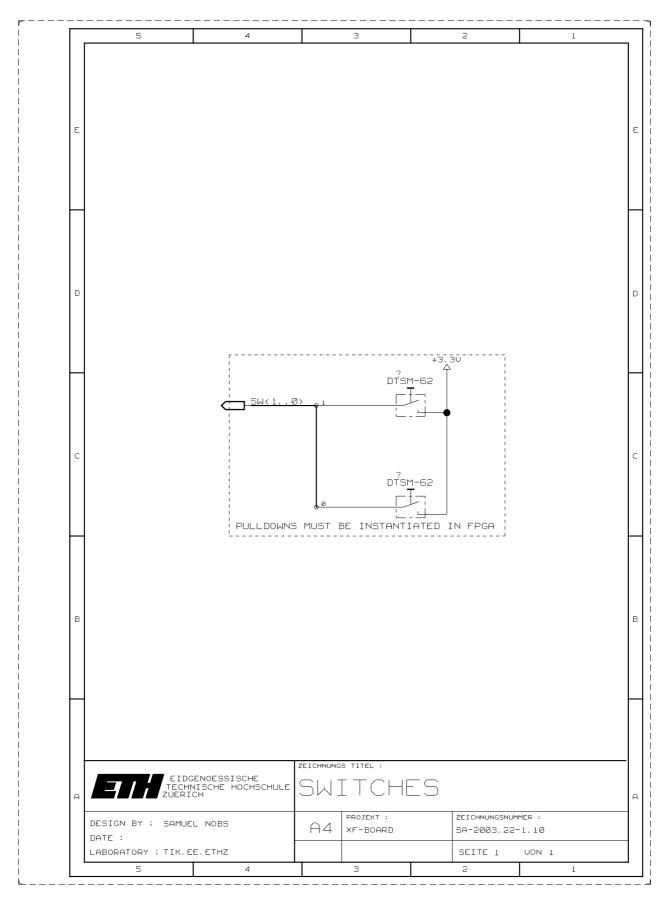

Two push buttons are present to provide means for simple user input. As there are no external pull-up resistors installed, they must be instantiated in the FPGA.

#### 3.1.11 JTAG Header

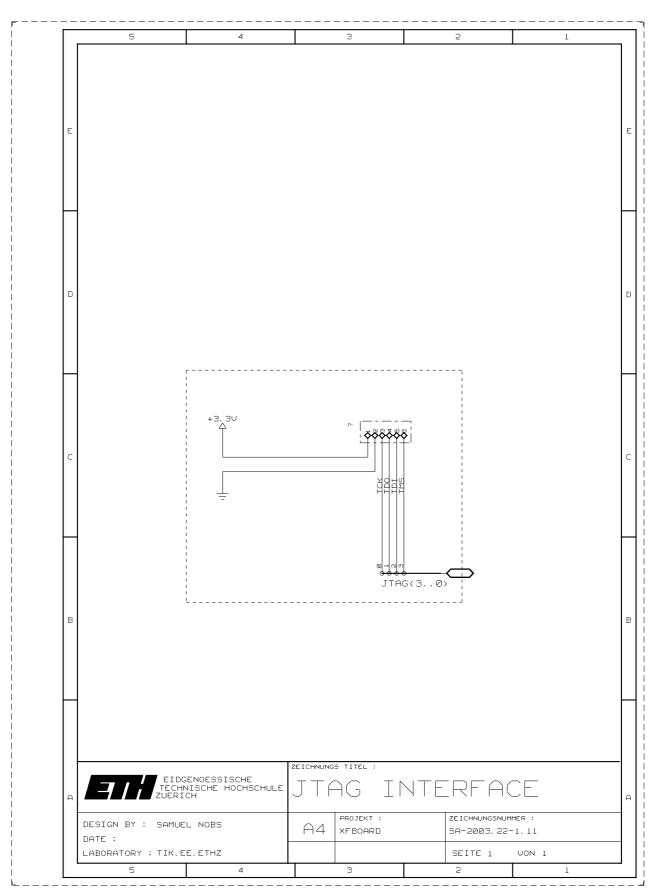

To allow configuration in Boundary Scan mode, a JTAG header is present.

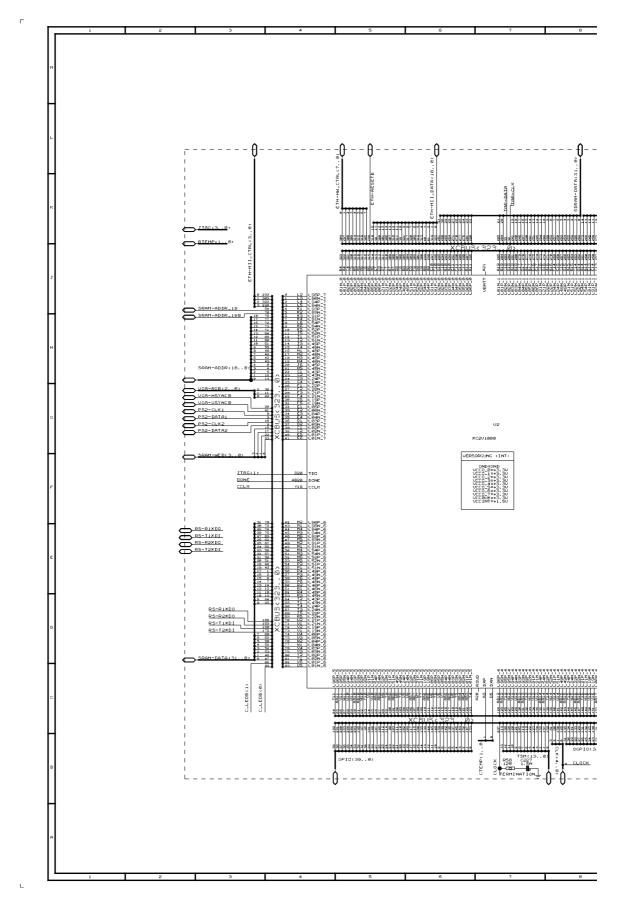

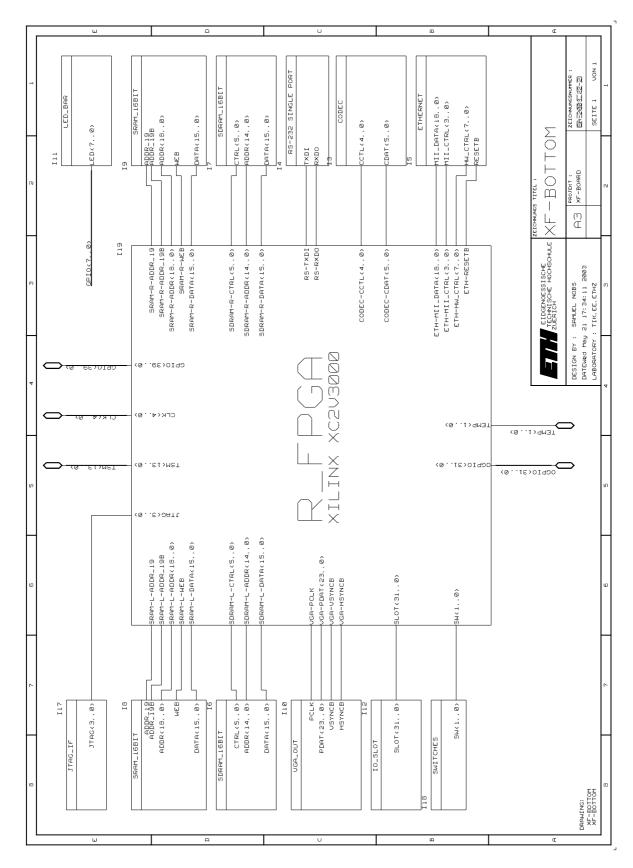

## 3.2 XF Bottom

#### 3.2.1 Reconfigurable FPGA

The FPGA used as the reconfigurable unit is an XC2V3000 of the Virtex-II series by Xilinx [9]. Refer to section 3.1.1 for details about the decoupling capacitor problem; a listing of the number of capacitors used for decoupling is given in table 3-1.

The FPGA is connected to be configured in Slave SelectMap mode (for information about this configuration mode please refer to [10], page 256).

| Capacitance value | $V_{CC_{int}}$ pins | $V_{CC_o}$ pins |

|-------------------|---------------------|-----------------|

| 10.0 μF           | 0                   | 1               |

| $1.0 \mu F$       | 1                   | 3               |

| $0.1  \mu F$      | 3                   | 8               |

| $0.01 \mu F$      | 5                   | 14              |

| 0.001 μF          | 11                  | 28              |

Table 3-6: Number of decoupling capacitances used for the R-FPGA

When connecting peripheral devices to the FPGA, lots of I/O pins must be left unconnected due to the need for reconfiguration. The OS frames in the FPGA remain static, so the I/O pins located in such frames may be used for peripheral devices only. We decided to use only the Inputs and Outputs neighbouring the left and the right OS frame (see figure 1-1). As a result of this restriction there are mere 150 pins available for peripheral devices on each side of the FPGA. An overview of the number of pins used for the various devices connected to the FPGA is given in table 3-7. To retain flexibility, some additional 32 lines to the C-FPGA connecting from the top side of the R-FPGA have been included for the case of non-reconfigurable use.

To allow simple optical signalling and monitoring, active low LEDs are connected to two I/O's. The state of the FPGA's DONE configuration signal is monitored by a LED too. The configuration signals PROG and CCLK are connected to the C-FPGA

| Device              | Pin Count |       |

|---------------------|-----------|-------|

|                     | left      | right |

| SRAM                | 38        | 38    |

| SDRAM               | 37        | 37    |

| VGA Port            | 27        | -     |

| Ethernet            | -         | 32    |

| RS-232 Single Port  | -         | 2     |

| Switches            | -         | 2     |

| Control LEDs        | -         | 2     |

| Audio CoDec         | -         | 11    |

| General Purpose I/O | 16        | 24    |

| I/O Slot            | 32        | -     |

| Pins used           | 150       | 148   |

| Pins available      | 150       | 150   |

| Pins left unused    | 0         | 2     |

Table 3-7: Pin accounting for the R-FPGA

and would not assume a valid signal level as long as the C-FPGA is not configured, so they need to be pulled to  $V_{CC}$ .

To provide temperature control of the two FPGA's, two MAX1617 temperature sensors by Maxim [13] are installed which are connected to the FPGA's temperature-sensing diode pins, DXN and DXP. The temperature values can be read using the SMBus serial protocol described in [13], and the addresses of the two sensors are set to 1A for the C-FPGA and to 4C for the R-FPGA.

The clock signal coming from the quarz oscillator is AC terminated as recommended in [25]. AC termination adds a capacitive load to the driver and a delay due to the RC time constant, however, it consumes low power. The termination elements have to be placed as near as possible to the FPGA's clock input pin in the layout. The clock signals coming from the C-FPGA are not terminated as these signals are buffered and are of high quality.

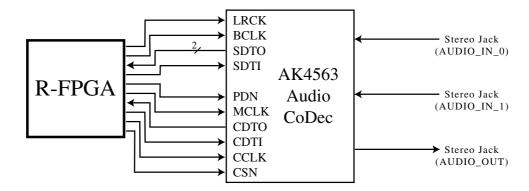

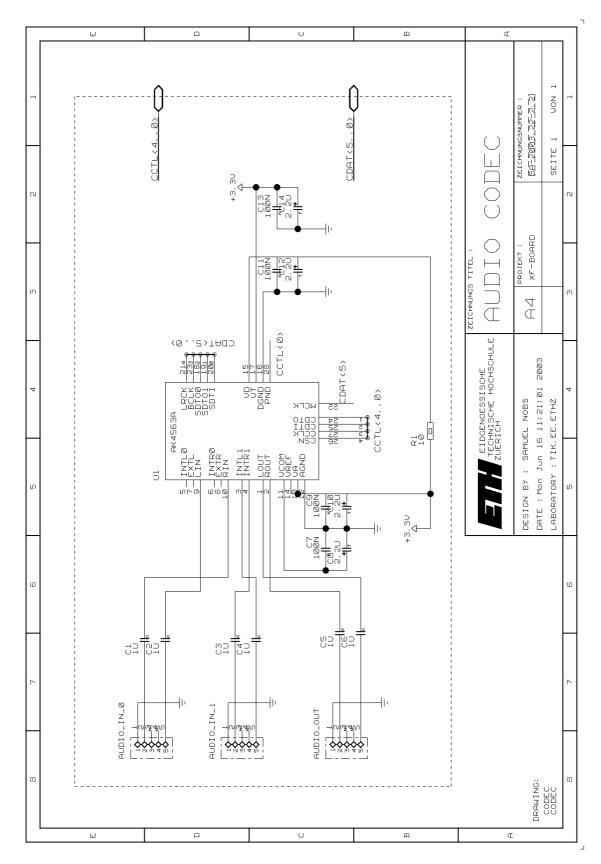

#### 3.2.2 Audio CoDec

The Audio CoDec used in this circuit is the AK4563A by AKM [18]. It is a 16 bit CoDec with two analog stereo inputs and one analog stereo output. The schematic supplied in the datasheet for this device (figure 23 in [18]) has been adopted without modifications. The value for the AC coupling capacitors at the inputs has been calculated to let the cutoff frequency  $f_c$  be at most 16 Hz as this is the lower end of the human ear's frequency response. The formula used was  $f_c = 1/2\pi RC$  with R being the CoDec's input resistance<sup>1</sup> and C being the desired capacitance. This calculation yields a value of 1  $\mu$ F for C. Using the same capacitance for AC decoupling at the output guarantees  $f_c$  to be at most 16 Hz for devices with an input resistance greater than or equal to 1 k $\Omega$ . This means that for headphone appearing as a 32  $\Omega$  load at the output will raise  $f_c$  to a significantly higher value (approximately 500  $\Omega$ ). Hence, the

<sup>&</sup>lt;sup>1</sup>this value depends on the gain table chosen. R is 10 k $\Omega$  at microphone gain table and 125 k $\Omega$  at line gain table, see [18]

#### CHAPTER 3. SCHEMATIC ENTRY

| Pin Number | Function      |

|------------|---------------|

| 1          | Ground        |

| 2          | Left channel  |

| 3          | Not connected |

| 4          | Not connected |

| 5          | Right channel |

Table 3-8: Pin assignment for the audio connector

use of a line amplifier is recommended.

#### 3.2.3 Video DAC, VGA Out

To convert the digital, 24bit wide color data for a pixel into analog values for the red, green and blue components of the video signal, Intersil's video DAC HI1178 is [19] used. Two modifications to the application circuit in figure 11 in [19] have been performed:

- to get the +2 V needed for the VREF pin from the +5 V supply, a voltage divider with fixed values is used instead of a potentiometer.

- some additional bypassing capacitors have been included.

The connector pin assignment can be found in table 3-4 on page 23. The  $\overline{\text{VSYNC}}$  and  $\overline{\text{HSYNC}}$  signals are directly fed through from the FPGA.

#### 3.2.4 1M x 16 SRAM

This circuit's concept is based on the  $1M \ge 16$  SRAM described in section 3.1.3. The only difference is the use of 2 instead of 4 modules that are connected in parallel to get 16 bit words.

#### 3.2.5 16M x 16 SDRAM

The memory modules used, the HYB39S256160CT by Infineon Technologies [21] come in the desired size and width, so the circuit is straightforward.  $\overline{CS}$  is tied to GND and CKE to  $V_{CC}$  to permanently enable the memory module.

#### 3.2.6 8-LED Bar

8 LEDs are included as a means of debugging and displaying. To connect the 8 LEDs to the general purpose I/O's of the FPGA without compromising bus signal integrity, the bus drivers of the 74 series (MM74HC244 by Fairchild Semiconductor [22]) have been used.

#### 3.2.7 I/O Slot

To extend the capabilities of the board, a 36 pin header is installed. 32 pins are signal pins, the remaining 4 pins offer three supply voltages (+5 V, +3.3 V and +1.5 V) and ground.

#### 3.2.8 RS-232 Single Port

This block is mainly the same as the one described in section 3.1.8 on page 22 except for the fact that only one driver pair of the MAX233A is used and one DB9 connector is present.

#### 3.2.9 Ethernet

This block is identical to the one described in section 3.1.2 on page 20.

#### 3.2.10 Switches

This block is identical to the one described in section 3.1.10 on page 24.

#### 3.2.11 JTAG Header

Refer to section 3.1.11 on page 24 for details about this block.

## 3.3 Power Supply

To connect a mains adaptor to the *DXFBOARD*, two different connectors are included: a 20 pin ATX connector used by standard PC power supplies, and a low-voltage connector to connect a +5 V power supply unit. The connectors tip has to be connected to +5 V, the sleeve to GND.

As neither variant shows up with the +1.5 V needed for the FPGA cores, this voltage has to be derived from the +5 V available. For that purpose, a TPS54613 step-down converter from Texas Instruments [23] has been installed. To generate the +3.3 V when no ATX supply is used, a TPS54616 is used. To disable or enable this converter, jumpers are present to be populated or depopulated according to the supply variant chosen. The converter circuits have been copied from the TIKDIMM Board [3].

All voltages are independently fused (+5 V, +3.3 V, +1.5 V); voltages generated by a step-down converter are fused after the converter. As a means for visual control of presence of the supply voltage, every voltage has its own status LED.

To measure the current drawn from the converters two jumpers are installed that may be depopulated to open the circuit to connect the measurement gear. All voltages present on the board are fed to an additional header. This header may be used to feed extension boards or external devices, e.g. a hard drive.

# **Chapter 4**

# **Physical Realization**

This short chapter explains the most important decisions and thoughts correlated with the design and manufacturing steps from the schematic to the physical board.

## 4.1 Trace Width and Spacing

As suggested in [10], the width of the signal traces on the top and the bottom layer of the PCB and the spacings between such traces is set to 5 mil (5 milli-Inches). A slightly lower trace width can be used in internal layers than the width used in top and bottom external or exposed traces. The trace width in inner layers is set to 4 mil. These values yield a  $69\Omega$  impedance for the top and bottom layers and a  $56\Omega$  impedance for the inner layers [29].

## 4.2 Number of Layers

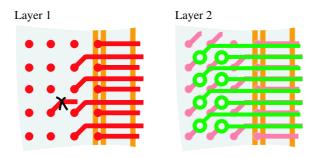

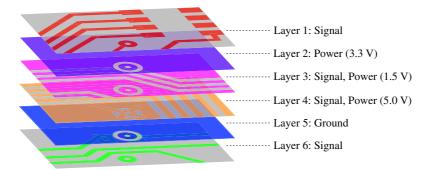

Signal escaping (traces leaving the pin/ball area) can be quite difficult with the large FG packages of the FPGAs (see figures 4-1 and 4-2). Since the selected trace width is 5 mil (4 mil in inner layers), only one signal can be escaped between two pads. As a consequence, only two rows of pins can be escaped per layer as shown in figure 4-3. The XC2V3000 used as the R-FPGA, there are 8 rows of pins to be connected, therefore at least 4 signal layers are necessary. Additionally, there is a need for a ground plane and for one power plane per voltage present on the board. As the two inner signal layers' usage is high only in the perimeter of the FPGAs, they may be filled up with a power plane too. Two power-only planes, one for ground and one for the 3.3 V needed all over the board, and the two inner layers filled up with the two other voltages (1.5 V and 5 V) seem to be reasonable. Have a look at figure 4-4 for details about the PCB layer stackup.

## 4.3 Maximum Trace Length

To be sure not to have reflection problems on the signal traces which are transmission lines for high frequencies, the trace lengths must not exceed an upper limit. The clock frequency does not really matter, as the spectral composition of the signal depends on the edges' slopes and these slopes quickly induce frequency components above the

Figure 4-1: Pinout Diagram of the C-FPGA

XC2V3000 FG676, bottom view

Figure 4-2: Pinout Diagram of the R-FPGA

Figure 4-3: Signal Escaping Problem

Figure 4-4: PCB Layer Stackup

base clock frequency. With the SRAM being the component with the fastest signal transients and assuming a transition time  $t_{tran}$  (rise or fall) of 3 ns<sup>1</sup>, the following rule of thumb yields a maximum trace length of

$$l_{max} < t_{tran} \cdot 3 \, \frac{cm}{ns} \, = \, 9 \, cm$$

which can easily be guaranteed not to be exceeded. So signal termination is omitted except for the clock signals coming from the quarz oscillator (see sections 3.1.1 and 3.2.1).

$<sup>^1</sup>$ Unfortunately, the datasheet [20] does not provide an exact value, but 3 ns being 20% of the access time (15 ns) seem to be a reasonable value

# Chapter 5

# **Programming Model**

This chapter shall give you the information needed for successful programming of the *XFBOARD*. First, you get an overview of the components available for use, then you learn the concept of programming the board.

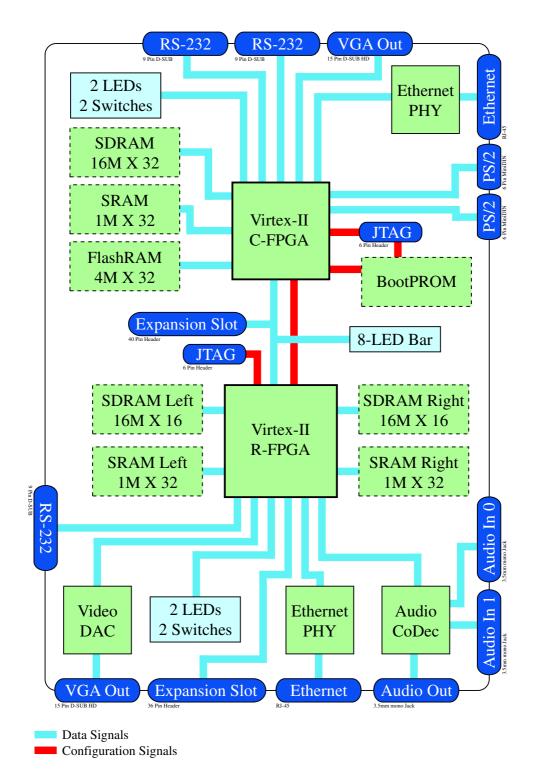

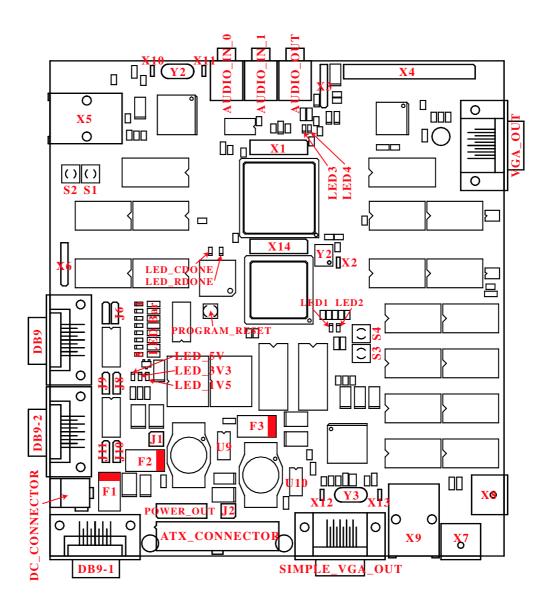

## 5.1 Available Components

To get an idea of the components available on the board you may want to catch a glimpse of figure 5-1 which provides a block diagram of the *XFBOARD*. Figure 5-2 offers a component side view of the PCB including the reference designators for the most important components; this may help you to locate them on the board. In the following subsections, some more information is given in textual and graphical form for the functional blocks in this diagram. However, details with low importance have been omitted in the graphics; for a more thorough discussion see the corresponding section in chapter 3 and the schematics in appendix A. Also, it may be useful to consult the relevant datasheets. Listings with all pin connections between the FPGAs and external components are available in appendix B. These pin listings may be used to generate the \*.ucf constraints file; on the CD-ROM, there are two ready-to-use constraints files: C-FPGA.ucf and R-FPGA.ucf.

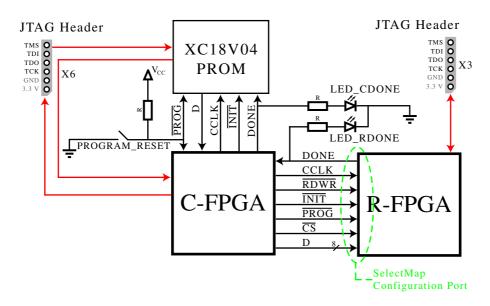

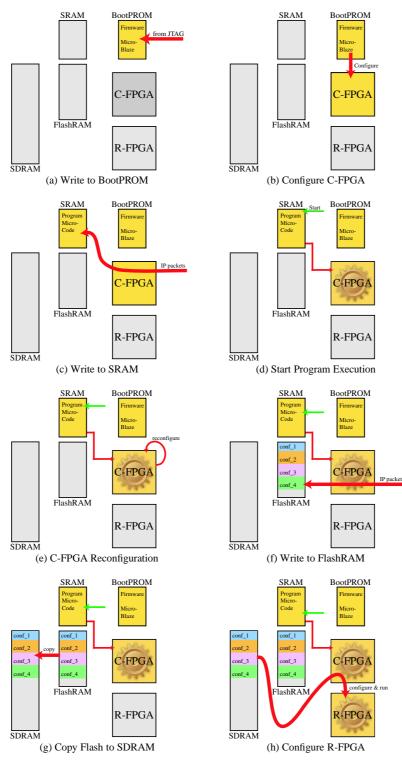

#### 5.1.1 Configuration Section

As shown in figure 5-3 there are three elements to be configured from the outside world, the BootPROM for the C-FPGA, the C-FPGA itself and the R-FPGA. The BootPROM and the C-FPGA are connected to the same JTAG chain while the R-FPGA has its own JTAG connector. Please note that configuration of the two FPGAs via JTAG is not to be performed when using the board for those purposes it is intended for. As stated in the description of the development cycle in section 5.2, only the BootPROM is configured via JTAG. The option to configure the FPGAs via JTAG chain is present for higher flexibility. Also, the JTAG interface may be used for debugging via boundary scan.

For partial reconfiguration of the R-FPGA, its SelectMAP configuration port may be used. Refer to table B-11 on how to connect to the R-FPGA from the C-FPGA.

The two LEDs LED\_CDONE and LED\_RDONE are dark after power-up and get lit as soon as the C-FPGA or the R-FPGA is configured, respectively. You can reset the C-FPGA and trigger its reconfiguration using the PROGRAM\_RESET switch.

Figure 5-1: Block Diagram of the XF-Board (Power Supply omitted)

Figure 5-2: Component Side View of the XF-Board with Reference Designators

The R-FPGA may be reset via the SelectMAP port. Consulting [10], [14] and [9] is recommended for additional information on (re)configuration.

Figure 5-3: Configuration Section

#### 5.1.2 FlashRAM

Figure 5-4: FlashRAM for the C-FPGA

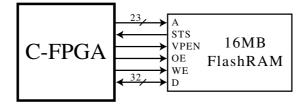

Two Intel 28F640J3 with 16 MB of storage (4M x 32) are connected to the C-FPGA as shown in figure 5-4. In the graphic, the two FlashRAM modules are merged into one block as they are connected in parallel to provide 32 bit words. After power-up, the FPGA can read and/or write the FlashRAM. Refer to the datasheet [24] for details on reading from and writing to the flash array. The schematic is described in section 3.1.5. The pins of the C-FPGA connected to the FlashRAM are listed in table B-5.

#### 5.1.3 SRAM

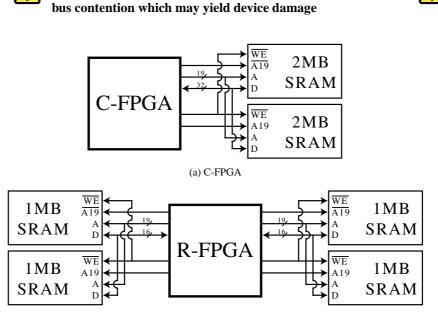

The FPGAs have access to 4 MB of SRAM built from eight Alliance AS7C34096. The SRAM for the C-FPGA is organized as  $1M \ge 32$  bits as shown in figure 5-5(a),

while the SRAM for the R-FPGA is organized in two independent banks as 1M x 16 (figure 5-5(b)). Please refer to sections 3.1.3 and 3.2.4 for the schematic, to tables B-13, B-23 and B-26 for the pins connected to the SRAM banks, and to the datasheet [20] on how to read and write from the SRAM.

Please note that A19 and  $\overline{A19}$  are in fact chip select signals that are used to extend the address space over a second group of memory modules.

A19 and A19 have to be complementary at every time to avoid 🥂

(b) R-FPGA

Figure 5-5: SRAM for both FPGAs

## 5.1.4 S-DRAM

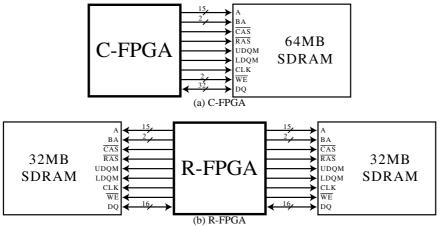

Both FPGAs have access to 64 MB of SDRAM. The C-FPGA is connected to two Infineon HYB39S256160CT to get a 16M x 32 bit structure. In figure 5-6(a), these two modules are merged into one block. The R-FPGAs SDRAM is organized in two independent banks each of which consists of an Infineon HYB39S256160CT, providing 16M x 16 bits (figure 5-6(b)). Sections 3.1.4 and 3.2.5 offer some additional information about the schematics. The FPGA pins connected to the SDRAM banks are listed in the tables B-10, B-22 and B-25, while details about the communication protocol may be gathered in [21].

## 5.1.5 Ethernet PHY

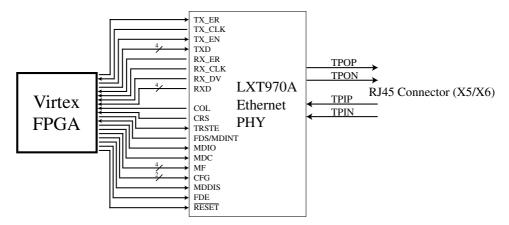

The **JXFBOARD** interfaces to an Ethernet LAN at 10 or 100Mbps. Each FPGA is connected to an Intel LXT970A Ethernet PHY chip as can be seen in figure 5-7. The FPGA acts as a MAC and manages the transfer of data packets to and from the PHY

Figure 5-6: SDRAM for both FPGAs

chip. The FPGA also controls the configuration pins determining the operational mode of the PHY chip. How the Ethernet PHY chips are connected to the FPGAs is visible in the tables B-4 and B-19. Schematic details are described in section 3.1.2.

Figure 5-7: Ethernet Interfaces for both FPGAs

To send data to the LAN, the FPGA needs to enable the transmitter using TX\_EN and then send the data bits on TXD. These operations have to be synchronized with the signal TX\_CLK. If a transmission error ocurred, the MAC (i.e. the FPGA) needs to inform the PHY by asserting TX\_ER. As soon as valid data has been received by the PHY, the FPGA gets notified using RX\_DV, and this data is fed to the FPGA via RXD in sync with the receiver clock RX\_CLK. The PHY asserts RX\_ER when it receives invalid symbols from the network.

The FPGA can disable the interface to the PHY by asserting the tristate control TRSTE. Otherwise, the FPGA passes management information to and from the PHY over the serial data line MDIO in sync with the clock MDC. The FPGA can be alerted to changes in PHY chip status by the FDS/MDINT interrupt line.

#### 5.1. AVAILABLE COMPONENTS

The FPGA can configure the PHY using the MF and the CFG lines. The 5 bits on MF can set operation functions like auto-negotiation, repeater mode, scrambler mode etc. The 2 CFG bits are used to chose 10Mbps or 100Mbps operating speed and to enable/disable the link test function. FDE determines either full-duplex or half-duplex operation, and MDDIS disables the management information interface.

The meaning of the LEDs at the front side of the RJ45 connectors is as follows:

| yellow | link active        |

|--------|--------------------|

| green  | receiver active    |

| orange | transmitter active |

You may want to learn how to communicate with the PHY chip in more detail using the datasheet [16].

## 5.1.6 Audio CoDec

The **JXFBOARD** uses an AK4563A to provide two stereo inputs and one stereo output. For details about the connections between the FPGA and the CoDec, please refer to figure 5-8 and to table B-16. You may want to visit section 5.1.6 for an explanation of the schematic.

Figure 5-8: Audio In- and Output

The audio signals coming from the jack connectors are digitized and fed to the FPGA using the I<sup>2</sup>S protocol: serial audio data is offered on SDTO<0> and SDTO<1> in sync to the bit clock  $\overline{\text{BCLK}}$ . Left-right information is given by the clock LRCK; both clocks are generated by the FPGA. Data to be converted to the analog domain and output via the jack connector has to be present on the SDTI line, again in sync to the two abovementioned clocks. The master clock MCLK from the FPGA synchronizes all the internal operations of the codec.

Additional information on operation status and operation functions (e.g. the peakmeter) can be read to and written from the control register using the signals CSN, CCLK, CDTI and CDTO. To reset the CoDec, pull down the PDN.

The datasheet [18] offers some additional information on the CoDec.

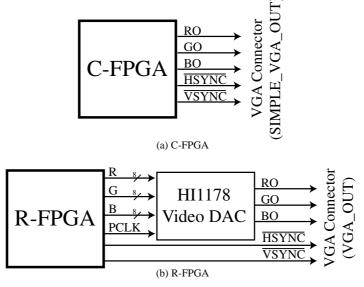

## 5.1.7 VGA Outputs

Both FPGAs can generate video signals for display on a VGA monitor. The C-FPGA directly feeds the color information to the VGA connector (figure 5-9(a)) using the one-bit signals RO, GO and BO, yielding 3 bit color resolution (8 colors). The vertical and horizontal sync pulses  $\overrightarrow{VSYNC}$  and  $\overrightarrow{HSYNC}$  have to be generated by the FPGA. Schematic details about this simple VGA output can be found in section 3.1.7, for a listing of the C-FPGA's pins connected to the VGA output refer to table B-12.

Figure 5-9: VGA Outputs for both FPGAs

The R-FPGA generates the signals using the Intersil HI1178 video DAC [19]. The DAC accepts three 8 bit data signals, R, G and B, as a color information, synchronized to the pixel clock PCLK generated by the FPGA. The analog color information is then fed to the VGA output using RO, GO and BO. Again, the sync pulses have to be generated by the R-FPGA. The schematic of this circuit is described in section 3.2.3. The corresponding pin listing is available in table B-29.

## 5.1.8 PS/2 Ports

The C-FPGA has access to two PS/2 ports to connect a keyboard and a mouse. The FPGA receives two signals from each interface: a clock signal and a serial data stream that is synchronized with the falling edges on the clock signal. Figure 5-10 illustrates the connection between the R-FPGA and the PS/2 ports. The pin listing is located in table B-8. A good resource for in-depth PS/2 information is [30].