Sommer Semester 2004

Prof. Dr. L. Thiele

Semester Project

# Embedded Task Machine with BTnode and FPGA

Clemens Lombriser and Marc André

Advisor: Matthias Dyer

### Abstract

The aim of this semester project was to create an *Embedded Task Machine*. The system would provide a means of executing applications that are too large to fit on the available hardware. Such applications would be broken down into smaller tasks and a description of how they relate to each other. *Synchronous Data Flow* is used as the modelling language for the applications. The *Embedded Task Machine* then executes the tasks one after another on reconfigurable hardware. The system at hand consists of a task repository, a memory management module for the interexchanged data, an execution unit, and a scheduler.

This report describes the architecture and the the detailed design of the complete project.

## Acknowledgment

We would like to thank Prof. Lothar Thiele for making it possible for us to work on this interesting project. We also would like to thank our tutor, Matthias Dyer, who supported us on any problems we had and Jan Beutel who helped out when Matthias was not present.

We would not have come this far if Roman Plessl would not have taken time for us in the last few weeks of his Master's Thesis. The discussions we had with him about the concepts of his work were very helpful and helped us a lot to start off our project.

Last but not least we also would like to thank the rest of the TIK-team for the various small things they did to support us.

Clemens Lombriser

Marc André

# Problem Task (German)

### Einleitung

### Der BTnode und das FPGA Modul

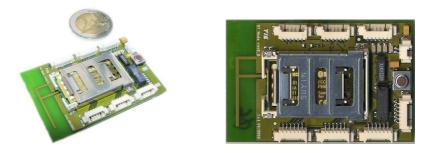

An unserem Institut wurden in Forschungsarbeiten, sowie in früheren Semesterund Diplomarbeiten diverse Hardware entwickelt, welche im Zusammenhang mit eingebetteten Systemen und mobilem Computing stehen.

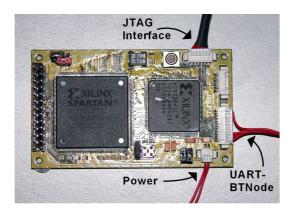

Zum einen gibt es den BTnode [1], ein kleiner "wireless node", mit einem Mikrocontroller und einem Bluetooth Modul. Der BTnode wird in verschiedenen Forschungsprojekten eingesetzt (z.B. Wireless Sensor Networks [2] oder Wearable Computing [3]).

Zum anderen wurde in einer Diplomarbeit ein FPGA Modul entwickelt, welches für den batteriebetriebenen Einsatz gedacht ist. Das Modul, bestehend aus einem Xilinx SpartanII FPGA, einem CPLD, SRAM und Flash ist so konstruiert, dass es mit dem BTnode über eine serielle Schnittstelle kommunizieren kann. Der Verbund von BTnode und FPGA erlaubt nun eine äusserst flexible Nutzung.

Abbildung 1: BTnode Rev 2.2 and FPGA Module

Es ist zum Beispiel möglich, dass mehrere FPGA Konfigurationen auf dem FPGA Modul gespeichert sind, welche dann auf Befehl des Mikrocon-

trollers auf dem BTnode in das FPGA geladen werden. So kann auch ein einfacher Scheduling Algorithmus auf dem BTnode implementiert werden, welcher den Ablauf einer Applikation bestehend aus mehreren Konfigurationen (Tasks) steuert. Eine Erweiterung dieses Scenarios ist, dass die Tasks nicht von Anfang an schon zur Verfügung stehen, sondern zuerst noch über die drahtlose Verbindung (Bluetooth) heruntergeladen werden müssen.

Eine Anwendung eines solchen Scenarios sind Sensor Netzwerke. Sensor Netzwerke bestehen aus einer Vielzahl von kommunizierenden Sensorknoten. Der BTnode und das FPGA Modul können zusammen einen solchen Sensorknoten darstellen. Der FPGA, welcher besonders effizient ist für die digitale Signalverarbeitung, sammelt Sensordaten und bereitet sie auf (Vorverarbeitung, Komprimierung, usw.). Der BTnode sendet dann auf Wunsch diese Daten zu einem Host.

### **Embedded Machine**

Die Embedded Machine kommt ins Spiel, wenn eine Applikation als Ganzes zu gross für den FPGA ist. Die Applikation kann trotzdem ausgeführt werden, in dem man sie in kleinere Tasks aufteilt und definiert, wie die Task miteinander kommunizieren und interagieren. Diese Definition nennen wir *Koordinationssprache*. Eine Applikation besteht in diesem Fall aus zwei Teilen: aus der Koordinationsbeschreibung und aus den Tasks.

Wird die Koordinationssprache nicht kompiliert sondern interpretiert, geht die Information, wie die Tasks miteinander agieren, nicht verloren und kann zur Lade- und Laufzeit verwendet werden.

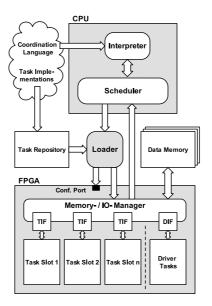

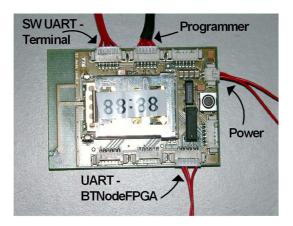

In [4] wurde das Prinzip der Embedded Machine für die Ausführung von Prozess Netzwerken auf eingebetteter rekonfiguierbarer Logik erklärt (siehe auch Abb. 2). Ein Prozess Netzwerk, besteht aus mehreren Prozessen (Tasks), welche in einem oder mehreren Slots im FPGA laufen können. Ein Scheduler, der in einer CPU läuft, entscheidet zur Laufzeit, welche Tasks als nächstes ausgeführt werden.

Die Realisierung der Embedded Machine auf dem FPGA Modul ist Hauptteil der Masterarbeit MA-2004-03 [5]. Das Ziel dort war es den Memorymanager und die Grundlagen für die Rekonfiguration der Taskslots zu implementieren. In dieser Arbeit wird jedoch ein IPAQ PDA als CPU verwendet.

Abbildung 2: Embedded Machine Runtime System

### Aufgabenstellung

Das Ziel dieser Arbeit ist den BTnode und das FPGA Modul zusammenzuschliessen und die entsprechende Services und Protokolle für die folgende Funktionen zu implementieren:

- Speichern einer FPGA-Konfiguration vom BTnode ins Flash vom FPGA Modul.

- (Partielle) Rekonfiguration des FPGAs aus dem Flash.

- Command/Event Kommunikation zwischen BTnode und FPGA.

Eine mögliche Verbindung zwischen BTnode und FPGA Modul ist die serielle Schnittstelle. Um die verschiedenen Dienste über eine serielle Verbindung zu multiplexen, braucht es ein durchdachtes Protokoll.

Es werden zur Zeit eine neue Version von BTnodes entwickelt. Diese haben zwar ein neues leistungsfähigeres Bluetooth Interface basieren aber auf demselben AVR Mikrokontroller wie die bisherigen BTnodes. Da die neuen BTnodes erst diesen Sommer erscheinen, soll diese Arbeit noch die bisherigen BTnodes verwenden.

Um Bluetooth mit den bisherigen BTnodes zu nutzen, wurde ein eigenes Dispatcher-basiertes Betriebssystem verwendet. Für die neuen BTnodes wird das multitasking Betriebssystem Ethernut [6] verwendet. Dieses RTOS läuft auch tadellos auf den bisherigen BTnodes, es fehlt zur Zeit nur noch die Unterstützung der Bluetooth Funktionen.

### Teilaufgaben

- Erstellen Sie in den ersten zwei Wochen zusammen mit Ihrem Betreuer einen realistischen Zeitplan, welcher Meilensteine festlegt. überlegen Sie sich, wie Sie die Arbeit effizient aufteilen können.

- 2. Machen Sie sich mit den beiden Hardwareplattformen (BTnode und FPGA Modul) vertraut.

- 3. Arbeiten Sie sich in die Grundlagen der AVR Mikrokontroller bzw. FPGA/CPLD Programmierung ein.

- 4. Definieren Sie ein Protokoll für die Kommunikation zwischen BTnode und FPGA Modul und erstellen Sie ein Konzept, wie dieses im BTnode bzw. im CPLD/FPGA verarbeitet wird.

- 5. Implementieren Sie das Protokoll im BTnode und im FPGA Modul.

- Definieren und Implementieren Sie ein oder mehrere Beispielsscenarien, mit welchen Sie das Funktionieren der Kommunikation demonstrieren können.

- 7. Dokumentieren Sie Ihre Arbeit sorgfältig mit einem Vortrag, einer kleinen Demonstration, sowie mit einem Schlussbericht.

### Durchführung der Semesterarbeit

### Allgemeines

- Der Verlauf des Projektes Semesterarbeit soll laufend anhand des Projektplanes und der Meilensteine evaluiert werden. Unvorhergesehene Probleme beim eingeschlagenen Lösungsweg können Änderungen am Projektplan erforderlich machen. Diese sollen dokumentiert werden.

- Stellen Sie Ihr Projekt zu Beginn der Semesterarbeit in einem Kurzvortrag vor und präsentieren Sie die erarbeiteten Resultate am Schluss im Rahmen des Institutskolloquiums Ende Semester.

• Besprechen Sie Ihr Vorgehen regelmässig mit Ihren Betreuern. Verfassen Sie dazu auch einen kurzen wöchentlichen Statusbericht (EMail).

### Abgabe

• Geben Sie zwei unterschriebene Exemplare des Berichtes spätestens am 2. Juli 2004 dem betreuenden Assistenten oder seinen Stellvertreter ab. Diese Aufgabenstellung soll vorne im Bericht eingefügt werden.

# Contents

| 1        | Intr           | roduction                                 | 1        |  |  |  |

|----------|----------------|-------------------------------------------|----------|--|--|--|

|          | 1.1            | Notation                                  | 3        |  |  |  |

| <b>2</b> | $\mathbf{Sys}$ | tem Architecture                          | <b>5</b> |  |  |  |

|          | 2.1            | The Execution Model                       | 5        |  |  |  |

|          |                | 2.1.1 Modules of the Execution Model      | 5        |  |  |  |

|          |                | 2.1.2 Mapping the modules to the hardware | 6        |  |  |  |

|          | 2.2            | MC-Protocol                               | 7        |  |  |  |

|          |                | 2.2.1 Commands to the CPLD component      | 7        |  |  |  |

|          |                | 2.2.2 Commands to the FPGA                | 8        |  |  |  |

|          |                | 2.2.3 Response from FPGA module           | 10       |  |  |  |

|          | 2.3            | FPGA-Protocol                             | 11       |  |  |  |

|          |                | 2.3.1 Data flow                           | 11       |  |  |  |

|          | 2.4            | FIFO structure in the SRAM                | 12       |  |  |  |

|          | 2.5            | Task slots in Flash                       | 14       |  |  |  |

| 3        | CP             | PLD-Design                                |          |  |  |  |

|          | 3.1            | CPLDTop                                   | 15       |  |  |  |

|          | 3.2            | CPLDControl                               | 16       |  |  |  |

|          | 3.3            |                                           | 16       |  |  |  |

|          |                |                                           | 16       |  |  |  |

|          |                | -                                         | 18       |  |  |  |

|          | 3.4            |                                           | 19       |  |  |  |

|          |                |                                           | 19       |  |  |  |

|          |                | -                                         | 19       |  |  |  |

|          |                |                                           | 22       |  |  |  |

|          | 3.5            |                                           | 22       |  |  |  |

|          | 0.0            | _                                         | 22       |  |  |  |

|          |      | 3.5.2 Usage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 22 |

|----------|------|----------------------------------------------------------------------------------------------|----|

|          | 3.6  | FPGAComm                                                                                     | 24 |

|          |      | 3.6.1 Description $\ldots$                                                                   | 24 |

|          |      | 3.6.2 Usage                                                                                  | 24 |

| 4        | FPO  | GA-Design                                                                                    | 26 |

|          | 4.1  | FPGATop                                                                                      | 26 |

|          | 4.2  | FPGAControl                                                                                  | 27 |

|          |      | 4.2.1 Description                                                                            | 27 |

|          | 4.3  | CPLDComm                                                                                     | 28 |

|          |      | 4.3.1 Description                                                                            | 28 |

|          |      | 4.3.2 Usage                                                                                  | 29 |

|          | 4.4  | OutputControl                                                                                | 31 |

|          | 4.5  | SRAMCore                                                                                     | 31 |

|          |      | 4.5.1 Description $\ldots$                                                                   | 31 |

|          |      | 4.5.2 Usage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 31 |

|          | 4.6  | MemoryControl                                                                                | 33 |

|          |      | 4.6.1 Description $\ldots$                                                                   | 33 |

|          |      | 4.6.2 Usage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 34 |

|          | 4.7  | FIFOControl                                                                                  | 34 |

|          |      | 4.7.1 Description $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 34 |

|          |      | 4.7.2 Usage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 36 |

|          | 4.8  | TaskControl                                                                                  | 37 |

|          |      | 4.8.1 Description                                                                            | 37 |

|          | 4.9  | Task                                                                                         | 38 |

|          |      | $4.9.1  \text{Description}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 38 |

|          |      | 4.9.2 The TaskWrapper                                                                        | 40 |

|          |      | 4.9.3 TaskTestbench                                                                          | 41 |

|          |      | 4.9.4 Requirements for a task                                                                | 41 |

|          | 4.10 | Drivers                                                                                      | 41 |

|          |      | 4.10.1 Input Driver                                                                          | 42 |

|          |      | 4.10.2 Output Driver                                                                         | 42 |

|          |      | 4.10.3 DriverWrapper                                                                         | 42 |

| <b>5</b> | MC   | Software                                                                                     | 44 |

|          | 5.1  | Introduction                                                                                 | 44 |

|          | 5.2  |                                                                                              | 44 |

|          |      |                                                                                              |    |

|              |                                                                    | 5.2.1 SDF formalism                                        | 46                                                                                                                                                         |

|--------------|--------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                    | 5.2.2 Scheduling                                           | 46                                                                                                                                                         |

|              | 5.3                                                                | Ethernut                                                   | 49                                                                                                                                                         |

|              | 5.4                                                                | User Interface                                             | 49                                                                                                                                                         |

|              | 5.5                                                                | Messages                                                   | 52                                                                                                                                                         |

|              | 5.6                                                                | Scheduler                                                  | 53                                                                                                                                                         |

|              |                                                                    | 5.6.1 Data structures                                      | 53                                                                                                                                                         |

|              |                                                                    | 5.6.2 Communication with the BT<br>nodeFPGA board $\hdots$ | 55                                                                                                                                                         |

|              | 5.7                                                                | Loading tasks                                              | 55                                                                                                                                                         |

| 6            | Eva                                                                | luation                                                    | 57                                                                                                                                                         |

|              | 6.1                                                                | Time Measurements                                          | 57                                                                                                                                                         |

|              | 6.2                                                                | Power Measurements                                         | 58                                                                                                                                                         |

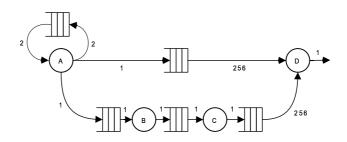

|              | 6.3                                                                | Demo application                                           | 58                                                                                                                                                         |

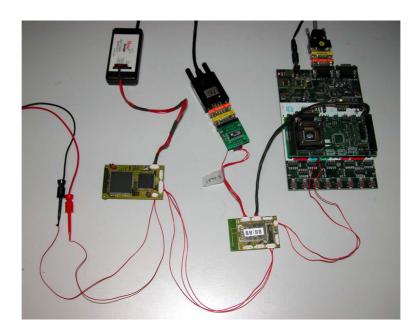

|              |                                                                    | 6.3.1 Setup                                                | 59                                                                                                                                                         |

|              |                                                                    | 6.3.2 Running the Demo                                     | 60                                                                                                                                                         |

| -            | a                                                                  |                                                            | <i>.</i>                                                                                                                                                   |

| 7            | Sun                                                                | nmary                                                      | <b>62</b>                                                                                                                                                  |

|              |                                                                    | ·                                                          |                                                                                                                                                            |

| $\mathbf{A}$ | Hov                                                                | v to start the Embedded Task Machine                       | 63                                                                                                                                                         |

| A            |                                                                    | v to start the Embedded Task Machine                       | <b>63</b>                                                                                                                                                  |

| Α            |                                                                    |                                                            |                                                                                                                                                            |

| A            |                                                                    | Cabling                                                    | 63                                                                                                                                                         |

| Α            |                                                                    | Cabling                                                    | 63<br>63                                                                                                                                                   |

| Α            | A.1                                                                | Cabling                                                    | 63<br>63<br>63                                                                                                                                             |

| в            | A.1<br>A.2<br>A.3                                                  | Cabling                                                    | 63<br>63<br>63<br>66                                                                                                                                       |

|              | A.1<br>A.2<br>A.3                                                  | Cabling                                                    | 63<br>63<br>63<br>66<br>66                                                                                                                                 |

|              | A.1<br>A.2<br>A.3<br>Fut                                           | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> </ul>                                                             |

|              | A.1<br>A.2<br>A.3<br>Fut<br>B.1                                    | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> </ul>                                                             |

|              | A.1<br>A.2<br>A.3<br><b>Fut</b><br>B.1<br>B.2                      | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> </ul>                                                 |

|              | A.1<br>A.2<br>A.3<br><b>Fut</b><br>B.1<br>B.2<br>B.3               | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>68</li> </ul>                                     |

|              | A.1<br>A.2<br>A.3<br><b>Fut</b><br>B.1<br>B.2<br>B.3<br>B.4        | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>68</li> <li>69</li> </ul>             |

|              | A.1<br>A.2<br>A.3<br><b>Fut</b><br>B.1<br>B.2<br>B.3<br>B.4<br>B.5 | Cabling                                                    | <ul> <li>63</li> <li>63</li> <li>63</li> <li>63</li> <li>66</li> <li>66</li> <li>67</li> <li>67</li> <li>68</li> <li>68</li> <li>69</li> <li>69</li> </ul> |

# List of Figures

| 1   | BTnode Rev 2.2 and FPGA Module                                           |

|-----|--------------------------------------------------------------------------|

| 2   | Embedded Machine Runtime System                                          |

| 1.1 | Mealy automaton                                                          |

| 1.2 | Overview diagram of a state machine                                      |

| 2.1 | Overview of the <i>Embedded Task Machine</i>                             |

| 2.2 | Wires between CPLD and FPGA                                              |

| 2.3 | Timing details of a single write cycle from CPLD to FPGA $\therefore$ 12 |

| 2.4 | SRAM FIFO structure                                                      |

| 2.5 | Organization of the task slots in the Flash                              |

| 3.1 | CPLD Architecture                                                        |

| 3.2 | FSM of the CPLDControl entity                                            |

| 3.3 | Timing diagram of the Flash access                                       |

| 3.4 | FlashCore FSM 21                                                         |

| 3.5 | Overview of the Finite State Machine of the FlashCore 22                 |

| 3.6 | FPGAConfigurator FSM                                                     |

| 3.7 | FPGAConfigurator FSM Interface                                           |

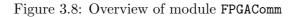

| 3.8 | Overview of module FPGAComm                                              |

| 3.9 | <b>FPGAComm</b> FSM                                                      |

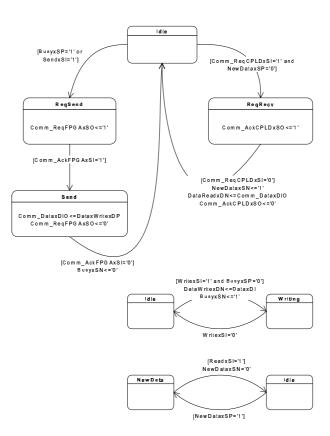

| 4.1 | FPGA Architecture                                                        |

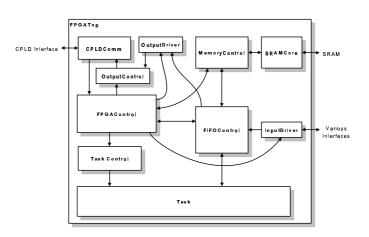

| 4.2 | Symbolic state chart of FPGAControl                                      |

| 4.3 | Overview of the module CPLDComm 29                                       |

| 4.4 | CPLDComm FSM                                                             |

| 4.5 | Interface of the SRAMCore entity                                         |

| 4.6 | SRAMCore handshake                                                       |

| 4.7 | Structure of the MemoryControl entity                                    |

| 4.8               | FIFOControl interface                                                                                                                                      | 35             |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

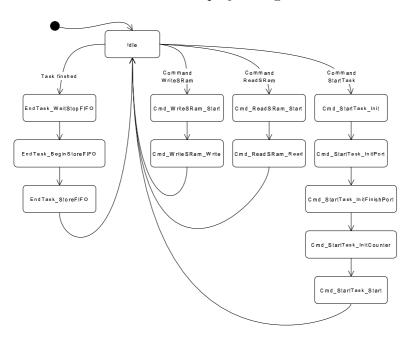

| 4.9               | TaskControl state chart                                                                                                                                    | 38             |

|                   |                                                                                                                                                            |                |

| 5.1               | SDF graph                                                                                                                                                  | 45             |

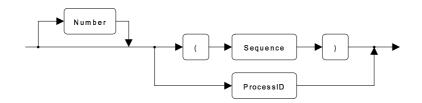

| 5.2               | Schedule sequence parser diagram                                                                                                                           | 54             |

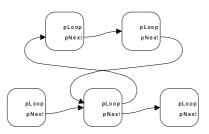

| 5.3               | possible linkage of the EXECUTION_STEP structures                                                                                                          | 55             |

|                   |                                                                                                                                                            |                |

| 6.1               | SDF graph of the demo application                                                                                                                          | 59             |

|                   |                                                                                                                                                            |                |

|                   |                                                                                                                                                            |                |

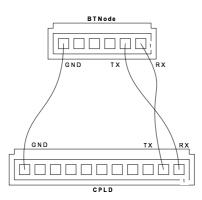

| A.1               | BTnodeFPGA BTnode connection schematic                                                                                                                     | 64             |

|                   | BTnodeFPGA BTnode connection schematic                                                                                                                     |                |

| A.2               |                                                                                                                                                            | 64             |

| A.2<br>A.3        | The connections used at the BTnodeFPGA-board $\ . \ . \ .$ .                                                                                               | 64<br>64       |

| A.2<br>A.3<br>A.4 | The connections used at the BTnodeFPGA-board The connections used at the BTnode-board, rev2.2                                                              | 64<br>64<br>65 |

| A.2<br>A.3<br>A.4 | The connections used at the BTnodeFPGA-board The connections used at the BTnode-board, rev2.2 Interconnections when using the <i>Embedded Task Machine</i> | 64<br>64<br>65 |

# List of Tables

| 2.1 | Resources on the hardware modules                                  | 6  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | CPLD commands                                                      | 8  |

| 2.3 | List of response messages codes                                    | 11 |

| 3.1 | FlashCore operation codes                                          | 20 |

| 4.1 | SRAMCore handshake timings                                         | 32 |

| 5.1 | Commands accepted by the RS232 software $\ldots$                   | 50 |

| 5.2 | Commands accepted by the BT<br>node user interface $\ . \ . \ .$ . | 56 |

| 6.1 | time requirements of significant processes                         | 57 |

| 6.2 | power requirements of significant processes                        | 58 |

| A.1 | BTnode UART settings                                               | 66 |

| A.2 | BTnodeFPGA UART settings                                           | 66 |

### Chapter 1

## Introduction

The next generation computing environment is called *ubiquitous computing*. It will substantially change the way people interact with computers, because any person will continuously be interacting with hundreds of nearby computers, which are interconnected and not visible to the user. Computers will be assisting people requiring no or just minimal interaction over new kinds interfaces that are subject of current research.

In order to invisibly integrate computers or at least not impeding into the environment, devices have to be small. This requirement forces a designer of a system to reduce the number of components to a minimum, and to use every module optimally not only in terms of area, but also over time. Reconfigurable hardware allows to reduce the size of the hardware by executing only the parts that are actually needed at every point in time. Other hardware configurations can be temporally stored using much less area on a mass storage device.

The aim of this thesis is to develop the software for a prototype system which can accept applications over a wireless connection and execute them. If the applications require more hardware over time than the system can provide permanently, the applications will be split into a number of tasks which then will be executed sequentially on the reconfigurable hardware part.

The execution model for the applications for the *Embedded Task Machine* defines an application to be a set of tasks which do some kind of operation on

data, and a description of how this data is passed from one task to another. This description is given in some *coordination language*.

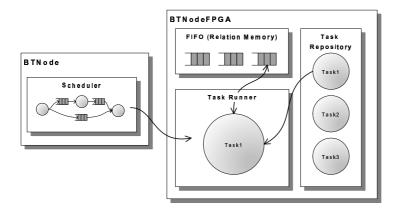

The *Execution Model* of the system specifies four main entities: The *task repository*, which holds the different tasks of the application, the *relation memory*, where the data communicated between the tasks is stored, the *task runner*, where the tasks are actually executed, and finally the *scheduler* which controls the sequence in which the tasks are executed.

The report at hand describes how the system has been implemented. It is organized in the following chapters:

#### 1. System Architecture

This chapter explains how the system is build up. It explains what the most important parts are and where they are placed on the hardware. Additionally it explains the protocols used on the external interfaces of the hardware modules.

### 2. CPLD-Design

The CPLD is one of the two programmable modules on the BTnodeFPGA board. This chapter explains the entities placed on the CPLD and how they collaborate.

### 3. FPGA-Design

The FPGA is the reconfigurable module and thus the heart of the system. This is the hardware on which the tasks of the application run. The chapter also explains the additional entities that are implemented on the FPGA to support the tasks.

### 4. Microcontroller Software

The microcontroller is the "mind" of the whole system. It is used to schedule all the tasks and initializes the hardware for the applications. It also provides a user interface which can be used to describe the application using a language which builds a *Synchronous Data Flow* graph.

#### 5. Evaluation

Some measurements on timings and power consumption have been carried out on the implemented and running system. The results are presented in this chapter. Additionally, a demo application has been implemented. The chapter explains what calculations are performed by the application and how it can be run on the system.

### 6. Summary

This chapter concludes the report and summarizes the achievements of the project.

### 7. How to Start the Embedded Task Machine

When using the system, the hardware has to be correctly interconnected. This chapter shows how it has to be done.

### 8. Future Work

Some ideas to what can further be done with the system is described in this chapter.

### 1.1 Notation

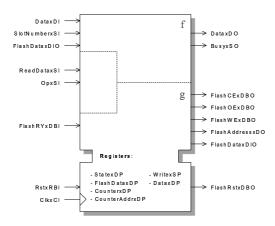

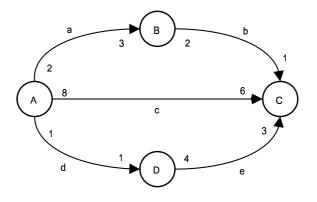

All modules in the FPGA and the CPLD have been designed as finite state machines (FSM). Since the state machines are all explained along with this text, a uniform way to describe their interface is introduced here.

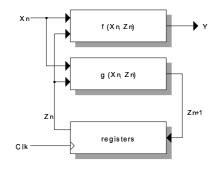

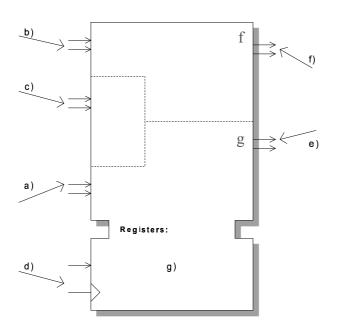

A state machine generally can be written as a Mealy Automaton. A symbolic view of a Mealy Automaton is show in Figure 1.1. This view of an automaton is used to introduce a diagram, which shows all involved signals of the state machine and their influence on the automaton. Figure 1.2 shows a detailed description of this diagram.

Figure 1.1: Mealy automaton

Figure 1.2: Overview diagram of a state machine

- a) Input signals that can only affect the next state

- b) Input signals that can directly change the output

- c) Input signals that can directly affect both the output and the next state

- d) Reset and clock signals

- e) Output signals that only change with the clock (generated from the state)

- f) Output signals that may change between clock cycles

- g) Optionally: Registers used to store the state of the FSM

### Chapter 2

### System Architecture

The *Embedded Task Machine* runs on two hardware modules: the BTnode[1] and the BTnodeFPGA[7]. These modules have been developed at the TIK institute and used for earlier projects. The idea behind the project was to use the FPGA on the BTnodeFPGA board as a computing device, since the microcontroller of the BTnode would be too weak for many signal processing applications. The execution of this kind of applications is the intended purpose of the system, which is supposed to run in a network of intelligent sensing devices. These sensors would process much of the data before sending it to some controlling device, reducing the data volume transmitted and spreading the computation load over many devices.

Since the sensor hardware may be too small to hold an entire application configuration, the application is split into smaller parts, called *tasks*, and a description of how these tasks exchange data, called the *coordination description*. These two information items are then send to the executing device, where the tasks then can be scheduled to run separately over time on the hardware. This way area is saved by requiring a longer execution time.

### 2.1 The Execution Model

### 2.1.1 Modules of the Execution Model

In order to be able to execute an application which is split into different tasks and a coordination description, different modules are needed. A first module is the *task repository* which holds the different tasks to be executed in

Figure 2.1: Overview of the Embedded Task Machine

a form which is smaller than when it is actually executed. A second module is the *relation memory*, where all the data is kept, which is interchanged between the tasks. The relation memory must be able to keep the data while the tasks are switched and executed. A third module would be the *task runner*, this is where the tasks are actually executed. It must be a reconfigurable device with a short enough reconfiguration time. Last, but not least, a *scheduler* is needed, which controls, at what time which task runs. This module is interpreting the coordination description.

### 2.1.2 Mapping the modules to the hardware

In order to design the system, the different modules of the Execution Model need to be mapped to the available hardware. The resources on the hardware modules are listed in Table 2.1. The different chips on the hardware modules have different properties which should be exploited for the system.

Obviously the task runner module needs to be placed on the FPGA of the BTnodeFPGA, since this is the only reconfigurable hardware module which

| BTnode                       | BTnodeFPGA             |

|------------------------------|------------------------|

| ATMega128L Microcontroller   | Xilinx CoolRunner CPLD |

| ROK 101 007 Bluetooth module | Xilinx Spartan II FPGA |

| AMIC 500kBit or 2MBit SRAM   | AMD 1MByte Flash       |

|                              | AMIC 4MBit SRAM        |

Table 2.1: Resources on the hardware modules

provides enough space to be able to execute tasks of sufficient size.

For the relation memory it is best to use the 4MBit SRAM since it has a direct connection to the FPGA, where the data is needed. A memory manager is needed to control the access of the data stored in the SRAM. It has to be placed between the task and the SRAM and is also placed on the FPGA.

The task repository is assigned to the Flash memory. The Flash does not loose the stored data on a power loss and thus provides a save place for the rather big configuration files which do not need to be retransmitted after a restart of the BTnodeFPGA. The administration of the different task slots on the Flash is implemented in the CPLD. The advantage of the CPLD is that it does not loose its configuration on a power-down as the FPGA does. The CPLD can also be used for an initialization of the whole board. The CPLD also gets the duty of reconfiguring the FPGA.

The scheduler is programmed for the microcontroller on the BTnode, since its work is highly data dependent and thus well suited to be executed on a microcontroller. The scheduler also calculates the sizes of the FIFOs in the relation memory and initializes the memory access structures used by the memory manager on the FPGA.

### 2.2 MC-Protocol

The microcontroller (MC) on the BTnode and the CPLD on the BTnodeFPGA communicate using an UART serial interface. The microcontroller uses this connection to control the the whole BTnodeFPGA board. The board also can send back messages through this connection. The protocol has two layers, differentiated between CPLD and FPGA commands.

### 2.2.1 Commands to the CPLD component

In order to create a fast communication the protocol header size is kept very small. I does not even contain any checksums. The length varies depending on the command. Each command consists of one byte header and a custom number of bytes as parameter:

| 4        | 4    |            |

|----------|------|------------|

| CPLD Cmd | Slot | Parameters |

The parameter "Slot" indicates the Flash slot addressed for most CPLD commands. If this parameter is not used, it should be set to 0x0. The CPLD understands the commands listed in Table 2.2. If a command is expected to be sent to the FPGA, the CPLD command FPGA Cmd must be sent as further explained in Table 2.2.

| Command    | Code            | Slot | Parameter                                    |

|------------|-----------------|------|----------------------------------------------|

| Store Task | 0xA             | yes  | 24       Len of Data     Data                |

| Conf Slot  | 0x9             | yes  | none                                         |

| Read Task  | 0x5             | yes  | none                                         |

| Erase Chip | 0xC             | no   | none                                         |

| Erase Slot | 0x3             | yes  | none                                         |

| FPGA Cmd   | $0 \mathrm{xF}$ | no   | 8 8<br>Len of Cmd Cmd Param                  |

|            |                 |      | Len of Cmd defines size of Cmd<br>and Param. |

Table 2.2: Commands interpreted by the CPLD. Column Slot shows if this field is used with this command. If it is not used, this parameter must be set to 0x0.

### 2.2.2 Commands to the FPGA

The commands to the FPGA have two layers, the first layer contains the FPGA Cmd command to the CPLD, which routes the next Len of Cmd bytes to the FPGA. The first of these bytes contains the command for the FPGA, the remaining its parameters. The following commands can be sent to the FPGA:

### Run Task

### FPGA-Command code: 0x01

This command is used to start an already loaded task for a given number of cycles. The FIFO buffers used for the task and the input/output tasks are supplied with the command message. If the task has completed it replies with TASKTERMINATED. The command may reply with a NACK if a task is already running. A list of response codes can be found in Section 2.2.3. The syntax of the command is given here:

| 8    | 8     | 8     | 8     | 8     | 8     | 8     | 16     |

|------|-------|-------|-------|-------|-------|-------|--------|

| 0x01 | Port1 | Port2 | Port3 | Port4 | Port5 | Port6 | Cycles |

*Note:* Cycles indicates the number of iterations the task has to be executed (and not the clock cycles!). The Port-parameters have the following setup:

| 2             | 6           |  |

|---------------|-------------|--|

| Driver config | FIFO-Number |  |

*Driver config* defines if this port is used by input or output driver. Please make sure you always configure an input and an output port. If you don't need the drivers, attach it to an unused FIFO.

| Value | Description            |

|-------|------------------------|

| 00    | No driver attached     |

| 10    | Output driver attached |

| 11    | Input driver attached  |

| 01    | Not allowed            |

*FIFO-Number* is the FIFO number to be mapped to this port. See Section 2.4 for more detail.

#### Write SRAM

#### FPGA-Command code: 0x10

You can directly write to the SRAM on the BTnodeFPGA. Since data is written to the SRAM in 16-bit WORDS, the supplied data must have an even byte length. The Length parameter holds the number of WORDs to be written. The first WORD is written to the address passed along in the Address parameter. Because the address has a 18-bit width, it needs two additional bits which are taken from the length parameter byte. With this setup a maximum of 64 WORDs (128 Bytes) can be written at once. The command replies with an ACK if it has successfully completed. The syntax of the command is given here:

| 8    | 6      | 18      |      |

|------|--------|---------|------|

| 0x10 | Length | Address | Data |

*Note:* Only the 6 most significant bits of the second byte contain the Length parameter. Length means data size in 16-bit WORDs.

### Read SRAM

FPGA-Command code: 0x11

This command reads data from the SRAM. The Length parameter holds the number of WORDs to be read. The first WORD will be read from the supplied address. Because the address has a size of 18-bit it uses the two most least significant bits of the second byte. Each WORD is returned separately in a data packet. The packet header is DATA. See Section 2.2.3 for more detail.

The syntax of the command is given here:

| ſ | 8    | 6      | 18      |  |

|---|------|--------|---------|--|

|   | 0x11 | Length | Address |  |

Note: Length indicates the data size in 16-bit WORDs.

### 2.2.3 Response from FPGA module

The CPLD may answer to a command from the MC either with an ACK or a NACK. In these cases, there is no additional data attached. If the FPGA sends information, the message contains a message code and one WORD of data. Possible message codes can be found in Table 2.3. The packets have the following setup:

| 8            | 16   |

|--------------|------|

| Message Code | Data |

| Message      | Code | Data | Description                    |  |

|--------------|------|------|--------------------------------|--|

| ACK          | 0x33 | no   |                                |  |

| NACK         | 0x66 | no   |                                |  |

| TASKFINISHED | 0xCC | no   | The running task has finished. |  |

| DATA         | 0xAA | yes  | Data returned answering a FPGA |  |

|              |      |      | command. E.g. SRAM read.       |  |

| OUTPUT       | 0x99 | yes  | Data sent by output driver.    |  |

Table 2.3: List of response messages codes

### 2.3 FPGA-Protocol

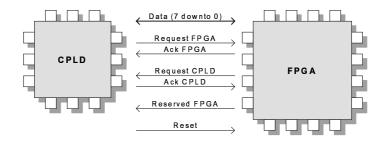

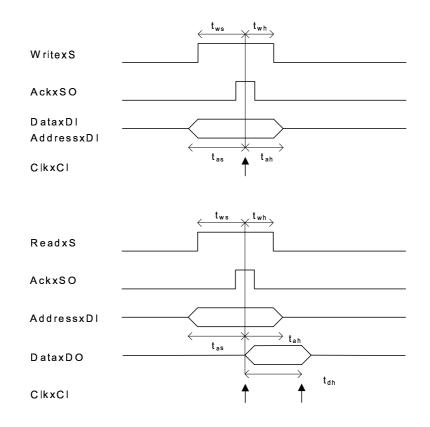

There are 16 wires available between the CPLD and the FPGA. Eight out of them are used to create a 8-bit data bus. 5 are used for communication control and one is used to reset the FPGA. Two lines are left unused. An overview of the connections can be seen in Figure 2.2.

Figure 2.2: Wires between CPLD and FPGA

### 2.3.1 Data flow

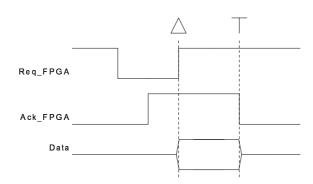

The protocol setup is designed to work with differing clocks on the CPLD and the FPGA. This requires a longer handshake but since most communication will be forwarded trough the RS232 interface anyway, this does not matter. The transmission of one byte requires at least 5 clock cycles.

Communication starts by setting request line high. The receiver accepts by setting its acknowledge line high. If the receiver is still busy, it will not accept until it is ready to do so. When the acknowledge line is high, data can be placed on the data lines and request line turns low. Communication is terminated by setting the acknowledge line to low. The data line access must remain on high impedance if the remote acknowledge line is not high. A timing diagram of the whole communication is shown in Figure 2.3.

Figure 2.3: Timing details of a single write cycle from CPLD to FPGA

The implementation of the protocol slightly differs between the CPLD and the FPGA. In case both modules try to send to the bus, the CPLD has a higher priority. There is an additional line named FPGA\_Res, which the FPGA uses to signal a multi-byte packet is being sent to the CPLD. This line is used by the CPLD to ensure that the packet will be transmitted without interruption to the RS232 module. This way a complete packet can safely be sent from the FPGA to the MC. The signal does not change the communication priority between the CPLD and the FPGA in any way.

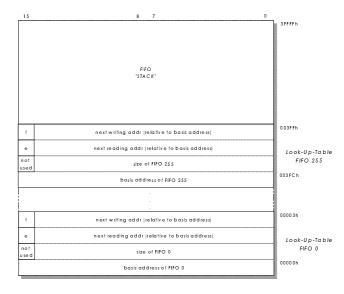

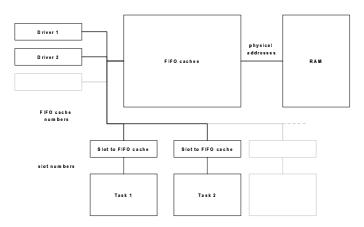

### 2.4 FIFO structure in the SRAM

The FIFOs is where the drivers and the tasks store their input and output data. This data is stored in the SRAM on the module, since it has to survive a reconfiguration of the FPGA but not a power down of the BTnodeFPGA board.

The data structure used to store the structure of these FIFOs has been imported from [5] and can be examined in Figure 2.4. The FIFO access information is stored in the lowest address space of the SRAM, occupying 4 addresses per FIFO. The rest of the address space is free for FIFO data. For every FIFO the following items are stored:

Figure 2.4: SRAM FIFO structure (image from [5])

- The **base address** indicates where the FIFO starts in the SRAM memory. Since the SRAM address is 18bit wide, and the SRAM word only 16 bit, the base address needs to be multiplied by 4 to get the actual address. A FIFO can thus only start at every fourth address.

- The second entry is the **FIFO size**. It indicates how many 16 bit words a FIFO can store. Together with the base address, the FIFO size determines the address range a FIFO occupies in the SRAM. This way, the FIFO structure would allow other data to be stored in the unused space of the SRAM.

- The **next reading address** is a relative address that indicates which data item is to be read next. After every read, it is incremented and wrapped around to 0 if the maximum relative address (the FIFO size) is reached. The address is given relative to the base address and must be added to it.

- Similarly, the **next writing address** points to the data item which can be overwritten on the next write access. This address is relative to the base address as well.

• In case the *next reading address* and the *next write address* point to the same address, two **full and empty bits** are stored at the addresses most significant bits to indicate whether the FIFO is full or empty.

The FIFO structure is accessed by the FIFOControl (see Section 4.7) to determine the FIFO locations. The FIFO structure must be created before starting the task by the microcontroller using the FPGA commands listed in Section 2.2.2.

### 2.5 Task slots in Flash

The BTnodeFPGA comes with an AM29LV081B[8] Flash chip that has 1 MByte of storage space. It is organized in 16 blocks of 64 KBytes. This is enough space to store 5 tasks with a full FPGA configuration size of 167'053 bytes, which uses three slots on the Flash. A detailed organization scheme of the Flash can be found in Figure 2.5.

| Sector  | Sector Size | Address-Range | Task Slot |  |

|---------|-------------|---------------|-----------|--|

| SA0     | 64 Kb       | 00000h-0FFFFh | unused    |  |

| SA1     | 64 Kb       | 10000h-1FFFFh |           |  |

| SA2     | 64 Kb       | 20000h-2FFFFh | Slot 0    |  |

| SA3     | 64 Kb       | 30000h-3FFFFh |           |  |

| SA4     | 64 Kb       | 40000h-4FFFFh |           |  |

| SA5     | 64 Kb       | 50000h-5FFFFh | Slot 1    |  |

| SA6     | 64 Kb       | 60000h-6FFFFh |           |  |

| SA7     | 64 Kb       | 70000h-7FFFFh |           |  |

| SA8     | 64 Kb       | 80000h-8FFFFh | Slot 2    |  |

| SA9     | 64 Kb       | 90000h-9FFFFh |           |  |

| S A 1 0 | 64 Kb       | A0000h-AFFFh  |           |  |

| S A 1 1 | 64 Kb       | B0000h-BFFFFh | Slot 3    |  |

| S A 1 2 | 64 Kb       | C0000h-CFFFh  |           |  |

| S A 1 3 | 64 Kb       | D0000h-DFFFFh |           |  |

| S A 1 4 | 64 Kb       | E0000h-EFFFh  | Slot 4    |  |

| S A 1 5 | 64 Kb       | F0000h-FFFFFh |           |  |

Figure 2.5: Organization of the task slots in the Flash

### Chapter 3

# **CPLD-Design**

The CPLD is the controlling unit on the BTnodeFPGA[7] board. Over an UART interface, it receives the commands to be executed by the different components. Its duties include writing and reading to the Flash and configuring the FPGA.

### 3.1 CPLDTop

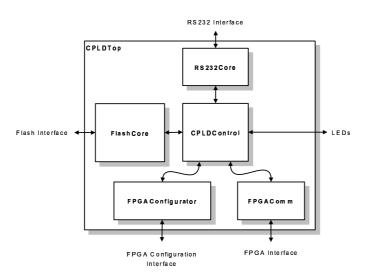

The CPLDTop entity is main entity of the CPLD. It does not include any logic but only interconnects the different entities of the CPLD and the external interfaces as shown in Figure 3.1.

The entities interconnected by CPLDTop are:

- The RS232Core, which handles all communication over the UART interface

- The FlashCore realizes all transactions to the Flash storage of the BTnodeFPGA board

- The FPGAConfigurator controls the configuration interface of the FPGA during the reconfiguration process

- The FPGAComm forwards the communication between the FPGA and the microcontroller to the RS232Core

- The CPLDControl finally controls all operations within the CPLD

Figure 3.1: The architecture of the CPLD

### 3.2 CPLDControl

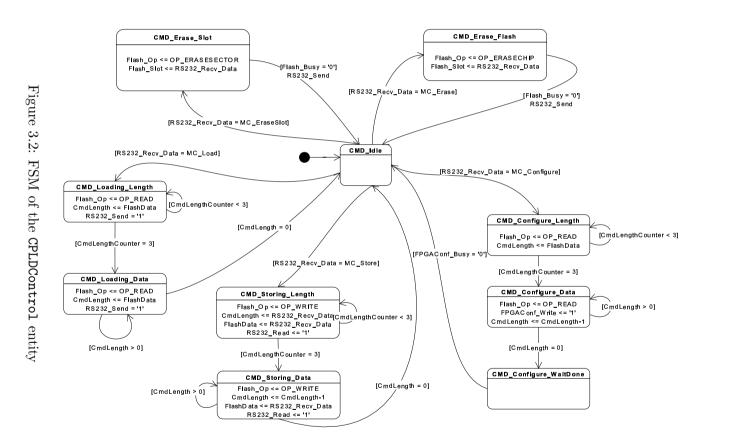

The CPLDControl is the "mind" of the CPLD. It accepts commands coming from the BTnode and controls their execution. It essentially executes the MC-Protocol described in Section 2.2.

The Finite State Machine (FSM) of the CPLDControl is shown in Figure 3.2.

### 3.3 RS232Core

### 3.3.1 Description

The RS232Core handles the communication over the UART interface of the BTnodeFPGA board. The entity has originally been programmed by Silvan Wegmann and further improved Roman Plessl. It is easily adapted to different baud rates and entity clocks. The baud rate for this project has been set to 115'200 bps with a clock of 18.432 MHz<sup>1</sup>. This is the highest baud rate that most devices support. Higher baud rates can be used by changing the generics of the instantiation of the RS232Core in the CPLDTop entity code. However, this should well considered because different handshakes between

<sup>&</sup>lt;sup>1</sup>The original BTnodeFPGA oscillator with 10Mhz has been replaced on this board. The UART interface can better be controlled with the new oscillator

the entities have been simplified with the assumption of the RS232Core having a long delay to send and receive data.

The final interface for the RS232Core module is the following:

```

entity rs232core is

generic (

Clockfrequency : natural := 18432000;

Baudrate

: natural := 115200

);

port (

-- internal ports

Send

: in std_logic;

WE

: in std_logic;

Send_Ready : out std_logic;

Send_Data : in

std_logic_vector(7 downto 0);

Read

: in

std_logic;

Data_Ready : out std_logic;

Recv_Data : out std_logic_vector(7 downto 0);

-- external ports

RX

: in std_logic;

ΤX

: out std_logic;

-- standard ports

ClkxCI

: in std_logic;

RstxRBI

: in std_logic

);

end rs232core;

```

Listing 3.1: Entity declaration of the RS232Core

### 3.3.2 Usage

If data has been received, the Data\_Ready signal turns high to indicate that the data lying on Recv\_Data is valid. The Data\_Ready signal turns low again as soon as it is acknowledged by the other part setting the Read signal to high. The Recv\_Data will then remain valid until the next whole byte has been received over the RS232 interface. If a new byte has arrived, the Recv\_Data buffer data will be replaced, regardless if the existing data has been acknowledged or not.

To send data, the send buffer first has to be filled with data. This is done by setting the WE signal high while the data to be sent lies on Send\_Data. The sending process is started when the Send signal is set to high. The Send and WE signals can be set concurrently. Send\_Ready turns to low when sending and will return to high when all data has been sent.

**RS232Core** implements two separate buffers for reading and writing such that these operations can be carried out concurrently.

## 3.4 FlashCore

#### **3.4.1** Description

The FlashCore is used to read, write (program) and erase the AM29LV081B Flash chip. It is the only entity with direct contact to the Flash chip to hide the details of the protocol to the other entities on the CPLD.

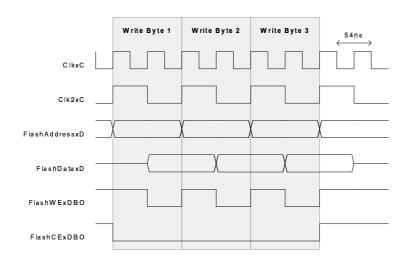

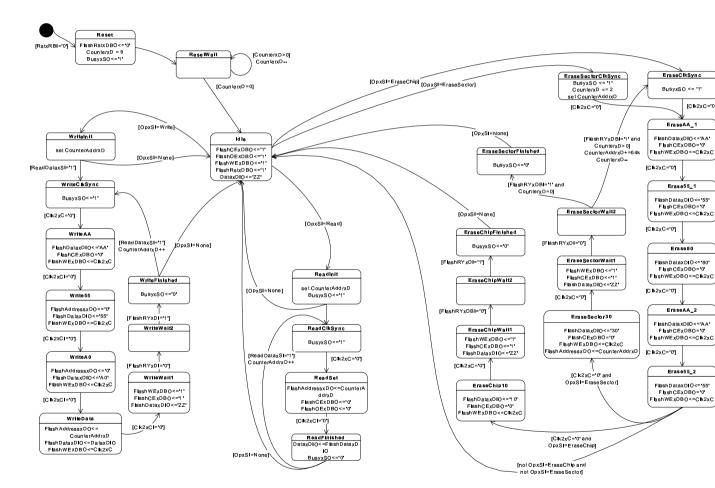

The AM29LV081B needs exact timing settings. These can be found in the AM29LV081B data sheet[8]. The FlashCore FSM uses a clock at half the speed of the original clock. A timing diagram of the Flash access procedure can be examined in Figure 3.3. FlashCore has been designed such that no external entity needs to know about the timing details of the Flash chip.

#### 3.4.2 Usage

The Flash memory has been organized in task slots. Further details are explained in Section 2.5. Data cannot be written explicitly to certain addresses of the Flash. Read and write operations always start at the beginning of a slot. An internal counter increments the memory address after each Flash read/write cycle.

The FlashCore has a simple internal interface: OpxSI defines the current operation of the entity. This signal may only be changed when BusyxSO is low. If an operation is completed, the FSM is returned to its idle state by setting OpxSI to 000 (None code). The available operation codes are listed in Table 3.1. The SlotNumberxDI signal defines the slot number on which the operation has to be performed. This number must be between 0 to 4 and needs to be valid for the whole duration of the operation. ReadDataxSI is used initiate the read or write operation of the next byte of the stream.

Figure 3.3: Timing diagram of the Flash access. This diagram shows a write operation of three bytes. The FlashWE# pin is directly connected to Clk2xC during the write process. This makes it possible to implement the write operation of one byte in a single FSM state. FlashDataxD has to be delayed.

The signal must be set high for one clock cycle. BusyxSO is high when a Flash operation is in progress, inputs should not be changed during this time for safe operation. DataxDO and DataxDI are used to access written or read data. DataxDI is buffered, so the input signal can be changed one clock cycle after ReadDataxSI had been high at the rising clock edge.

| Operation   | Code |  |

|-------------|------|--|

| None        | 000  |  |

| Read        | 001  |  |

| Write       | 010  |  |

| EraseSector | 100  |  |

| EraseChip   | 101  |  |

Table 3.1: FlashCore operation codes

3.4

FlashCore

Chapter

ယ

tion of the three commands: write, read and erase Figure 3.4: Finite State Machine of the FlashCore. Note the implementa-

Figure 3.5: Overview of the Finite State Machine of the FlashCore

#### 3.4.3 The state machine

The FlashCore FSM is build out of 31 states. An interface overview is presented in Figure 3.5. The detailed FSM can be examined in Figure 3.4.

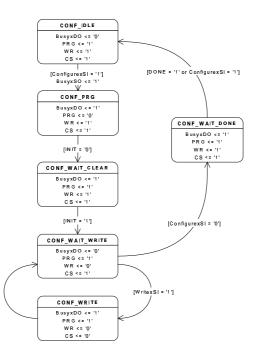

## 3.5 FPGAConfigurator

#### 3.5.1 Description

The FPGAConfigurator entity reconfigures the FPGA connected to the CPLD using the configuration port in *Slave Parallel Mode*. The configuration data is provided by the FlashCore module which is synchronously controlled by the CPLDControl entity during the configuration process. Thus, the FPGAConfigurator just drives the configuration controls ports and does not care about the configuration data ports on the FPGA.

The configuration process for a Spartan2 FPGA is described in more detail in [9]. The process has been modeled as the FSM as shown in Figure 3.5.1 and Figure 3.5.1.

#### 3.5.2 Usage

To start a configuration of the FPGA, ConfigurexSI has to be set to high and should remain high. BusyxSO will then immediately turn high and not return to low until the FPGA is ready to accept the configuration data. As

Figure 3.6: The FSM model for the FPGA configuration process

Figure 3.7: The interface of the FPGAConfiguratorFSM

soon as BusyxSO is low, the configuration data writing cycles start. The controlling unit should make sure that valid data lies on the parallel slave configuration data ports of the FPGA and set the WritexSI signal to high. The FPGAConfigurator then signals the FPGA to read the configuration data. BusyxSO will turn high for this time and return to low again as soon as the FPGA is ready for the next configuration data byte.

When all configuration data has been written, the ConfigurexSI signal can be set to low. The FPGAConfigurator will answer by setting BusyxSO to high, and waiting for the FPGA to complete the reconfiguration. Then, BusyxSO is set low again, and FPGAConfigurator is ready for another configuration process

Note: The configuration data is not checked to be valid. If the configuration is not accepted by the FPGA, it does indicate this by leaving its FPGAConfig\_INITxDBI signal low. FPGAConfigurator does ignore this signal in this state. Thus it may happen that the FPGA has not been reconfigured and remains in its previous configuration.

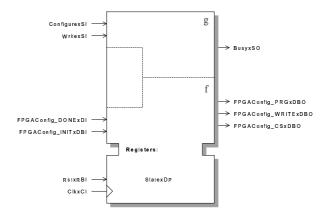

## 3.6 FPGAComm

#### **3.6.1** Description

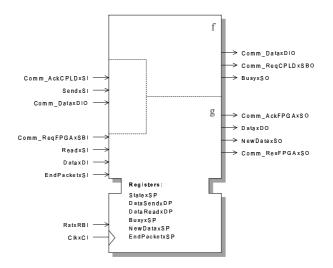

The FPGAComm module is used to implement the interface to the CPLD. The custom protocol described in Section 2.3 is used for communication. The state machine used is shown in Figure 3.9. An interface description can be examined in Figure 3.8.

#### 3.6.2 Usage

The state machine works asynchronously. All communication lines are buffered. To write a byte to the FPGA, DataxDI must be set and SendxSI tied to high for one clock cycle. BusyxSO then goes low until the byte could be successfully sent. Newly received data is signaled by the NewDataxSI signal turning high. Data then can be read from DataxDO. ReadxSI must be tied high for one clock cycle to acknowledge the reading of the received byte. Because the state machine works asynchronously, it is possible to receive a byte before the byte waiting to be sent is actually sent.

Figure 3.9: FPGAComm FSM

## Chapter 4

# **FPGA-Design**

The FPGA is the execution unit for the tasks. It starts and stops the tasks and controls their memory accesses. The FPGA also holds drivers for its external interfaces, where input data for the applications can be collected.

## 4.1 FPGATop

The FPGATop module interconnects the different entities of the FPGA design. Figure 4.1 shows the structure of the architecture. A short description of the different entities is given below:

- $\bullet$  CPLDComm handles the communication to the CPLD

- $\bullet\,$  SRAMCore reads and writes to the SRAM on the <code>BTnodeFPGA</code> board

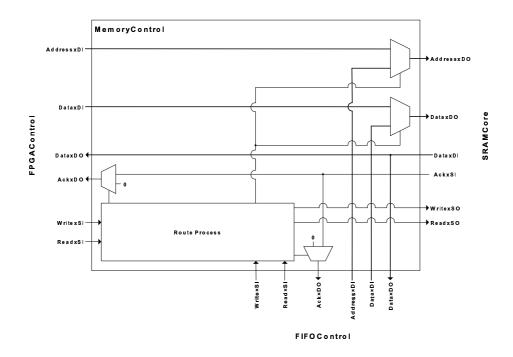

- MemoryControl handles concurrent access requests to the SRAMCore by the FIFOControl or the FPGAControl entities

- FIFOControl acts as a cache for FIFO accesses by the Task, InputDriver, and OutputDriver entities

- The InputDriver generates or reads data from an external interface of the FPGA and feeds it to a FIFO

- The OutputDriver sends data from a FIFO over the CPLD to the microcontroller

- The FPGAControl accepts commands passed by the CPLD from the microcontroller and executes these on the FPGA

Figure 4.1: FPGA Architecture

• The Task entity is where the custom tasks are configured to and executed

## 4.2 FPGAControl

#### 4.2.1 Description

FPGAControl is the main controller on the FPGA. It has two general purposes: Firstly, it accepts incoming commands from the CPLD and executes them. Secondly, it stores back the cached FIFO structure data and signals the termination of the task to the CPLD when the running task has finished.

Three commands are currently understood by the FPGAControl: the commands to read and write to the SRAM and to start the task. How these commands can be sent to the FPGA is described in Section 2.2.2.

#### Read SRAM and Write SRAM

These two commands are used to read and write directly to the SRAM. Writing is usually used to initialize the FIFOs before an application is started. Reading has been implemented for debugging purposes.

#### Start task

Before a task can be started, the FIFO structure data used by the task must be loaded into the cache. Section 4.7 describes the procedure in further detail. The required FIFO numbers are submitted as parameters of the StartTask command. After the initialization of the FIFOs, a signal to TaskControl allows it to start the task.

Figure 4.2 shows a symbolic state chart of FPGAControl. It is not specified when the transitions occur to simplify the figure.

Figure 4.2: Symbolic state chart of FPGAControl

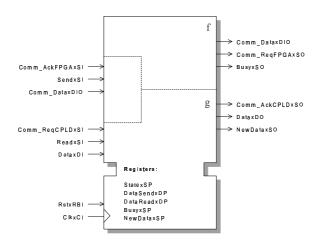

## 4.3 CPLDComm

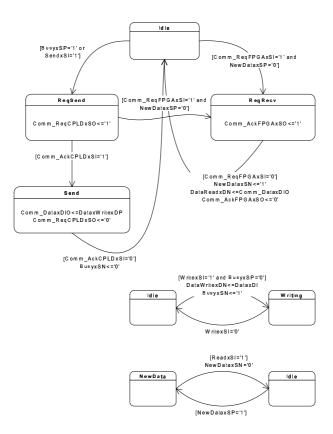

#### 4.3.1 Description

The CPLDComm module is used to handle the interface to the CPLD which uses the FPGA-Protocol described in Section 2.3. CPLDComm is very similar to the FPGAComm on the CPLD described in Section 3.6. The most important difference is that the access priorities differ. If the CPLD requests to send a byte, it has priority over the FPGA. Because the FPGA won't accept a new byte if the old one hasn't read and the CPLD has priority to send, it is important that every data that has arrived is taken from the receiver's buffer. If the FPGA tries to send a byte and doesn't read received data a deadlock may happen! The FSM modeling the protocol is shown in Figure 4.4. An interface description can be found in figure 4.3.

Figure 4.3: Overview of the module CPLDComm

#### 4.3.2 Usage

The state machine works asynchronously. All communication lines are buffered. To write a byte to the CPLD, DataxDI must be set and SendxSI tied high for one clock cycle. BusyxSO goes low when the byte could be successfully sent. Newly received data is signaled by the signal NewDataxSI turning high. Data can then be read from DataxDO. Then, ReadxSI must be tied high for one clock cycle to acknowledge the byte. Because the state machine works asynchronously, it is possible to receive a byte before the the byte to send could be sent.

The FPGA-Protocol provides a special line for the FPGA to reserve a communication line to the Btnode. It is automatically used and therefore the last byte of any packet must be marked by additionally setting EndPacketxSI to high when sending the last byte by triggering SendxSI. This must even be done for a single byte packet.

Figure 4.4: CPLDComm FSM

## 4.4 OutputControl

The OutputControl entity is used to share the CPLDComm communication entity between the the FPGAControl and the output driver. The same packeting mechanism as used on the CPLDComm interface is used to reserve the interface for a multi-byte data transmission. FPGAControl has a higher priority when writing to the data bus.

The advantage of using the same interface as the CPLDComm entity is that the connected modules do not have to be changed when directly connected to the CPLDComm. The entities do not notice that other modules are currently sending data since the OutputControl signals to the requesting entity that the external interface busy until its first byte has been transmitted.

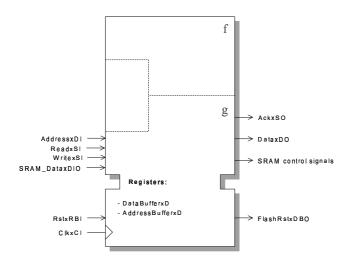

## 4.5 SRAMCore

#### 4.5.1 Description

The SRAMCore entity controls the SRAM of the BTnodeFPGA board that is connected to the FPGA. A detailed description of how the data in the SRAM can be accessed can be found in [10].

A problem has been encountered on BTnodeFPGA boards with a 18 MHz clock: since their clock cycle is 54ns, and the read and write cycles of the SRAM takes 55ns according to the specifications. Thus the SRAM should be slightly to slow for this clock. Two clock cycles are thus needed to access data on the SRAM. However, on the BTnodeFPGA board used for development, the SRAM worked with one clock cycle of the 54ns clock, too. The SRAMCore entity supports both access cycles, the required code for a two cycle access is commented in the source code.

#### 4.5.2 Usage

To write a byte, the data and the address have to be set to DataxDI and to AddressxDI respectively. When WritexSI is set to high, the address and data must not change until the writing procedure has been acknowledged by the SRAMCore setting its AckxSO signal to high. The data can be considered written as soon as the WritexSI and the AckxSO signal have been high at a rising clock edge. If the WritexSI signal is kept high after AckxSO has been set, a new write cycle is initiated. Thus before changing any data, the

Figure 4.5: Interface of the SRAMCore entity

WritexSI signal must be removed immediately after the AckxSO signal has gone to low.

| Setup times |                | Hold times |                |

|-------------|----------------|------------|----------------|

| $t_{ws}$    | $\geq 1$ cycle | $t_{wh}$   | 0              |

| $t_{as}$    | $\geq 1$ cycle | $t_{ah}$   | 0              |

| $t_{ds}$    | -              | $t_{dh}$   | $\geq 1$ cycle |

Table 4.1: SRAMCore handshake timings

To read data, the address has to be set on AddressxDI and the ReadxSI signal has to be set to high. The address should not be altered until SRAMCore acknowledges the reading procedure by setting the AckxSO signal to high. A read cycle is considered complete when the AckxSO and the ReadxSI signal have been high at a rising clock edge. After this event, the data liess on DataxDO for at least one clock cycle. If the ReadxSI remains on high after the AckxSO has been set to low, a new read cycle is initiated. The data is buffered in the SRAMCore and will not change until another operation (read or write) is started.

Chapter 4

Figure 4.6: SRAMCore handshake, timing values are listed in Table 4.1

Note: If both the ReadxSI and the WritexSI signal are set, the read operation is executed since it does not change the data stored in the SRAM.

## 4.6 MemoryControl

#### 4.6.1 Description

The MemoryControl entity coordinates the access to the SRAM. Two units can write to the SRAM: FPGAControl and FIFOControl. MemoryControl takes care that only one of these two units is accessing the SRAM at any point in time. It blocks the interface to an entity while another is accessing the SRAM.

Priority is given to the FIFOControl since the task or the drivers are doing the actual work and should not be impeded by configuration messages received from or sent to the controller.

Figure 4.7: Structure of the MemoryControl entity

## 4.6.2 Usage

FIFOControl and MemoryControl can both use the interfaces of the MemoryControl as if they would directly be connected to the SRAMCore (see Figure 4.6 for details on the protocol used). There is no additional delay inserted, since MemoryControl observes the handshake and knows when it can switch from one to the other entity.

## 4.7 FIFOControl

#### 4.7.1 Description

This entity wraps two modules that have been inherited from an earlier project[5]. These are the Address\_Register and the LUT\_Address entities. These modules handle the data structure of the FIFOs in the SRAM. This structure is explained in more detail in Section 2.4.

To reduce the latency of a memory access, the FIFO configurations are loaded into a cache in the Address\_Register module. The module keeps track of every read and write access and increments the associated pointers.

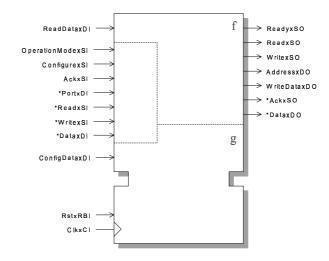

Figure 4.8: FIF0Control interface. Signals marked with a \* are common interface signals for the different consumers

It also handles wrap overs<sup>1</sup>. The FIFO data structure in the SRAM is not altered. Before changing the task, the modified data in the Address\_Register needs to be written back into the SRAM.

The Address\_Register only keeps hold of as many FIFOs as are allowed to be ports of a task, plus two for the input and output drivers. Thus it automatically maps the port number to the corresponding FIFO in the SRAM. This mapping is conducted during the initialization process when the FIFO data is loaded into the different ports in the Address\_Register module. The proper addresses for loading the FIFO data structure are generated by the LUT\_Address module. The mapping is also stored into a buffer which is used to again generate the FIFO data structure addresses in the write back phase after a task has finished its execution cycles.

The FIFOControl entity has five interfaces. It provides three interfaces to the entities who use the FIFOs: the task, the input driver, and the output driver. These interfaces are basically used for requests to write or read something to a FIFO. Using the interface to the MemoryControl entity,

<sup>&</sup>lt;sup>1</sup>When data is written to the last entry of the reserved FIFO space, the pointer is set back to its beginning

the FIFOControl can access the memory after having computed the physical address the request needs. The last interface connects to FPGAControl and is used for configuration purposes as further explained below.

#### 4.7.2 Usage

Before the FIFOControl can be used, the FIFO data structure must already be present in the SRAM. This configuration has to be done externally using the MC-Protocol as defined in Section 2.2. The required structure is explained in Section 2.4.

If the FIFO data structure is present in the SRAM, the FIFOControl can be configured with other commands over the MC-Protocol. The FPGAControl extracts the necessary information from these commands and configures the FIFOControl unit. After the configuration is done, the FIFOs can be accessed by the task, the input, and the output drivers. After the task has finished its cycles, the FIFOControl needs to be instructed to write back its data before a new task FIFO configuration can be loaded into the FIFOControl.

These steps are now explained in further detail:

#### Configuration

When the ReadyxSO signal is high, the FIFOControl can be driven into configuration mode by setting OperationModexSI to LoadFIFO. ReadyxSO will turn to low and will return to high as soon as FIFOControl is ready to accept its first configuration byte. Now it expects the FIFO number of the first port, which can be submitted by setting ConfigDataxDI to the FIFO number and setting ConfigUrexSI to high for one clock cycle. The ConfigDataxDI must remain high until ReadyxSO turns back to high again. After the impulse on ConfigUrexSI, FIFOControl loads the data associated with that FIFO<sup>2</sup> into its buffer for its first port.

Subsequent impulses on ConfigurexSI will initiate the configuration of the next port with the FIFO data for the FIFO number given by ConfigDataxDI. New impulses are not accepted until ReadyxSO turns back to high. This configuration procedure is halted by changing OperationModexSI to AccessFIFO. If more ports are loaded than there are physically provided, a wrap around

$<sup>^{2}</sup>$ The physical address of for the first data item (base address) is computed by multiplying the FIFO number by 4

occurs and the configuration of the first port will be overwritten. Thus the configurator is responsible of not assigning too many FIFOs to the ports.

#### Write Back

After the task has finished its execution, the FIFO state must be written back to the SRAM before a new configuration is loaded. This can be done by driving OperationModexSI to StoreFIFO when ReadyxSO is high. FIFOControl will now start to write the FIFO configurations into the SRAM. OperationModexSI must remain on LoadFIFO until ReadyxSO returns to high. Changing OperationModexSI before the time will force FIFOControl back into idle mode, but leaving all FIFOs not yet written to the SRAM as they are.

#### **FIFO Access**

After a configuration has been loaded into FIFOControl,OperationModexSI can be changed to AccessFIFO, and FIFO accesses can be made. The hand-shake works like the one presented for the SRAMCore and displayed in Figure 4.6, with the PortxDI signal replacing AddressxDI. Priorities are given in the following order: Task Read, Task Write, InputDriver Write, Output-Driver Read.

It is important that **\*PortxDI** does not change while **\*WritexSI** or **\*ReadxSI** are driven high.

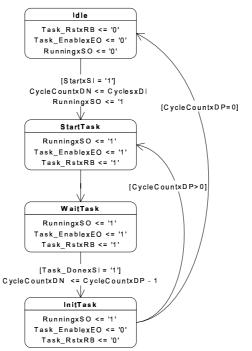

## 4.8 TaskControl

#### 4.8.1 Description

TaskControl is used to control a task. It receives a cycle count and a start signal from FPGAControl and executes the task for the given number of cycles. When the task has finished its iterations, RunningxSO turns low to signal the task has terminated.

The cycle count holds the number of times the task will be restarted after termination. Figure 4.9 shows the state chart.

Figure 4.9: TaskControl state chart

## 4.9 Task

#### 4.9.1 Description

The task module is where the actual work is done. Here custom modules can be placed which use the interface shown in Listing 4.1.

A task is controlled through the *execution control ports*. These are used to start and stop the execution of a task. In every iteration, the following signal forms are expected:

- 1. RstxRBI is driven low to reset the task. A task iteration must only depend on data stored in the FIFOs and no internal state that should be kept from one iteration to another. DonexSO must now turn to low, indicating the task is ready to run.