MA-2006-05

# Evaluation and Comparison of Performance Analysis Methods for Distributed Embedded Systems

Master's thesis presented by

Simon Perathoner Politecnico di Milano, Italy

Supervisors:

Prof. Dr. Lothar Thiele, Dipl. Ing. Ernesto Wandeler Computer Engineering and Networks Laboratory Swiss Federal Institute of Technology, Zürich

> Prof. Dr. William Fornaciari Dipartimento di Elettronica e Informazione Politecnico di Milano

to my family

# Acknowledgements

First of all I would like to thank Prof. Dr. William Fornaciari for supporting me in writing this thesis abroad.

I would also like to express my sincere gratitude to Prof. Dr. Lothar Thiele for giving me the opportunity to write this thesis in his research group at the Computer Engineering and Networks Lab of the Swiss Federal Institute of Technology (ETH) Zürich. In particular, I would like to thank him for giving me the opportunity to take part in the ARTIST2 Workshop on Distributed Embedded Systems 2005 in Leiden, The Netherlands, which has considerably influenced the outcomes of this thesis.

Most of all I wish to thank Dipl. Ing. Ernesto Wandeler for his constant support throughout the whole project and for his ability to motivate me. Without his valuable input and advice this work would never have been possible.

I am also grateful to Dr. Alexandre Maxiaguine and Dipl. Ing. Simon Künzli for their help during this thesis work.

Finally, my warmest thanks go to my parents and my brother for their love and support during my studies.

### **Abstract**

In this thesis we evaluate and compare a number of system level performance analysis methods for distributed embedded systems. We discuss different criteria for their classification and comparison and evaluate some concrete performance analysis techniques with respect to these criteria. In particular, we examine the modeling power and usability of various approaches, apply the performance analysis methods to a set of benchmark systems and compare the obtained results. We show that there are important differences between methods in terms of modeling effort and accuracy by highlighting some modeling difficulties and analyzing pitfalls of the different formal approaches. Further we present an extendible open-source library for performance simulation of distributed embedded systems based on SystemC and compare the hard performance bounds provided by formal analysis methods with the performance estimations obtained by simulation.

# **Table of Contents**

| 1 | Intr | roducti | ion                                                         | 1  |

|---|------|---------|-------------------------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                                       | 1  |

|   | 1.2  | Contri  | butions                                                     | 2  |

|   | 1.3  | Overv   | iew                                                         | 3  |

|   | 1.4  | List of | f abbreviations                                             | 3  |

| 2 | Per  | formar  | nce analysis of distributed embedded systems                | 5  |

|   | 2.1  | Distrib | outed embedded systems                                      | 5  |

|   | 2.2  | Perfor  | mance metrics                                               | 6  |

|   | 2.3  | Requir  | rements for performance analysis methods                    | 7  |

| 3 | App  | proach  | es to performance analysis                                  | 9  |

|   | 3.1  | Classif | fication                                                    | 9  |

|   | 3.2  | Simula  | ation based methods                                         | 9  |

|   | 3.3  | Holisti | ic scheduling                                               | 12 |

|   |      | 3.3.1   | Schedulability analysis for distributed systems             | 13 |

|   |      | 3.3.2   | Performance analysis for systems with data dependencies     | 14 |

|   |      | 3.3.3   | Performance analysis for systems with control dependencies  | 15 |

|   |      | 3.3.4   | The Modeling and Analysis Suite for Real-Time Applica-      |    |

|   |      |         | tions (MAST)                                                | 17 |

|   | 3.4  | Comp    | ositional scheduling analysis using standard event models . | 17 |

|   |      | 3.4.1   | Standard event models                                       | 18 |

|   |      | 3.4.2   | The SymTA/S analysis approach                               | 19 |

|   |      | 3.4.3   | Extensions                                                  | 21 |

|   | 3.5  | Modul   | lar Performance Analysis with Real Time Calculus            | 22 |

|   |      | 3.5.1   | Variability characterization curves                         | 23 |

|   |      | 3.5.2   | Analysis and resource sharing                               | 24 |

|   |      | 3.5.3   | Extensions                                                  | 27 |

|   | 3.6  | Timed   | automata based performance analysis                         | 28 |

|   |      | 3.6.1   | Modeling the environment                                    | 29 |

|              |            | 3.6.2 Modeling the hardware resources                     | 29         |

|--------------|------------|-----------------------------------------------------------|------------|

|              |            | 3.6.3 Performance analysis                                | 30         |

|              | 3.7        | Remarks                                                   | 32         |

| 4            | PES        | SIMDES - An extendible performance simulation library     | <b>3</b> 5 |

|              | 4.1        | Motivation                                                | 35         |

|              | 4.2        | Performance metrics and modeling scope                    | 36         |

|              | 4.3        | Implementation concepts                                   | 38         |

|              |            | 4.3.1 Event tokens and task activation buffers            | 39         |

|              |            | 4.3.2 Input stream generators                             | 40         |

|              |            | 4.3.3 Resource sharing                                    | 43         |

|              | 4.4        | Future extensions                                         | 46         |

| 5            | Con        | mparison of performance analysis methods                  | <b>4</b> 9 |

|              | 5.1        | Comparison criteria                                       | 49         |

|              | 5.2        |                                                           | 51         |

|              | 5.3        | Comparison of usability                                   | 52         |

| 6            | Cas        | •                                                         | 57         |

|              | 6.1        |                                                           | 59         |

|              | 6.2        | Case study 2: Cyclic dependencies                         | 62         |

|              | 6.3        | •                                                         | 65         |

|              | 6.4        | ,                                                         | 68         |

|              | 6.5        | ·                                                         | 75         |

|              | 6.6        | Case study 6: Workload correlations                       | 77         |

|              | 6.7        | Case study 7: Data dependencies                           | 81         |

|              | 6.8        | Overview                                                  | 83         |

| 7            | Con        |                                                           | 87         |

|              | 7.1        |                                                           | 87         |

|              | 7.2        | Outlook                                                   | 88         |

| $\mathbf{A}$ |            | extendible data format for the description of distributed |            |

|              |            |                                                           | 91         |

|              |            |                                                           | 91         |

|              |            | •                                                         | 91         |

|              | A.3        | Description of the data format - XML Schema               | 94         |

| В            |            |                                                           | 99         |

|              | <b>D</b> 1 | Sotup                                                     | $\Omega$ C |

|              | B.2  | Modeling                                       | . 99  |

|--------------|------|------------------------------------------------|-------|

|              | B.3  | Simulation                                     | . 102 |

| $\mathbf{C}$ | Cas  | e studies - System models                      | 105   |

|              | C.1  | Models case study 1: Pay burst only once       | . 106 |

|              | C.2  | Models case study 2: Cyclic dependencies       | . 111 |

|              | C.3  | Models case study 3: Variable Feedback         | . 116 |

|              | C.4  | Models case study 4: AND/OR task activation    | . 121 |

|              | C.5  | Models case study 5: Intra-context information | . 128 |

|              | C.6  | Models case study 6: Workload correlations     | . 133 |

|              | C.7  | Models case study 7: Data dependencies         | . 137 |

| D            | Tasl | k description (German)                         | 141   |

### Chapter 1

#### Introduction

#### 1.1 Motivation

One of the major challenges in the design process of distributed embedded systems is to estimate performance characteristics of the final system implementation in the early design stages. In particular, during a system-level design process a designer faces several questions related to the system performance: Do the timing properties of a certain architecture meet the design requirements? What is the on-chip memory demand? What are the different CPU and bus utilizations? Which resource acts as a bottleneck? These and other similar questions are generally hard to answer for embedded system architectures that are highly heterogeneous, parallel and distributed and thus inherently complex.

Nevertheless, accurate performance predictions are essential for several reasons. First of all they are crucial in the domain of hard real-time applications, where provable guarantees of system performance are indispensable. In addition, higher standards of usability are now increasingly being applied to soft real-time systems, as well. Further, performance analysis plays a fundamental role in the design process of embedded systems. In particular, performance analysis is necessary to drive the design space exploration: different implementation variants in terms of partitioning, allocation and binding can only be evaluated on the basis of reliable performance predictions. And finally, the high market pressure to maximize the performance and minimize the price of embedded systems no longer permits designers to overallocate system resources in order to compensate for vague performance predictions.

Several different approaches to the performance analysis of distributed embedded systems can be found in the literature. However, the various approaches are very heterogenous in terms of modeling scope, modeling effort, tool support, accuracy and scalability and there is a lack of literature on their classification and comparison. It is difficult for a designer to ascertain which performance

analysis methods can be applied to a certain system and in particular which method is most suitable for his individual needs.

In this thesis we address this problem by evaluating, classifying and comparing different performance analysis methods.

#### 1.2 Contributions

- We give an overview of approaches to the performance analysis of distributed embedded systems. We describe a number of concrete techniques that have been proposed so far and demonstrate their application.

- We discuss several criteria for the classification and comparison of performance analysis methods and evaluate a number of techniques with respect to these criteria. In particular we examine the modeling power, scalability and usability of various approaches.

- We then apply the different performance analysis methods to a number of benchmark systems defined by researchers of the ARTIST2 Network of Excellence on Embedded Systems Design<sup>1</sup>. We compare the results obtained in terms of accuracy and consider the required modeling and analysis effort. Further, we compare the hard performance bounds provided by formal analysis methods with worst-case estimations obtained by simulation.

- We present an extendible open-source library for performance simulation of distributed embedded systems based on SystemC, which we call PESIMDES. It is a repository of reusable modules that facilitates the system-level modeling and simulation of large distributed embedded systems using SystemC.

- We introduce a tool-independent and extendible data format for the description of distributed embedded systems and their performance analysis.

This format is a first step towards an automated combination of several performance analysis tools.

<sup>&</sup>lt;sup>1</sup>in the context of the ARTIST2 Workshop on Distributed Embedded Systems 2005 (http://www.lorentzcenter.nl/lc/web/2005/20051121/info.php3?wsid=177)

#### 1.3 Overview

- In Chapter 2 we lay the foundations for the work presented. In particular we describe the principal characteristics of distributed embedded systems and the relevant performance metrics. Moreover, we identify the requirements for performance analysis methods.

- Chapter 3 gives an overview of approaches to performance analysis and describes a number of concrete analysis methods.

- In Chapter 4 we present PESIMDES, an extendible open-source library for performance simulation of distributed embedded systems based on SystemC.

- In Chapter 5 we discuss several criteria for the classification and comparison of performance analysis methods. Further, we evaluate and compare the techniques presented in Chapter 3 with regard to these criteria.

- In Chapter 6 we provide a number of case studies on performance analysis. In particular, we apply the performance analysis methods described in Chapter 3 to several benchmark systems and compare the results.

- Chapter 7 contains conclusions and perspectives for the future.

#### 1.4 List of abbreviations

| CAN                                                            | Controller area network                                |  |

|----------------------------------------------------------------|--------------------------------------------------------|--|

| EDF                                                            | Earliest deadline first                                |  |

| FP                                                             | Fixed priority                                         |  |

| GPS                                                            | Generalized processor sharing                          |  |

| MAST                                                           | Modeling and Analysis Suite for Real-Time Applications |  |

| PESIMDES Performance Simulation of Distributed Embedded System |                                                        |  |

| RM                                                             | Rate monotonic                                         |  |

| SymTA/S                                                        | Symbolic Timing Analysis for Systems                   |  |

| TA                                                             | Timed automata                                         |  |

| TDMA                                                           | TDMA Time division multiple access                     |  |

| WCET                                                           | ET Worst case execution time                           |  |

| WCRT                                                           | Worst case response time                               |  |

Table 1.1: List of abbreviations used in this thesis

4 Chapter 1

# Performance analysis of distributed embedded systems

#### 2.1 Distributed embedded systems

Embedded systems are special purpose computing systems that are closely integrated into their environment. Typically, they are embedded into a larger product. In contrast to general purpose computing systems, embedded systems are dedicated to a specific application domain. This means that they execute only few applications, which are entirely known at design time. In particular, they are typically not programmable by the end user.

In general embedded systems must be efficient in terms of power consumption, size and cost. In addition, they usually have to be highly dependable, as a malfunction or breakdown of the device they control is not acceptable.

For many embedded systems not only the availability and the correctness of the computations is relevant, but also the timeliness of the computed results. Such systems with precise timing requirements are called real-time embedded systems. Their temporal behavior in terms of computation times, latencies and end-to-end delays is a functional system requirement. This means that a right answer arriving too late (or even too early) is wrong. Thus, real-time does not simply mean 'fast', but is a synonym for 'timely' and 'predictable'. In particular, real-time systems are called *hard*, if a missed deadline is not acceptable. All other embedded systems with timing constraints are called *soft*.

In most cases the timing constraints concern the reaction of the embedded system to events generated by the environment. In particular, embedded systems that must execute at a pace determined by the environment are called reactive systems. Examples are the control system of a nuclear power plant or the video processing system of a set-top box.

The embedding into a larger product and the constraints imposed by a

special application domain very often lead to distributed implementations. In particular physical, performance, safety and modularity constraints require distributed solutions. Distributed embedded systems consist of several hardware components that communicate via an interconnection network. Often the network is a shared resource that is contended for by several processing units. For instance the network can be a data bus that handles various data streams. Usually, the individual computing nodes are not synchronized and communicate via message passing. They have a high degree of independency and make autonomous decisions concerning resource access and scheduling. Therefore, it is a particularly complex task to maintain global state information.

In addition, in many cases each computing node has an individual functionality and a particular local environment. Thus, each node is provided with specific and adapted hardware resources, which leads to highly heterogeneous implementations. For instance in a car the embedded control units responsible for engine control, power train control and stability control have a highly heterogeneous composition.

Based on the above description, it becomes clear that heterogeneous and distributed embedded systems are inherently complex to design and analyze.

#### 2.2 Performance metrics

In [15] Marwedel indicates the following five metrics for the evaluation of the efficiency of an embedded system:

- Power consumption

- Code-size

- Run-time efficiency<sup>1</sup>

- Weight

- Cost

All these metrics can be subject to design requirements of the system. Therefore, in order to evaluate admissible system implementations and drive the state space exploration, appropriate predictions of these system characteristics are required in early design stages. Hence, in a broad sense, they can all be considered objectives of early performance analysis.

<sup>&</sup>lt;sup>1</sup>comprehends the amount of allocated hardware resources, clock frequencies and supply voltages

However, in most of the performance analysis methods for real-time embedded systems the focus is on the analysis of timing aspects. In particular, the designer is interested in best-case and worst-case delays, as he needs to know if the end-to-end latencies of the designed system meet the real-time requirements.

Further, in most embedded systems it is not acceptable that portions of a data stream are lost or retained due to buffer overflows. Therefore, it is essential for the designer to know if the allocated data buffers between the various computing nodes of the distributed system are large enough to contain the worst-case amount of data. In other words, he is interested in the worst-case buffer fill levels of the designed system.

On the basis of the above requirements, most of the performance analysis methods that can be found in the literature for real-time systems are targeted at one or both of the following performance metrics:

- End-to-end delays

- Memory requirements (in terms of buffer spaces)

### 2.3 Requirements for performance analysis methods

An ideal performance analysis method is accurate, fast and easy to use. There are, however, also other requirements that a performance analysis technique should fulfill. In this section we pick up and extend the list of requirements for performance analysis methods given in [25].

#### Correctness

A performance analysis approach should produce correct results. In the case of hard real-time embedded systems correct means that the determined results are hard upper (lower) bounds for the worst-case (best-case) performance of the system. In other words, there are no reachable system states such that the determined bounds are violated.

#### Accuracy

The calculated upper (lower) performance bounds should be close to the actual worst-case (best-case) performance of the system.

#### Analysis effort

The analysis of a distributed embedded system should be cheap in terms of analysis time and computational effort. This is particularly important if the performance analysis is used to drive a design space exploration. In this case the performance analysis is executed repeatedly in order to

evaluate several different system implementations and a short analysis time for a single evaluation is essential.

#### Modeling effort

A designer should be able to set up a system model for performance analysis with little effort. Also, an existing model should be easy to reconfigure, which is fundamental for design space exploration.

#### Reusability

An ideal performance analysis method should be reusable across different abstraction levels. This means that it should permit designers to model and analyze a system with different levels of detail. In particular, it should be easy to refine an existing system model.

#### Modularity

Performance analysis methods are not necessarily required to be modular (in the next chapter we will also consider holistic approaches), but modularity can have several advantages. For instance modular performance analysis methods are typically more scalable and easier to reconfigure than holistic approaches, because they permit designers to model and analyze a system by composing several smaller, ideally pre-built system modules. However, often the modularity is paid for by reduced analysis accuracy.

We would like to point out that the discussed requirements form a sort of "wish list" for attributes of performance analysis methods, i.e. they concern an ideal method. As we will show in the following chapters, none of the approaches considered satisfies all these requirements. In particular, different requirements may be conflicting for some performance analysis methods. For instance, a performance analysis method might be able to achieve more accurate results when performing a more time-consuming analysis.

Moreover, depending on the application domain and the design approach, the different requirements are usually not equally relevant.

# Approaches to performance analysis

There are several different approaches to analyzing or estimating the performance of distributed embedded systems. In this chapter we describe a number of methods for performance analysis that can be found in the literature. In particular we focus on system level performance analysis in early design stages.

#### 3.1 Classification

An important distinction is drawn between formal performance analysis methods and simulation based approaches. The former determine hard guarantees of the performance of a system, while the latter cannot usually provide hard performance bounds due to insufficient corner case coverage. There are also stochastic methods for performance analysis which we will not consider in the context of this thesis.

Further, one can distinguish modular and holistic performance analysis methods. The modular approaches analyze the performance of single components of the system and propagate the results in order to determine the performance of the entire system. In contrast, the holistic approaches consider the system as a whole. Holistic methods can generally provide more accurate results, as the behavior of the entire system is analyzed at once. However, this can also considerably increase the complexity of the analysis.

#### 3.2 Simulation based methods

The use of simulation for performance verification of distributed embedded systems is state of the art in industry. Several tools are available for cycle accurate hardware-software co-simulation; see e.g. [7, 31, 24]. In addition, the use of SystemC [19], a widespread platform for system-level modeling and simulation, is very common. Many simulation methods are trace-based, i.e. the

system designer provides traces of input stimuli that drive the simulation of the modeled system.

The main advantage of simulation is the large modeling scope. In contrast to formal analysis methods, basically every system can be modeled, as many dynamic and complex interactions can be taken into account for the simulation. Moreover, in most of the cases the functioning and performance of a system can be verified with the same simulation environment, simulation traces and benchmarks.

Another advantage of simulation based methods is that usually they are reusable over different abstraction levels, as the simulation models can be refined. In other words, the level of abstraction for the simulation can be adapted to the required degree of accuracy.

However, hardware-software co-simulations are often computationally complex and have long running times. Therefore, performance estimation quickly becomes a bottleneck in the design process, especially if it is used to drive a design space exploration.

The fundamental problem of simulation based performance analysis methods is the insufficient corner case coverage. Usually an exhaustive simulation of all the system states is not feasible due to the enormous state space. Thus, in order to determine the best-case or worst-case performance of a system through simulation, the system designer must provide use cases in the form of simulation traces that lead to the corresponding corner cases. However, this becomes practically impossible with increasing system complexity.

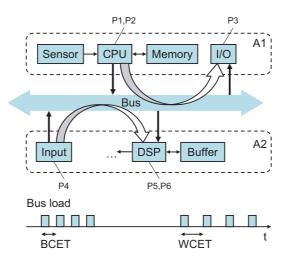

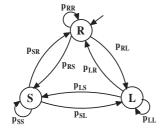

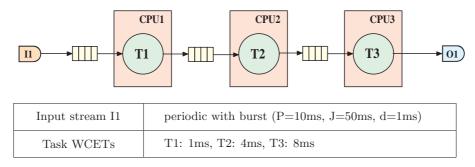

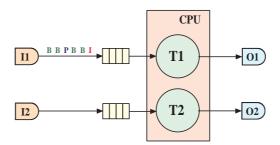

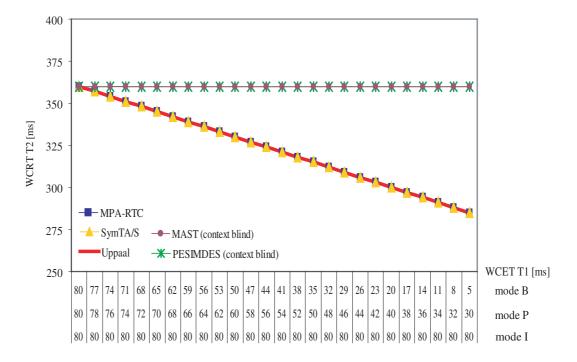

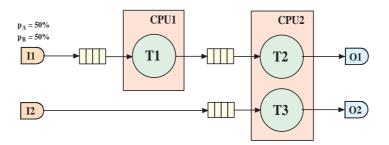

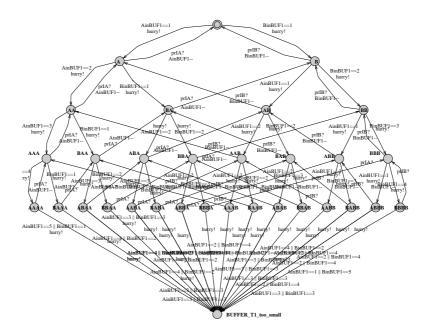

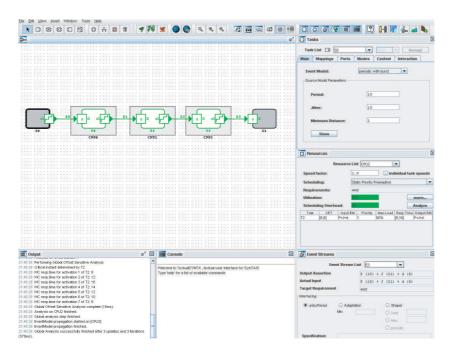

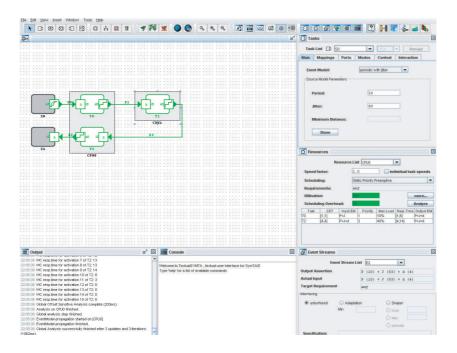

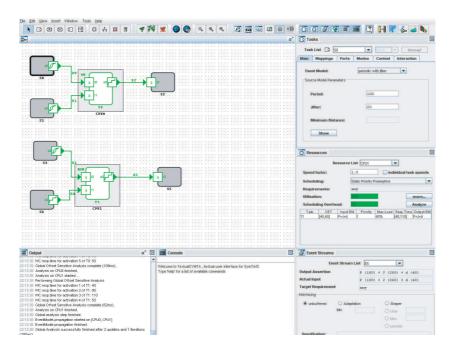

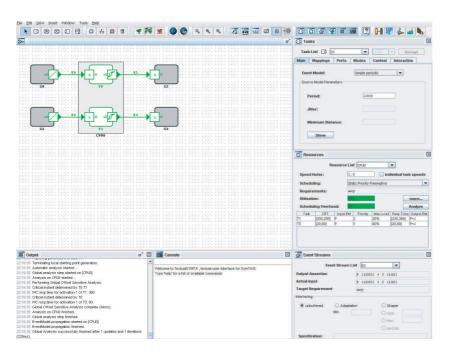

The following example adapted from [10] shows that finding simulation patterns that lead to corner cases is already challenging for apparently trivial distributed embedded systems. The system architecture is represented in Figure 3.1. In application A1 a task P1 of the CPU reads periodically data bursts from the sensor and stores the data in the memory. A second task P2 reads the data from the memory, processes it and transfers it to an output device via the shared bus. The task P2 has a best case execution time BCET and a worst case execution time WCET. We suppose that the CPU implements static fixed priority scheduling and that P1 has higher priority than P2. In the second application A2 a task P4 running on the input interface periodically sends data packets to the DSP over the shared bus. Task P5 on the DSP stores the data packets into the buffer. A second task P6 periodically removes data packets from the buffer, e.g. for playback. We suppose that the bus uses a first come first serve scheme for arbitration. As the two data streams of A1 and A2 interfere on the shared bus, there will be a jitter in the packet stream received

by the DSP that may lead to an underflow or overflow of the buffer.

Figure 3.1: Interference of two data streams on a shared communication resource

The interesting property of this system is that the DSP experiences the worst case input jitter when P2 executes continuously with its BCET. The reason is that in this case the distance between the packets of A1 on the bus is shortest and thus the transient bus load is highest. In other words, the worst case execution of A2 coincides with the best case execution of A1.

The designer must perceive this system particularity in order to provide a simulation trace that reaches the corner case. In case of larger and more realistic systems, several computation and communication resources will be shared simultaneously, there may be different scheduling policies for the various resources and data/control dependencies will play a role. In short, the corner cases will be extremely difficult to find.

Hence, simulation based methods are not suited to determining hard performance bounds of a general distributed embedded system. Nevertheless, simulative approaches can be useful to estimate the average system performance.

Moreover, it can be advantageous to combine simulation with formal performance analysis approaches: if the performance estimates provided by simulation are close to the results determined by an analytical method, it means that the calculated performance bound is accurate. In other words, simulation may be helpful to evaluate the accuracy of formal performance analysis. However, note that if the simulation and analysis results are distant, no conclusion about the accuracy is possible: either a too pessimistic performance analysis or a too optimistic performance simulation can be the cause.

#### 3.3 Holistic scheduling

There is a large body of literature on scheduling of tasks on shared computing resources. In particular, in the real-time domain the research is focused on the analysis of schedulability and worst case response times of tasks. Examples of scheduling algorithms are fixed priority, rate monotonic, earliest deadline first, round robin and TDMA. Detailed information about the various scheduling policies and the corresponding analyses can be found in [5], as well as in many other books on the topic.

Several proposals have been made to extend concepts of the classical scheduling theory to distributed systems. In such systems the applications are executed on several computing nodes and the delays caused by the shared use of communication resources cannot be neglected. In particular the integration of process and communication scheduling is often denoted as holistic scheduling. Rather than a specific performance analysis method, holistic scheduling is a group of techniques for the analysis of distributed embedded systems.

Each analysis technique is focused on a particular input event model and resource sharing policy. This permits a detailed analysis of the temporal behavior of a system and leads to accurate performance predictions. Nevertheless, the modeling scope of the analysis techniques is restricted to a particular class of systems, i.e. the holistic approaches do not scale to general distributed architectures. For every new kind of input event model, communication protocol, resource sharing policy and combinations thereof, a new analysis method needs to be developed.

A number of holistic analysis techniques can be found in the literature. For instance in [27] Tindell and Clark combine fixed priority scheduling on the processing resources of a distributed system with TDMA scheduling on communication resources. In [22] Pop, Eles and Peng analyze mixed event triggered and time triggered task sets that communicate over protocols with both static and dynamic phases (e.g. FlexRay).

In this section we briefly describe the holistic analysis approach presented by Tindell and Clark as well as improvements of the analysis for systems with data dependencies (Yen, Wolf) and control dependencies (Pop, Eles, Peng). Moreover, we describe the MAST tool (Gonzalez Harbour *et al.*), an analysis suite that implements several holistic techniques.

#### 3.3.1 Schedulability analysis for distributed systems

In [27] Tindell and Clark propose an extension of the static priority preemptive scheduling analysis to address the wider problem of scheduling analysis for distributed systems. In particular, they derive an analysis for systems in which tasks with arbitrary deadlines communicate via message passing over a communication network implementing the TDMA protocol.

The starting point is the equation to compute the worst-case response time of a given task i on a shared processor, assuming periodic task activations and static priority preemptive scheduling [13, 11]:

$$r_i = C_i + \sum_{\forall j \in hp(i)} \left\lceil \frac{r_i}{T_j} \right\rceil C_j \tag{3.1}$$

where  $r_i$  is the worst-case response time of a given task i, hp(i) is the set of all tasks of higher priority than task i,  $C_i$  ist the worst-case execution time of task i and  $T_j$  is the period of task j. This equation is valid under the assumption that the deadline of a task i is less than its period  $T_i$  and can be solved by iteration (a suitable initial value for  $r_i$  is 0).

Tindell and Clark contribute to two extensions of the above analysis:

- 1. They extend the analysis to the case with arbitrary deadlines

- 2. They take into account the release jitter  $J_i$  of processes, i.e. the worst-case time between the arrival of a process and its release

The resulting analysis of the worst-case response time of a task i is given by the following equations:

$$r_i = \max_{q=0,1,2,\dots} (J_i + w_i(q) - qT_i)$$

(3.2)

$$w_i(q) = (q+1)C_i + \sum_{\forall i \in hp(i)} \left\lceil \frac{J_i + w_i(q)}{T_j} \right\rceil C_j$$

(3.3)

The sequence of values of q in the first equation is finite since only values of q where  $w_i(q) > (q+1)T_i$  need to be considered.

The major achievement of Tindell and Clark is the adaptation of the above processor schedulability analysis to a communication system. In particular, they apply the same family of analysis to the bounding of message delays across a TDMA broadcast bus. For the sake of conciseness, we do not report the corresponding equations and refer the reader to [27].

Finally, Tindell and Clark integrate the analysis of the worst-case timing of tasks with the analysis of the worst-case timing of messages. The basic concept is to interpret the message delay induced by the communication system as release jitter of the receiver task. The result is a holistic analysis method for distributed systems.

However, the holistic scheduling equations cannot usually be trivially solved due to mutual dependencies. For instance the release jitter of a receiver task depends on the arrival time of the corresponding message, which in turn depends on the interference from higher priority messages, which in turn depends on the release jitter of sender tasks.

This example points out an important property that holds for most of the holistic analysis methods: in general the complexity of the model grows with the size of the system.

#### 3.3.2 Performance analysis for systems with data dependencies

In [32] Yen and Wolf introduce an analysis algorithm for the execution time of an application on a distributed system. In particular they extend the classical analysis for static priority preemptive scheduling (equation 3.1) in order to exploit data dependencies that exist among the tasks of a task graph. This permits to determine tighter performance bounds. Basically, the extended analysis takes into account that the delays through a path of tasks forming a task graph are not independent.

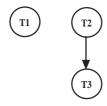

The example of Figure 3.2 adopted from [32] illustrates the effects of data dependencies on the execution delay<sup>1</sup>: if the data dependency between T2 and T3 is ignored, their worst-case response times are  $35 \, ms$  and  $45 \, ms$ , respectively. Thus, the classical analysis assumes a worst-case delay of  $80 \, ms$  for the execution of the task sequence T2-T3. However, the worst-case delay for this task sequence is actually  $45 \, ms$ , because

- 1. T1 can only preempt either T2 or T3, but not both in a single execution

- 2. T2 cannot preempt T3

as can be easily traced considering the periods and WCETs of the system specification.

To detect and exploit properties like the first one in the above example, Yen and Wolf introduce the concept of *phases* among task activations and extend

<sup>&</sup>lt;sup>1</sup>The example is considered also in Section 6.7 where a more detailed analysis can be found

| Task | Period | WCET | Priority |

|------|--------|------|----------|

| T1   | 80     | 15   | high     |

| T2   | 50     | 20   | medium   |

| Т3   | 50     | 10   | low      |

Figure 3.2: Effect of data dependencies on the execution delay. The three tasks form two task graphs and share the same CPU which implements preemptive fixed priority scheduling.

the analysis of equation 3.1 as follows<sup>2</sup>:

$$r_i = C_i + \sum_{\forall j \in hp(i)} \left\lceil \frac{r_i - \phi_{ij}}{T_j} \right\rceil C_j$$

(3.4)

where the phase  $\phi_{ij}$  is the smallest interval for the next activation of a preempting task j relative to the activation of a task i. In particular the phases among the tasks are computed iteratively by a fixed point iteration: starting with initial phase values the response time analysis is used to derive better phase values which in turn allow a more accurate response time analysis etc.

To handle conditions like the second one in the above example, Yen and Wolf introduce a so called separation analysis that allows to verify whether the executions of two tasks can overlap or not.

For the sake of conciseness we do not report the two algorithms to compute the phases and separations of tasks and refer the interested reader to [32].

# 3.3.3 Performance analysis for systems with control dependencies

In [21] Pop, Eles and Peng present an extension of the previous analysis that takes into account the control dependencies among the tasks of an application. In systems with control dependencies, depending on conditions, only a subset of the tasks is executed during a system invocation. As for data dependencies, the consideration of control dependencies can significantly reduce the pessimism of the performance analysis.

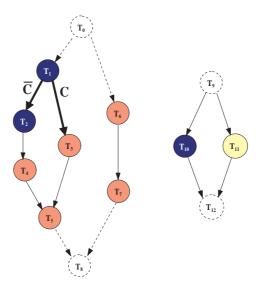

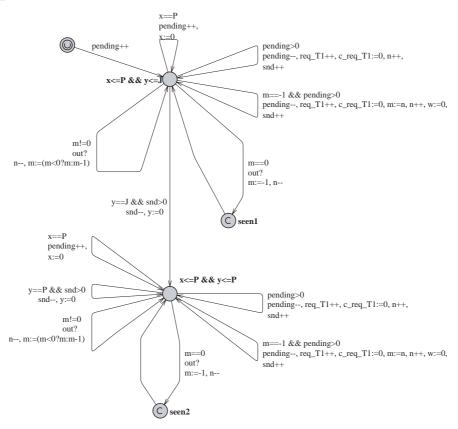

In particular, in [21] the authors introduce so-called conditional process graphs (CPG) as models for applications and analyze their delay. Figure 3.3 shows an example of a system model consisting of two CPGs.

Three approaches are proposed to analyze the delay of a CPG:

<sup>&</sup>lt;sup>2</sup>In [26] Tindell presents a similar concept of time offsets to exploit data dependencies

Figure 3.3: Example of system model consisting of two CPGs. The execution of T2/T4 and T3 depends on the condition C determined by T1. The tasks are mapped on three different processors as indicated by the shading.

#### Brute force solution

The CPG is decomposed into all its constituent unconditional subgraphs and each of these subgraphs is analyzed as presented in the previous section. This approach provides a tight bound on the delay, but can be very expensive in terms of analysis effort, as in general the number of unconditional subgraphs can grow exponentially with the number of tasks.

#### Condition separation

The knowledge about the conditions is used only in order to refine the separation analysis of the previous section. This analysis is more pessimistic than the brute force solution, however it reduces the analysis effort significantly.

#### Relaxed tightness analysis

This approach is similar to the brute force solution, as the same number of unconditional subgraphs must be analyzed. However, the analysis effort is reduced significantly by the substitution of the original analysis algorithms with less complex approximation variants. Of course, this simplification is paid for by reduced analysis accuracy.

For the corresponding analysis algorithms we refer the reader to [21].

# 3.3.4 The Modeling and Analysis Suite for Real-Time Applications (MAST)

An important contribution to enhance, implement and aggregate several scheduling analysis techniques has been made by the research group of Gonzalez Harbour at the University of Cantabria. This group has realized the MAST suite<sup>3</sup>[14], an open source set of software tools for the schedulability analysis of real-time applications. It aggregates several scheduling analysis techniques for mono-processor and distributed systems. In particular the MAST tool

- implements offset-based scheduling analysis techniques

- can model complex dependence patterns among the tasks of an application (for instance multiple event task activation)

- supports hierarchical scheduling

- supports several input event models (for instance periodic, sporadic, or bursty event streams)

- can compute optimal priority assignments to tasks

- can compute priority ceilings and preemption levels for shared resources

- can analyze the resource load and compute several slack values

For the evaluation of performance analysis methods conducted in the next chapters we will use the MAST tool as representative of holistic performance analysis methods.

# 3.4 Compositional scheduling analysis using standard event models

In [23, 10] Richter *et al.* propose a modular performance analysis approach for distributed embedded systems based on the results of classical real-time scheduling. The approach is denominated SymTA/S, which stands for Symbolic Timing Analysis for Systems.<sup>4</sup>

$<sup>^3</sup>http://mast.unican.es/$

$<sup>^4</sup>$ The SymTA/S approach is fully implemented in a software tool distributed under the same name. In this thesis we will use the term SymTA/S for both the analysis approach itself and the corresponding tool.

In the following subsections we first report a number of well known abstractions for event arrival patterns on which the SymTA/S analysis is based. Then, we briefly describe the analysis approach itself and some recent extensions.

#### 3.4.1 Standard event models

The behavior of the environment of a distributed embedded system is often modeled using common abstractions for event arrival patterns. These abstractions include periodic or sporadic event arrivals with potential jitters or bursts. In the context of SymTA/S these models are denoted as standard event models.

#### Periodic event stream

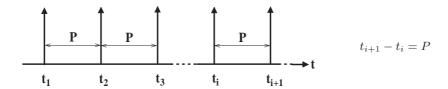

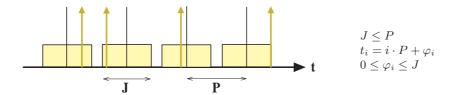

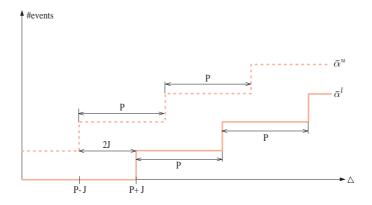

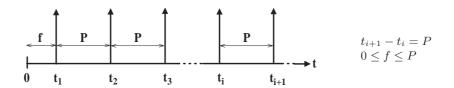

In a periodic event stream with period P the events arrive at intervals of exactly P time units. Figure 3.4 depicts a periodic arrival pattern.

Figure 3.4: Periodic event stream

#### Periodic event stream with jitter

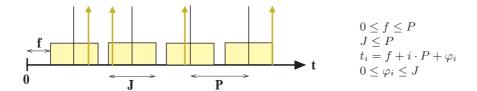

In the periodic event stream model with jitter the events arrive at an average time interval of P time units, but may have a local deviation around the ideal periodic arrival. The deviation is bounded by an interval of length  $J \leq P$ . This is represented in Figure 3.5, where the intervals of admissible arrival times are represented as shaded rectangles.

Figure 3.5: Periodic event stream with jitter. In each jitter interval (shaded rectangle) exactly one event arrives.

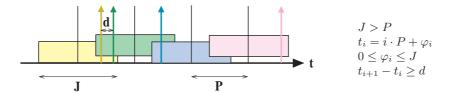

#### Periodic event stream with burst

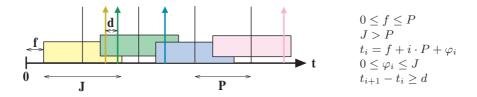

Events may arrive in bursts, if the deviation from the ideal periodic arrival time is larger than the period. In this case the admissible arrival time intervals of adjacent periods overlap, as depicted in Figure 3.6. However, events cannot overtake each other: the arrival time of an event is restricted by the arrival time of previous events. In particular an event may arrive only d time units  $(d = minimum event inter-arrival time, d \ge 0)$  after the arrival of the event belonging to the previous period.

Figure 3.6: Periodic event stream with burst

The standard event models also include the sporadic variants of the three models described above. Basically they are identical to the periodic variants with the difference that single event arrivals may be left out.

#### 3.4.2 The SymTA/S analysis approach

The main goal of the SymTA/S analysis approach is to exploit the host of work on mono-processor real-time scheduling analysis for the performance analysis of distributed embedded systems. While holistic methods attempt to extend classical scheduling analysis to special classes of distributed systems, SymTA/S applies existing analysis techniques in a modular manner: the single modules of a distributed system are analyzed with classical algorithms and the local results are propagated among the system through appropriate interfaces.

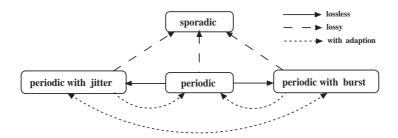

The advantage of this approach is that it does not require the development of new scheduling analysis algorithms. However, all the event streams in the system must fit the basic models for which scheduling analysis techniques are available. In particular, the output event stream of a component must be converted to an event stream model that is compatible with the scheduling analysis performed on the next component. SymTA/S provides interfaces to convert standard event stream models among each other. These interfaces can be grouped into two types:

#### Event Model Interfaces (EMIFs)

Event Model Interfaces do not change the actual timing properties of an

event stream. Only the mathematical representation of the stream, i.e. the underlying model is converted. Such transformations require that the parameters of the target model encompass the timing of any possible event sequence in the source model.

#### Event Adaptation Functions (EAFs)

Event Adaptation Functions need to be used in cases where an EMIF transformation is not possible. In this case the timing properties of the stream must be adapted to fit the requested model. In particular this requires to change the implementation of the system, e.g. by adding appropriate event buffers.

For instance it is possible to convert a periodic event stream with jitter X to a sporadic event stream Y by a simple EMIF: If X is characterized by a period  $P_X$  and a jitter  $J_X$  and Y is characterized by a minimum interarrival time  $t_Y$ , the corresponding EMIF is represented by the equation  $t_Y = P_X - J_X$ . However, this transformation comports a loss of information, as the stream Y also comprehends event sequences that cannot occur according to the event stream model X.

An example of an interface that requires an EAF is the conversion of a periodic event stream with burst to a pure periodic event stream. In particular it is necessary to add an appropriate buffer to smooth out the bursts.

Figure 3.7 gives an overview of the event model interfaces adopted by SymTA/S.

Figure 3.7: Event model interfaces in SymTA/S

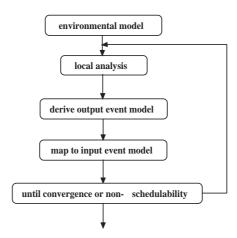

The event stream interface technology described above permits to analyze the performance of a distributed embedded system by applying classical scheduling analysis algorithms to local components. Figure 3.8 illustrates the overall analysis principle. First the environmental timing assertions are applied to components connected to the system inputs. Then, these components are analyzed to derive local delays and buffer requirements, as well as the corresponding output event models. These output event models are mapped to the input event

models of the connected components using appropriate EMIFs or EAFs. In pure feed-forward systems this procedure is simply repeated for all the components until the event streams are propagated through the whole system and global end-to-end delays and buffer sizes can be determined.

Figure 3.8: Analysis principle of SymTA/S

For systems with functional cycles (i.e. systems with feedback) or systems with non-functional cyclic dependencies the timing of two or more components is mutually dependent. In this case the event streams are propagated iteratively until the event stream parameters converge or the tasks of a resource are no longer schedulable.

#### 3.4.3 Extensions

Several extensions have been worked out for the analysis approach described above. For instance the SymTA/S analysis approach can deal with multiple task activation. This means that the tasks of a system can be triggered by multiple inputs in AND- or OR-combination. Moreover, the approach is able to take into account system context information in order to reduce analysis pessimism. In particular, the analysis methods support the exploitation of two kinds of context information:

#### Intra-event stream context

This kind of context information considers the correlations between successive computation or communication requests in an event stream. In particular, the events of a stream can have different types and impose different workloads on the activated tasks according to their type. Correlations within a sequence of different activating events can be described by means of appropriate intra-context information. This information can ei-

ther describe exactly the sequence of activation events (e.g. by specifying a periodically recurring pattern of event types) or be partially incomplete (e.g. by specifying minimum and maximum number of occurrences for a certain event type in an event sequence of a given length).

#### Inter-event stream context

This kind of context information considers timing correlations between events in different event streams. In particular, while context-blind analysis assumes that all tasks sharing a resource are independent and can all be activated simultaneously, this might not be possible due to timing correlations among event streams. For instance, such correlations may result from data dependencies (see Section 3.3.2) and can be expressed by appropriate activation offsets.

More detailed information about the various extensions to the SymTA/S performance analysis approach can be found in [10].

# 3.5 Modular Performance Analysis with Real Time Calculus

Modular Performance Analysis with Real Time Calculus (MPA-RTC) [6] is a framework for performance analysis of distributed embedded systems that has its roots in network calculus [4], a theory of deterministic queuing systems for communication networks. MPA-RTC analyzes the flow of event streams through a network of computation and communication resources in order to derive performance characteristics of a distributed embedded system.

MPA-RTC is a modular approach to performance analysis. It permits to analyze large systems by composing basic analysis components to performance models. In contrast to the SymTA/S approach, MPA-RTC is not restricted to a few classes of input event models. In particular it permits to model any event stream using so-called arrival curves. A similar abstraction, the so-called service curves, is used to model the availability of computation or communication resources. Service curves are first-class citizen in the MPA-RTC approach and permit to model basically any form of resource availability. This differentiates MPA-RTC from other performance analysis methods, that are usually restricted to a few common models of resource availability.

In the following subsections we first describe the concepts of arrival and service curves (denoted together as variability characterization curves) on which MPA-RTC is based. Subsequently, we describe the analysis approach itself and some recent extensions.

#### 3.5.1 Variability characterization curves

In MPA-RTC the timing characterization of event and resource streams is based on variability characterization curves which basically generalize the classical representations such as sporadic, periodic or periodic with jitter.

Event streams are described using arrival curves  $\bar{\alpha}^u(\Delta)$ ,  $\bar{\alpha}^l(\Delta) \in \mathbb{R}^{\geq 0}$ ,  $\Delta \in \mathbb{R}^{\geq 0}$  which provide upper and lower bounds on the number of events in any time interval of length  $\Delta$ . In particular, if R[s,t) denotes the number of events that arrive in the time interval [s,t), then the following inequality is satisfied:

$$\bar{\alpha}^l(t-s) \le R[s,t) \le \bar{\alpha}^u(t-s) \quad \forall s < t$$

(3.5)

where  $\bar{\alpha}^l(0) = \bar{\alpha}^u(0) = 0$ . The timing information of the standard event models can easily be represented by appropriate pairs of upper and lower arrival curves [6]. For instance Figure 3.9 depicts the upper and lower arrival curves of the class of event streams with period P and jitter J.

Figure 3.9: The upper and lower arrival curves of an event stream with period P and jitter  ${\bf J}$

The arrival curves are much more general than the standard event models: any deterministic event stream can be modeled by an appropriate pair of arrival curves. The curves can be constructed analytically, if the event stream pattern is completely defined. Alternatively they can be derived from a finite set of event traces. This can be done easily by using a sliding window of size  $\Delta$  and determining the minimum and maximum number of events within the window.

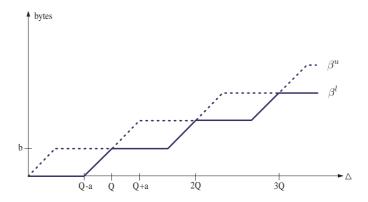

In a similar way, resource streams are described using service curves  $\beta^u(\Delta)$ ,  $\beta^l(\Delta) \in \mathbb{R}^{\geq 0}$ ,  $\Delta \in \mathbb{R}^{\geq 0}$  which provide upper and lower bounds on the available service in any time interval of length  $\Delta$ . The service is expressed in an appropriate unit, for instance number of cycles for computing resources or bytes for communication resources. In particular, if C[s,t) denotes the number of

processing or communication units available from the resource over the time interval [s,t), then the following inequality holds:

$$\beta^{l}(t-s) \le C[s,t) \le \beta^{u}(t-s) \quad \forall s < t \tag{3.6}$$

Again, there are no restrictions for the representable resource models. With an appropriate pair of service curves, any deterministic resource availability can be modeled. For instance Figure 3.10 depicts the upper and lower service curves for a slot of a time units that permits the transmission of b bytes on a TDMA resource with period Q. Moreover, service curves enable the modeling of hierarchical scheduling.

Figure 3.10: The upper and lower service curves for a slot on a TDMA resource

Note that in the above definitions  $\bar{\alpha}^l(\Delta)$  and  $\bar{\alpha}^u(\Delta)$  are expressed in terms of events (this is marked by a bar on the  $\alpha$ ), while  $\beta^l(\Delta)$  and  $\beta^u(\Delta)$  are expressed in terms of workload/service units. However, the analysis described in the next subsection requires the arrival and service curves to be expressed in the same unit. The transformation of event-based curves into workload/resource-based curves and vice versa is done by means of so called workload curves. Basically these define the minimum and maximum workload imposed on a resource by a given number of succeeding events, i.e. they capture the variability in execution demands. The interested reader can find more information about workload curves in [16].

#### 3.5.2 Analysis and resource sharing

In this subsection we describe how MPA-RTC models the processing of event streams by computation and communication resources. In particular we describe how the outgoing event and resource streams of a processing component are derived from the ingoing event and resource streams.

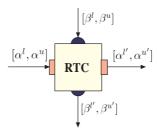

Figure 3.11 shows a so called Real Time Calculus abstract processing component that models the processing of an event stream by an application process. In particular, an incoming event stream represented as a pair of arrival curves  $\alpha^l$  and  $\alpha^u$ , flows into a FIFO buffer in front of the processing component. The component is triggered by these events and will process them in a greedy manner while being restricted by the availability of resources, which are represented by a pair of service curves  $\beta^l$  and  $\beta^u$ . On its output, the component generates an outgoing stream of processed events, represented by a pair of arrival curves  $\alpha^{l'}$  and  $\alpha^{u'}$ . Resources left over by the component are made available again on the resource output and are represented by a pair of service curves  $\beta^{l'}$  and  $\beta^{u'}$ .

Figure 3.11: Real Time Calculus processing component

The transformation of input arrival and service curves to output arrival and service curves is described by the following set of equations:

$$\alpha^{l'}(\Delta) = \min \left\{ \inf_{0 \le \mu \le \Delta} \left\{ \sup_{\lambda \ge 0} \left\{ \alpha^{l}(\mu + \lambda) - \beta^{u}(\lambda) \right\} + \beta^{l}(\Delta - \mu) \right\}, \beta^{l}(\Delta) \right\}$$

(3.7)

$$\alpha^{u'}(\Delta) = \min \left\{ \sup_{\lambda \geq 0} \left\{ \inf_{0 \leq \mu < \lambda + \Delta} \left\{ \alpha^{u}(\mu) + \beta^{u}(\lambda + \Delta - \mu) \right\} - \beta^{l}(\lambda) \right\}, \beta^{u}(\Delta) \right\}$$

(3.8)

$$\beta^{l'}(\Delta) = \sup_{0 \leq \lambda \leq \Delta} \left\{ \min \left\{ \inf_{0 \leq \mu \leq \Delta} \left\{ \sup_{\lambda \geq 0} - \alpha^{u}(\lambda) \right\} \right\}$$

(3.9)

$$\beta^{u'}(\Delta) = \max \left\{ \inf_{\lambda \geq \Delta} \left\{ \beta^{u}(\lambda) - \alpha^{l}(\lambda) \right\}, 0 \right\}$$

(3.10)

$$\beta^{l'}(\Delta) = \sup_{0 < \lambda < \Delta} \left\{ \min \left\{ \inf_{0 \le \mu \le \Delta} \left\{ \sup_{\lambda > 0} -\alpha^{u}(\lambda) \right\} \right\} \right. \tag{3.9}$$

$$\beta^{u'}(\Delta) = \max\{\inf_{\lambda > \Delta} \{\beta^{u}(\lambda) - \alpha^{l}(\lambda)\}, 0\}$$

(3.10)

The processing components can be freely combined to form performance models of distributed embedded systems. For instance in order to model the sequential processing of an event stream by two tasks, it is sufficient to connect two processing components in series so that the outgoing event stream of the first one is the ingoing event stream of the second one.

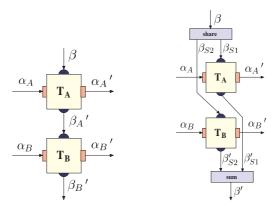

Scheduling policies on shared resources can be modeled by the way processing components are linked and resource streams are distributed among them. For instance Figure 3.12(a) shows how to connect two performance components in order to model a resource that implements preemptive fixed priority scheduling: the task  $T_B$  has lower priority than  $T_A$  and thus gets only the resource service that is left after  $T_A$  has been served. Figure 3.12(b) shows the modeling of a proportional share policy. Many other scheduling strategies as for instance FCFS, TDMA or EDF can be modeled by distributing resource streams properly.

Figure 3.12: Real Time Calculus models for Fixed Priority and Proportional Share scheduling

The performance analysis of a distributed embedded system is done by combining the analysis of the single processing components of a performance model. In particular, the maximum delay experienced by an event at a system module and the maximum number of events that are waiting to be processed can be bounded by the following inequalities:

$$delay \leq \sup_{t>0} \left\{ \inf \left\{ \tau \geq 0 : \alpha^{u}(t) \leq \beta^{l}(t+\tau) \right\} \right\}$$

(3.11)

$$delay \leq \sup_{t\geq 0} \left\{ \inf \left\{ \tau \geq 0 : \alpha^{u}(t) \leq \beta^{l}(t+\tau) \right\} \right\}$$

$$backlog \leq \sup_{t\geq 0} \left\{ \alpha^{u}(t) - \beta^{l}(t) \right\}$$

$$(3.11)$$

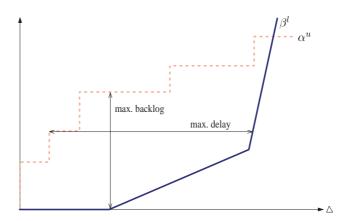

The maximum delay and backlog experienced at a processing component correspond to the maximal horizontal and vertical distance between  $\alpha^u$  and  $\beta^l$ , respectively, as depicted in Figure 3.13.

The end-to-end delay experienced by an event at the complete system is computed as the sum of the single delays at the various processing components. However, the analysis does not necessarily need to be strictly modular. For instance a holistic delay analysis that considers the combined action of several processing components in series is also feasible.

Figure 3.13: Graphical interpretation of maximum delay and backlog

### 3.5.3 Extensions

Several extensions have been worked out to refine the MPA-RTC analysis approach. The following list cites three examples:

- [28] proposes an abstract stream model for the characterization of streams with different event types that impose different workloads on the system. It permits considerable improvements of the worst-case performance analysis for systems with type related workload.

- [29] presents abstract models for system components, which permit to capture complex functional properties of systems, as for example caches, variable resource demands and arbitrary up- and down-sampling of event streams in a system component.

- [30] introduces a model to characterize and capture the correlation of different resource demands that events of a given type cause on different system components. The exploitation of such so-called workload correlations can lead to considerably improved analysis results (see case study in Section 6.6).

Finally, we would like to point out that the described modular performance analysis framework is not necessarily bound to the use of Real Time Calculus. Instead, any abstraction of event streams and resource characterization can be used. It is sufficient to change the computations that are done within the processing components appropriately.

### 3.6 Timed automata based performance analysis

The use of formal methods for the design and analysis of real-time systems has driven research for many years. Several different formal approaches can be used to specify a system and verify its correctness. [8] gives an overview of available formalisms for the design and analysis of real-time computing systems.

Timed automata [1] are one popular formalism for the specification of realtime systems. They can be used in combination with a logic language to verify system properties by model checking. In particular the UPPAAL tool environment<sup>5</sup> [3] allows users to validate and verify real-time systems modeled as networks of timed automata.

In [17] Yi et al. have shown that the schedulability analysis of an event-driven system can be represented as a reachability problem for timed automata and thus can be tackled with model checking. In particular, timed automata based schedulability analysis is implemented in the TIMES tool<sup>6</sup> [2]. TIMES permits users to analyze systems that are described as a set of tasks which are triggered either periodically or by external event streams modeled through appropriate timed automata. However, the TIMES tool is limited to the schedulability analysis of single processors. Thus, it is not suited for performance analysis of distributed systems.

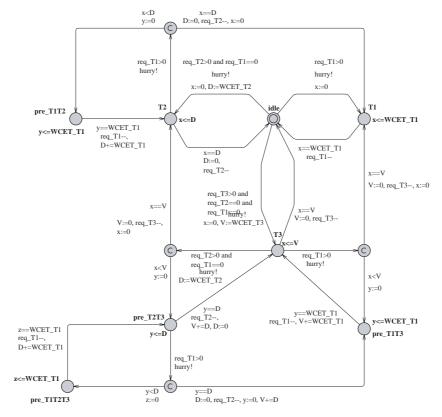

Recently Hendriks and Verhoef have presented an approach to performance analysis of distributed embedded systems based on the model checking of timed automata networks [9]. In this section we briefly describe the fundamental concept and the application of their approach.

Basically, the idea is to model the environment and the resources of a system as timed automata. The various components are then composed into a network of timed automata that models a distributed embedded system. The performance properties of the system are verified through exhaustive model checking. In particular, UPPAAL is used for the modeling and verification of timed automata networks.

In the following subsections we describe some timed automata models for input event streams and hardware resources that have been proposed so far in the context of this analysis approach. Afterwards we show how the different components can be aggregated to model a distributed embedded system and how the performance analysis is realized. We would like to point out that the analysis approach is not restricted to the component models described. In

<sup>&</sup>lt;sup>5</sup>available at http://www.uppaal.com

<sup>&</sup>lt;sup>6</sup>available at http://www.timestool.com

particular, new timed automata models for other types of event streams and resource sharing policies can be designed, making extensibility one of the major benefits of this approach.

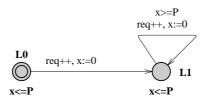

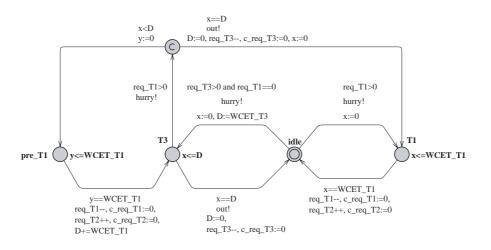

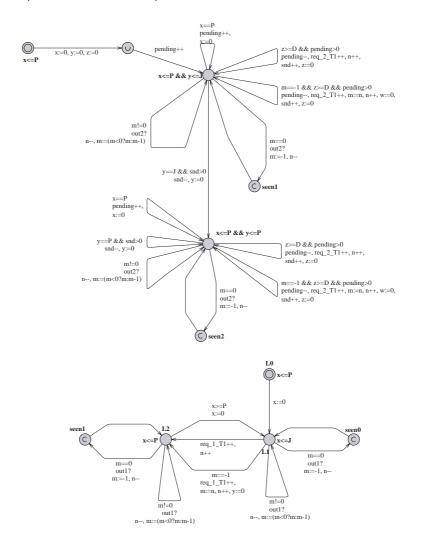

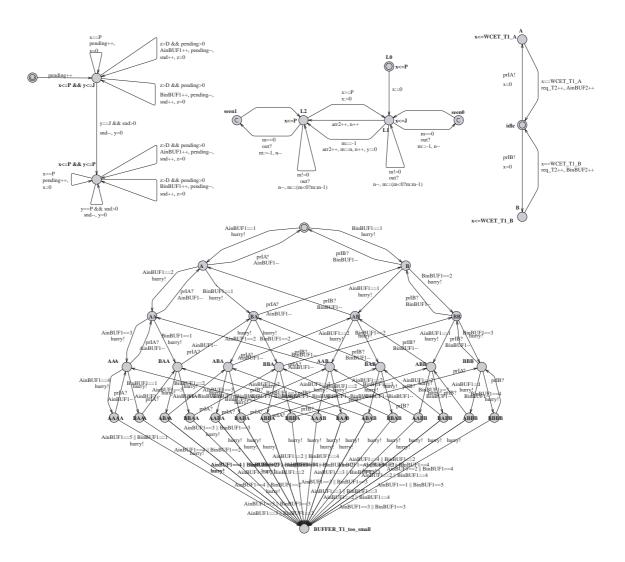

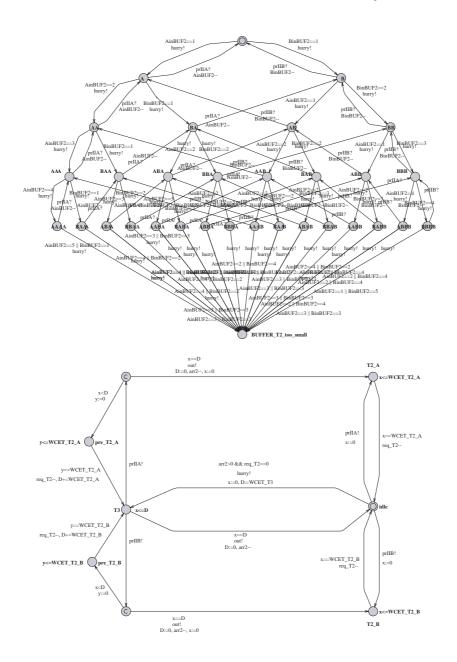

### 3.6.1 Modeling the environment

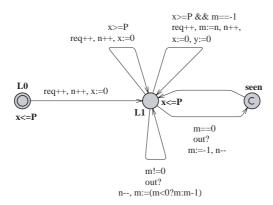

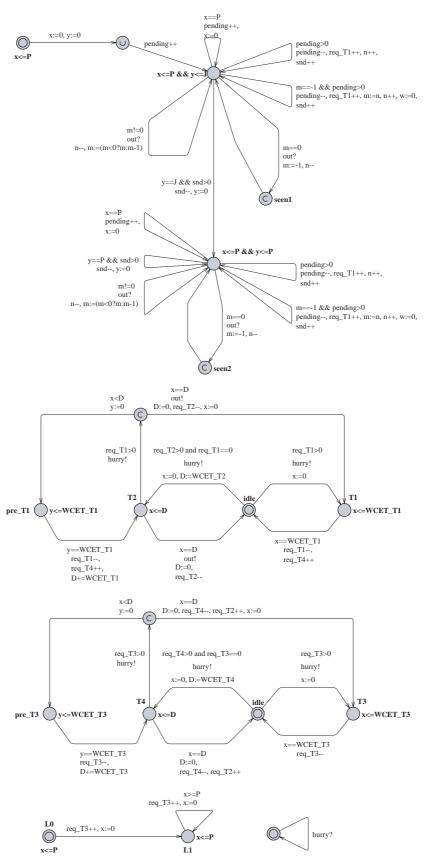

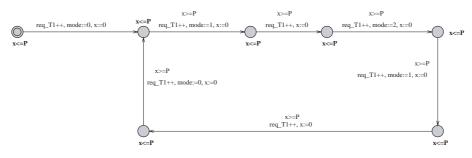

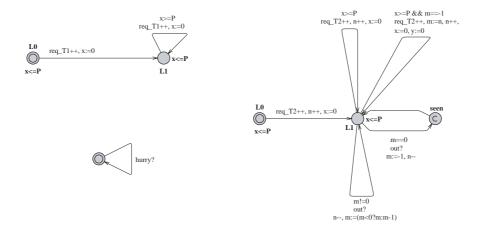

Several timed automata models have been proposed to represent different input event streams. In particular, for all the standard event models (see Section 3.4.1) corresponding timed automata templates have been designed. For instance Figure 3.14 shows a timed automaton that models a periodic event stream with period P. After an undefined initial offset the automaton generates events at intervals of exactly P time units. The generation of an event is modeled by the increment of the global variable req. Figure 3.15 depicts a timed automaton presented in [20] that models a periodic event stream with jitter  $J \leq P$ .

Figure 3.14: Timed automata model for a periodic event stream

Figure 3.15: Timed automata model for a periodic event stream with jitter

The automaton for a periodic event stream with burst can be found in [9]. As we stated above, new event stream models can be designed easily. Basically any deterministic event stream can be modeled.

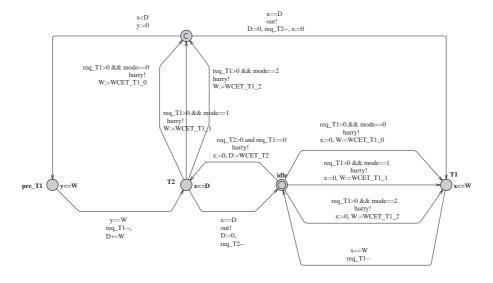

### 3.6.2 Modeling the hardware resources

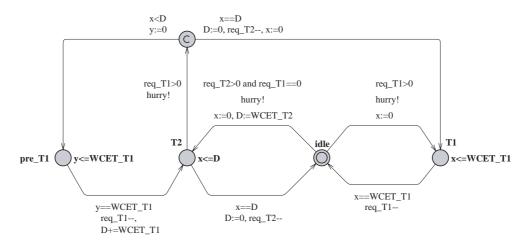

Each processing component is modeled as a separate timed automaton. A processing component is either idle or busy computing some function. Similarly, each communication link is modeled as a timed automaton. Each link is either idle or transporting some data. For shared resources the adopted scheduling

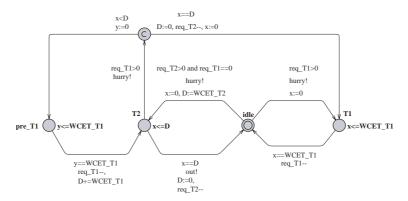

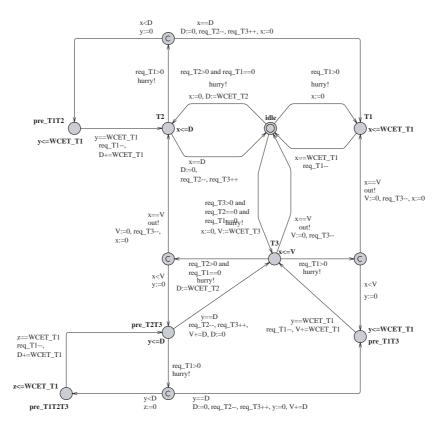

policy determines the structure of the model. For instance Figure 3.16 shows a timed automaton that models a hardware resource with two tasks implementing preemptive fixed priority scheduling. The resource can either be idle or process T1 or process T2. The location  $pre\_T1$  models the fact that T1 can preempt T2. The hurry! synchronization models a so-called urgent edge (see [3] for details) and makes sure that the corresponding edge is taken as soon as it is enabled.

Figure 3.16: Timed automata model for a preemptive FP resource with two tasks

Several other resource sharing strategies can be modeled with appropriate timed automata. For instance in [20] we have presented a solution for a TDMA policy.

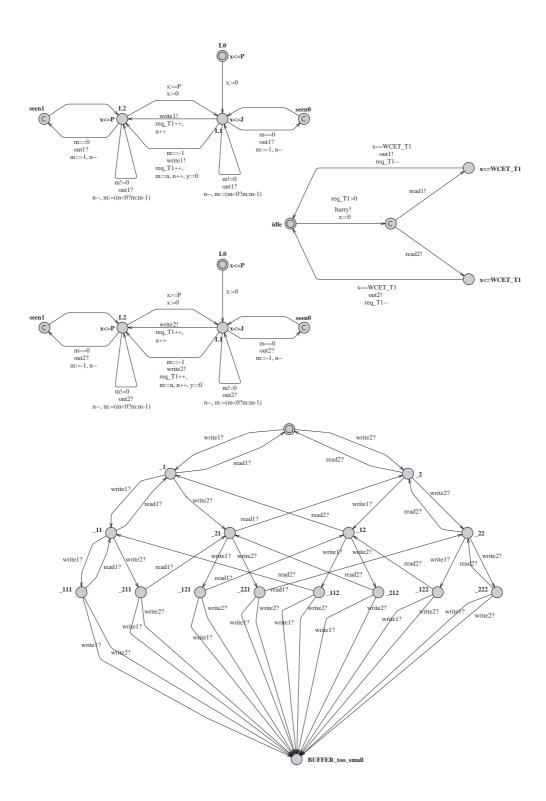

### 3.6.3 Performance analysis

The timed automata models of the single system components are aggregated into a timed automata network that represents a distributed embedded system. The single components interact via global variables and channels. For instance suppose that the timed automaton of an input event generator increments a global variable req to model the request of a task activation on a certain resource. The timed automaton that models the corresponding resource is sensitive to increments of the variable req and immediately starts the execution of the corresponding task if no higher priority task has to be executed. The completion of the task execution is modeled by the decrement of the variable req. Let's suppose that the corresponding output event triggers a second task. This can be modeled by incrementing a second global variable req2 simultaneously with the decrement of req. Again, another automaton will be sensitive to

the increments of req2, start the corresponding task and so on. In this way the propagation of events through the distributed system can be easily modeled.

The performance attributes of a distributed embedded system are derived by verifying properties of the corresponding timed automata network. For instance, to ensure that the maximum backlog of a certain task does not exceed a given value b, it is sufficient to verify the following property by model checking:

$$AG \quad (req \leq b)$$

where 'AG' stands for 'always generally' (= invariantly) and req is the global variable that counts the activation requests of the corresponding task. In particular it is possible to derive the exact maximum backlog by finding the smallest b that satisfies the above property. This can be done by using a binary search strategy.

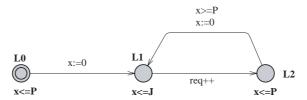

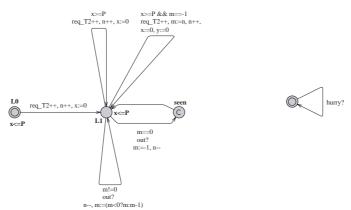

The verification of end-to-end delays is a little more involved as it requires to adapt the timed automata models of the corresponding input event generators. For instance Figure 3.17 shows the variant of a periodic event stream generator that permits to verify end-to-end latencies.

Figure 3.17: Timed automata model for a periodic input generator that measures the end-to-end delay

The automaton is synchronized with the system output over the global channel out and can keep track of the amount of time that passes between the generation of an event and its output from the system. Basically, the automaton can generate input events in the same way as the automaton of Figure 3.14 (left upper transition), but it can also arbitrarily choose to measure the end-to-end delay of an event (right upper transition). In particular, the variable n (initially 0) keeps track of the number of events that have been fed into the system and for which no response (a synchronization over the channel out) has been received yet. The clock y measures the response time and m (initially -1)

equals the number of responses that must be discarded before the one used for the measurement is seen. At most one measurement can be in progress and m = -1 if no measurement is in progress. For more details we refer the reader to [9].

Similar 'measuring' automaton variants are available also for other event streams. To ensure that the worst-case end-to-end delay of an event does not exceed a given value d it is sufficient to verify the following property by model checking:

$$AG \ (IG.seen \Rightarrow IG.y < d)$$

where we assume that 'IG' is the name of the measuring automaton. Again, the exact worst-case end-to-end delay can be determined by finding the smallest d that satisfies the property.

The described method for performance analysis based on model checking has an important benefit with respect to the approaches considered previously: it permits to derive not only hard but also exact bounds for performance properties of a distributed system. However, the price to pay is a potential high analysis effort due to the exhaustive model checking performed. In particular, the modeling of a distributed embedded system as a network of timed automata can easily lead to a state space explosion which makes the verification of system properties infeasible.

### 3.7 Remarks

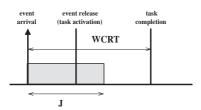

In this section we would like to point out a relevant difference in the interpretation of periodic task activation with jitter adopted by the various performance analysis methods. In particular, the holistic methods interpret the jitter in the activation of a task as release jitter, while all the other considered methods interpret it as arrival jitter. In the former interpretation the arrival and release of an event are distinguished: the events are assumed to arrive exactly at intervals of one period but their release may be delayed up to the maximum jitter value J. In the latter interpretation the maximum jitter value J defines an interval of admissible arrival times.

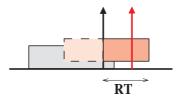

Although in both cases the interval of admissible task activation times is the same, this leads to a different analysis of the worst-case response time as depicted in Figure 3.18: the holistic methods (a) consider the release jitter already as part of the delay and refer the WCRT to the ideal periodic arrival time of the event, while the other performance analysis methods (b) refer the

- (a) interpretation adopted by the holistic methods

- (b) interpretation adopted by the other methods

Figure 3.18: Two different interpretations of activation jitter and WCRT

WCRT to the actual task activation time.

Usually it is not possible to convert the WCRT determined by a holistic method to the second interpretation, as the actual task activation instant leading to the worst-case response is unknown. However, the two interpretations of WCRT differ at most for the maximum jitter value J. Thus, the impact of this interpretation difference on the performance analysis results depends on the relative size of the WCRT in comparison with J: if the WCRT is much larger than J, then the two different interpretations will not lead to significantly different results. However, if the actual worst-case delay from the task activation to its completion is considerably smaller than J, then the holistic methods will provide poor performance analysis results compared to methods that adopt the second interpretation.

# Chapter 4

# PESIMDES - An extendible performance simulation library

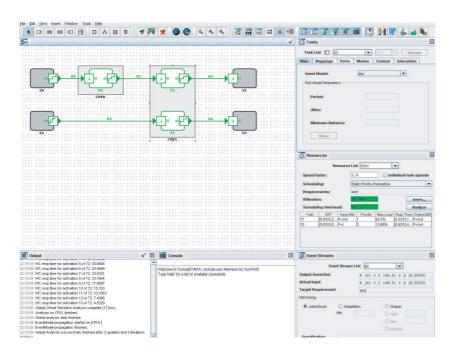

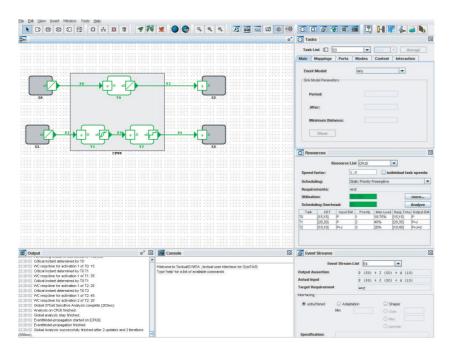

PESIMDES (**Performance Simulation of Distributed Embedded Systems**) was developed as part of this thesis and is an extendible open-source library for performance simulation of distributed embedded systems based on SystemC.

In this chapter we briefly review the motivations for developing PESIMDES, describe its features and explain the most important concepts of its implementation. A user guide to PESIMDES can be found in Appendix B.

### 4.1 Motivation

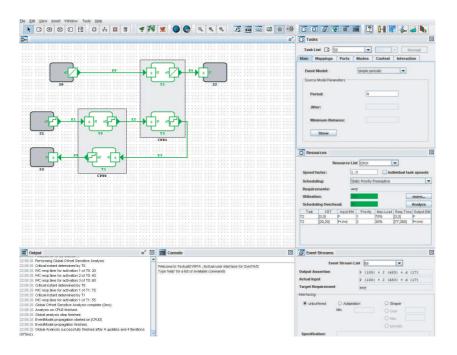

Whereas the use of formal approaches for performance analysis is still rare in industry, simulation can be considered the current state of the art in MpSoC performance verification. There are various commercial simulation environments for the simulation of distributed embedded systems. They differ from each other mainly in the level of abstraction of the simulation models. The range extends from cycle-accurate simulators for low-level models to discrete event simulators for system-level models.

While there are many different (mostly proprietary) software tools for low-level simulations, we have not found an adequate simulation tool focused on performance estimation of distributed embedded systems on the system-level, i.e. one which abstracts systems to an aggregation of event generators, processing resources and tasks with BCET/WCET.

SystemC [19], a widespread platform for system-level modeling and simulation, can be used to describe and simulate a distributed embedded system on the requested level of abstraction. However, this requires a substantial set-up effort, as all the necessary components of the system model must be implemented from scratch.

Because on a high level of abstraction all distributed embedded systems are composed of the same basic components, we have decided to collect these components in a common repository in order to reduce the set-up effort required for a SystemC performance simulation. The result is PESIMDES, a library for performance estimations of distributed embedded systems build on top of SystemC. PESIMDES is intended to be a pool of reusable modules which are designed to facilitate the system-level modeling and simulation of large distributed embedded systems in early design stages.

### 4.2 Performance metrics and modeling scope

PESIMDES provides estimations for the two most important performance metrics of a distributed embedded system: latencies and memory requirements. On the one hand the simulation allows to record the maximum observed end-to-end delay for the processing of event streams. On the other hand the maximum observed activation backlog of every single task can be monitored.

These results can be compared to the timing/memory requirements of the system and possible deadline misses or buffer overflows may be detected. The sequence of events leading to such a requirement violation can easily be traced back as all generated input stimuli are stored into trace-files which can be used to replicate the simulation.

Like any other simulation based approach, PESIMDES can only analyze single input instances out of all possible system inputs. Thus the tool itself cannot provide hard bounds for the worst-case performance of a system. It is up to the designer to provide a set of appropriate simulation stimuli which cover all relevant corner cases.

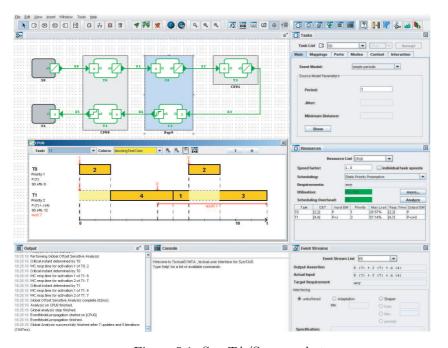

Table 4.1 summarizes the performance metrics supported by the current PESIMDES version. Regarding the modeling scope, PESIMDES offers various components to model the environment, the computation and communication resources, the tasks and the buffers of a distributed embedded system. To create a new system model, it is sufficient to select the proper components, instantiate them and link them together. Table 4.2 gives an overview of the current modeling power of PESIMDES. The modeling scope can easily be extended by adding new components to the library.

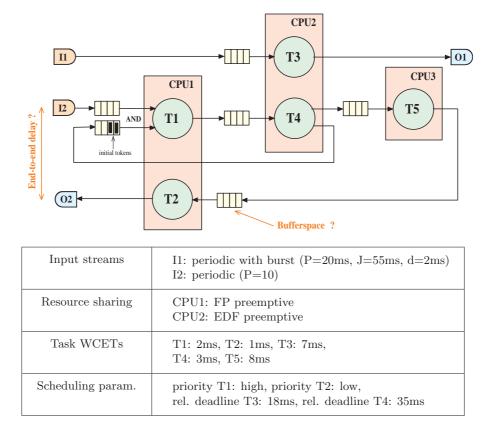

Figure 4.1 gives an example of a simple distributed embedded system that

<sup>&</sup>lt;sup>1</sup>By non-preemptive TDMA we mean that the execution of a task starts only if it can be concluded within the remaining time of the corresponding TDMA-slot, i.e. if the task can be executed without preemption.

| Performance metric                     | Supported |

|----------------------------------------|-----------|

| End-to-end delays (latencies)          | yes       |

| Memory requirement (buffer dimensions) | yes       |

| Resource utilization                   | not yet   |

Table 4.1: Performance metrics supported by the current PESIMDES version

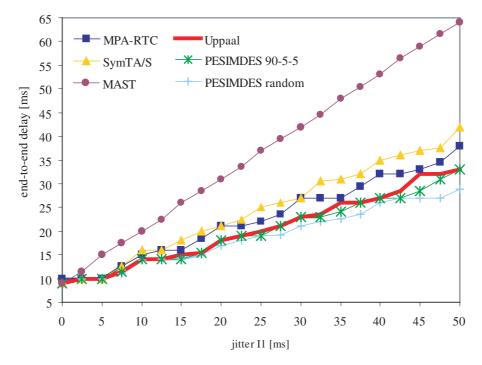

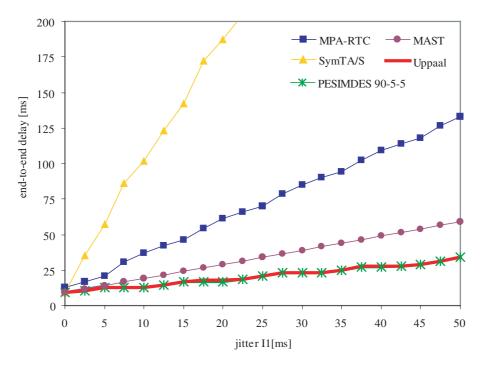

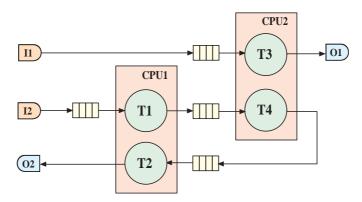

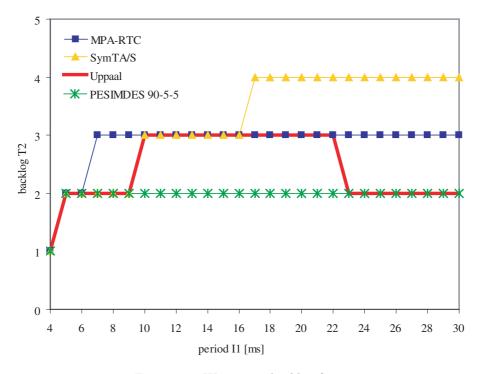

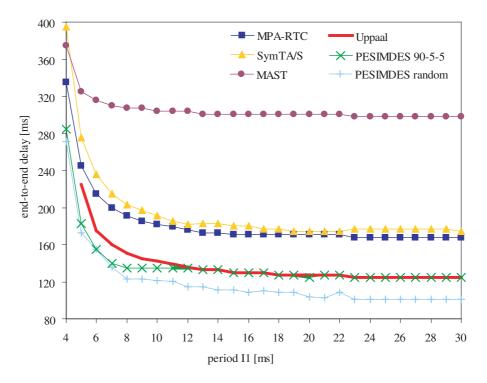

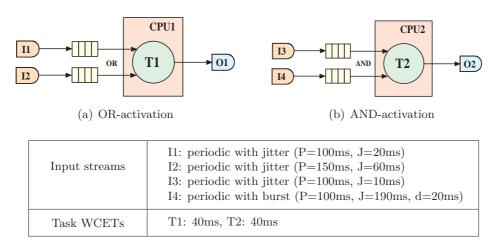

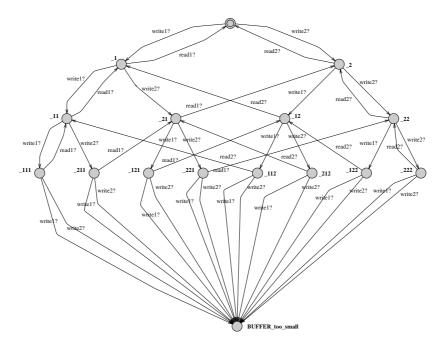

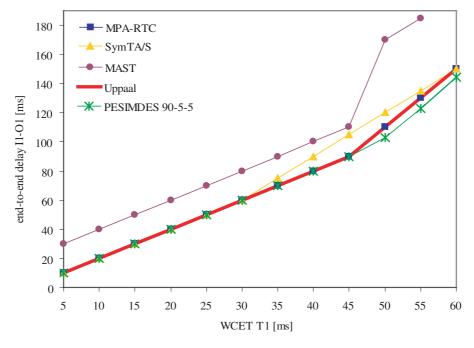

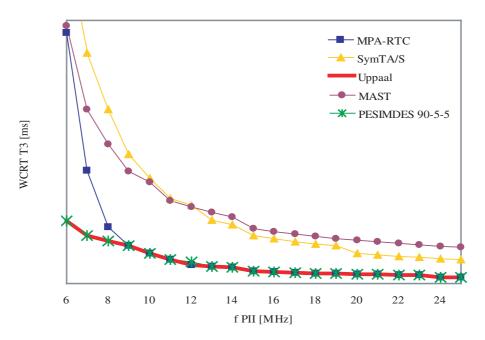

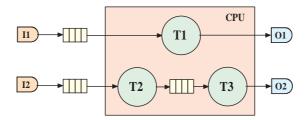

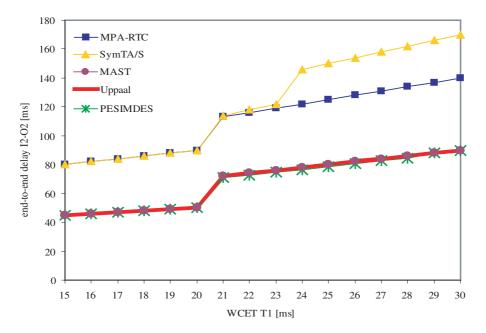

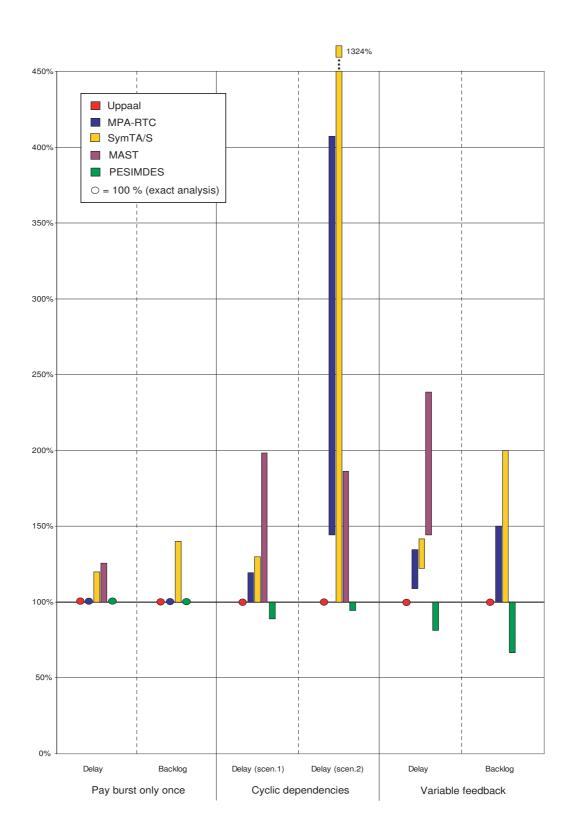

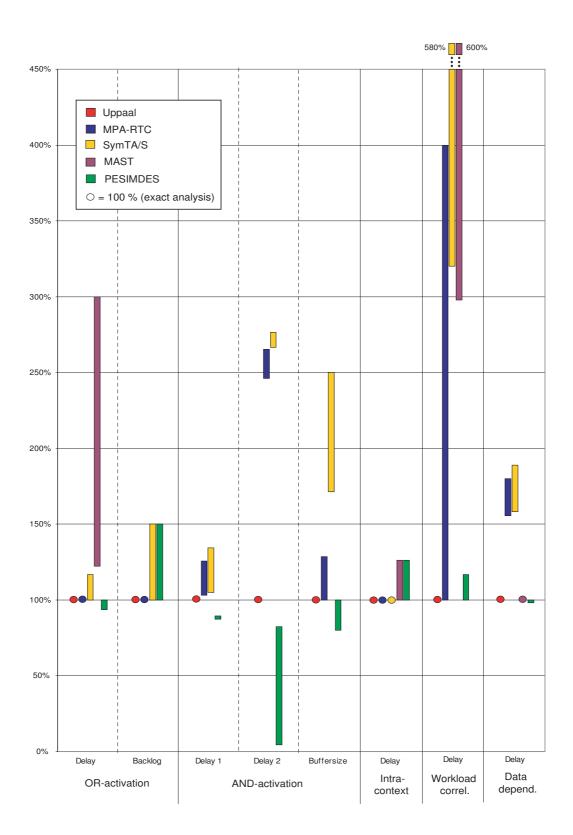

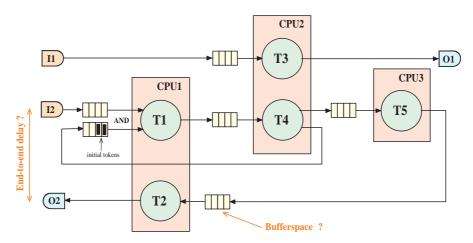

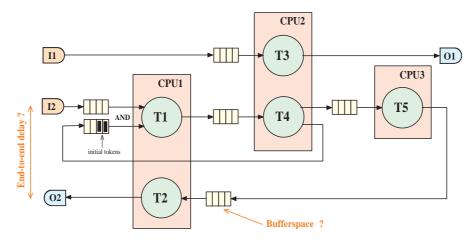

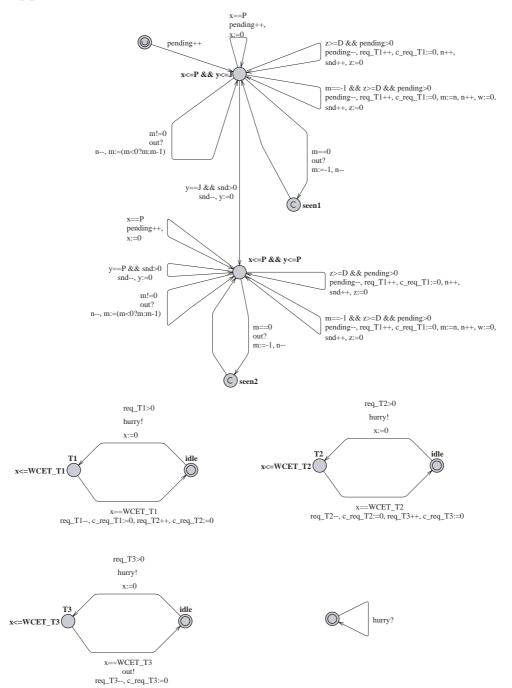

| Input Event Models           | periodic periodic with jitter periodic with burst sporadic sporadic with jitter sporadic with burst input from tracefile      |