# Window Based FIFOs for Communication in On-Chip Multiprocessor Systems

Hardware Design, Testing Strategies and Design Flow Integration.

Master's Thesis by David Grünert, 1 April – 30 Sept. 2006

Tutor: Kai Huang Supervisor: Prof. Dr. Lothar Thiele

Institut für Technische Informatik und Kommunikationsnetze Computer Engineering and Networks Laboratory

### Abstract

This thesis introduces a new communication model for on-chip multi-processor systems. The model is based on a high level interface that defines both the data transfer and the synchronisation of the connected processors. It was designed to simplify the reuse of hardware and software components and to support the automation of the design flow. On the one hand, these improvements help to minimise the time-to-market and the design costs, on the other hand it also leads to designs of higher quality because it avoids error-prone low level interfaces and ad-hoc synchronisations. The model of computation is based on an extension of Kahn process networks (KPN). It is therefore particularly suitable for the design of streambased applications in signal processing.

The thesis includes the description of the new concept, the hardware implementation of the new buffer type for an FPGA architecture, the definition and implementation of the API for buffer access, the implementation of an automated testing environment, a tool for automated system design and the discussion of theoretical aspects of WFIFO buffers such as memory requirements and determinateness.

Zurich, 30 September 2006

David Grünert

# Contents

| 1 | Intr | oduction 1                                   |

|---|------|----------------------------------------------|

|   | 1.1  | Problem Description: Limits of KPN           |

|   | 1.2  | Solution Approach: WFIFO Concept             |

|   | 1.3  | Research Contributions                       |

|   | 1.4  | Related Work                                 |

|   | 1.5  | Content of this Report                       |

| 2 | WF   | IFO: The Concept 7                           |

|   | 2.1  | WFIFO – Windowed FIFO                        |

|   |      | 2.1.1 WFIFO Protocol                         |

|   |      | 2.1.2 WFIFO Data Transport                   |

|   | 2.2  | System Modelling with WFIFO Process Networks |

|   | 2.3  | WFIFO Target Architecture                    |

|   | 2.4  | Example of Application                       |

| 3 | The  | Hardware Design 15                           |

|   | 3.1  | Target Platform and Core Selection           |

|   |      | 3.1.1 FPGA Platform                          |

|   |      | 3.1.2 Processor and Bus Selection            |

|   | 3.2  | WFIFO Overview                               |

|   |      | 3.2.1 Requirements and Problem Description   |

|   | 3.3  | WFIFO State Machine                          |

|   |      | 3.3.1 Single and Dual Bus Application        |

|   |      | 3.3.2 WFIFO State Machine Architecture       |

|   |      | 3.3.3 Protocol Violations                    |

|   |      | 3.3.4 WFIFO States                           |

|   |      | 3.3.5 Memory Management                      |

|   | 3.4  | WFIFO Memory                                 |

|   | 3.5  | Bus Driver Interface                         |

|   |      | 3.5.1 Implemented Instruction Format         |

|   |      | 3.5.2 Instruction Format Evaluation          |

|   | 3.6  | WFIFO Design Parameters                      |

|   | 3.7  | WFIFO Implementation Details                 |

|   |      | 3.7.1 IPIF IO Signals                        |

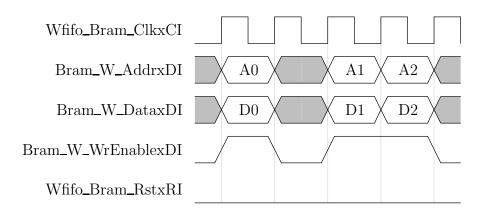

|   |      | 3.7.2 BRAM IO Signals                        |

|   |      | 3.7.3 States for Memory Management           |

|   |      | 3.7.4 Signal Level State Transitions         |

|   |      | 3.7.5 Output Signal Values                   |

|   |      | 3.7.6 WFIFO Process Level                    |

|   | 3.8  | myIPIF                                       |

|   | 0.0  | my m     |

| 4 | The  | WFIFO API                                               | 45 |

|---|------|---------------------------------------------------------|----|

|   | 4.1  | API Interface                                           | 46 |

|   |      | 4.1.1 Command Details                                   | 48 |

|   |      | 4.1.2 Error Handling and Compile Options                | 51 |

|   |      | 4.1.3 Command Latency                                   | 53 |

|   | 4.2  | WFIFO API Implementation                                | 53 |

|   | 4.3  | Alternative Status Signalling Concept                   | 56 |

|   |      | 4.3.1 Accessing the Error Signal with MB.               | 56 |

|   |      | 4.3.2 IPIF Problems with Error Signal                   | 57 |

|   |      | 4.3.3 MB Exception Handling                             | 57 |

|   |      | 4.3.4 Summary                                           | 58 |

|   |      | 1.0.1 Summary                                           | 00 |

| 5 | Test | ting                                                    | 59 |

|   | 5.1  | Challenge of Testing – Design for Testability           | 60 |

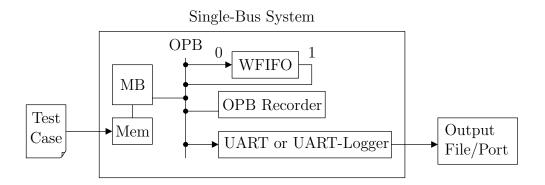

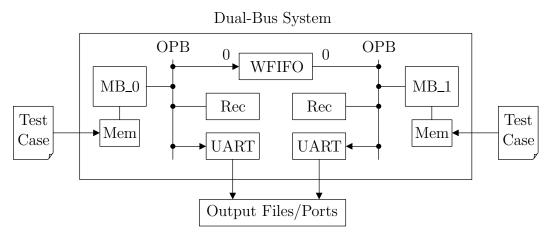

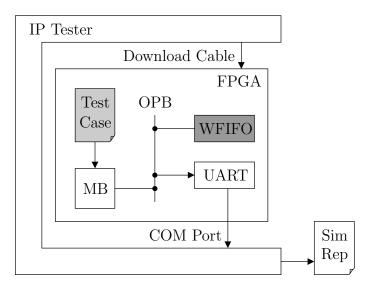

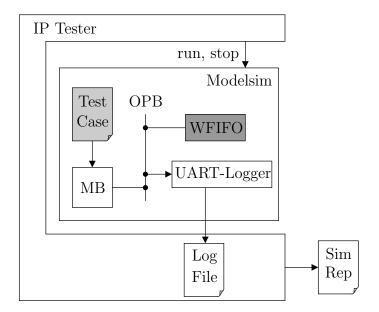

|   | 5.2  | Testing Architecture                                    | 63 |

|   |      | 5.2.1 Data Output                                       | 64 |

|   |      | 5.2.2 Data Acquisition                                  | 65 |

|   |      | 5.2.3 Example of Functional Test                        | 66 |

|   |      | 5.2.4 Example of Performance Test                       | 67 |

|   |      | 5.2.5 Summary                                           | 68 |

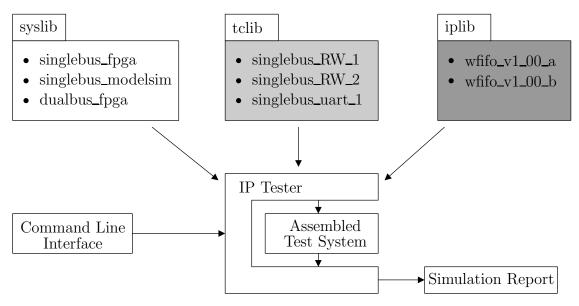

|   | 5.3  | Modular Testing Environment                             | 68 |

|   |      | 5.3.1 Command Line Options                              | 71 |

|   |      | 5.3.2 How to Write Test Cases                           | 72 |

|   |      | 5.3.3 How to Add New Systems                            | 72 |

|   |      | 5.3.4 Directory Structure                               | 73 |

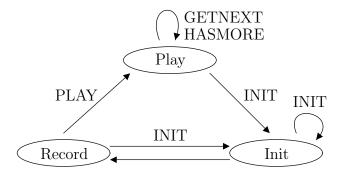

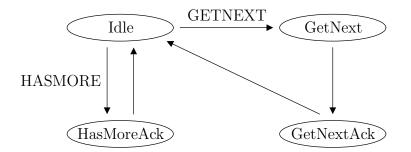

|   | 5.4  | OPB Recorder                                            | 74 |

|   | 5.5  | UART Logger                                             | 76 |

| 6 | Desi | ign Flow Integration and Automation                     | 77 |

| Ū | 6.1  | XPS Design Flow Integration                             | 77 |

|   | 6.2  | Automated Design-Flow                                   | 78 |

|   | 0.2  | 6.2.1 Automated Mapping                                 | 79 |

|   |      | 6.2.2 WAB – WFIFO Architecture Builder                  | 83 |

|   |      |                                                         | 00 |

| 7 | WF   | IFO Theory                                              | 87 |

|   | 7.1  | KPN Compliance                                          | 87 |

|   | 7.2  | A Model for Data Transport in Communication Channels    | 88 |

|   |      | 7.2.1 Classifications of Communications Channels        | 90 |

|   | 7.3  | Classification of Implementation Alternatives           | 90 |

|   | 7.4  | Minimum Memory Size for Channels with Reordering Memory | 91 |

|   | 7.5  | Minimum Memory Size for WFIFO Channels                  | 92 |

|   |      | 7.5.1 Channels with Equal Read and Write Windows        | 93 |

|   |      | 7.5.2 Channels with Non-Overlapping Windows             | 94 |

|   |      | 7.5.3 Channels with a Brick Wall Window Structure       | 95 |

|   | 7.6          | Non-Blocking Acquiring and Determinism                                                                               | 97                           |

|---|--------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|

| 8 | WFI<br>8.1   | Compared Concepts                                                                                                    | <b>9</b><br>99               |

|   |              |                                                                                                                      | 99                           |

|   | 0.0          |                                                                                                                      | 99                           |

|   | $8.2 \\ 8.3$ | Motivation and Origin       10         Hardware       10                                                             |                              |

|   | 8.4          |                                                                                                                      |                              |

|   | 8.5          | Memory Usage       10         API Concept       10         10                                                        |                              |

|   | 8.6          | Latency                                                                                                              |                              |

|   | 8.7          | Summary                                                                                                              |                              |

| • |              |                                                                                                                      |                              |

| 9 |              | Iook and Conclusion     10       Conclusion     10                                                                   | -                            |

|   | 9.1          | Conclusion       10         9.1.1       Summary of Completed Work         10                                         |                              |

|   | 9.2          | 9.1.1         Summary of Completed Work                                                                              |                              |

|   | 9.2          | 9.2.1 FIFO Read and FIFO Write                                                                                       |                              |

|   |              | 9.2.2 Block Transfer                                                                                                 |                              |

|   |              | 9.2.3 Multiple Processes on one Processor                                                                            |                              |

|   |              | 9.2.4 Complete and Verify WFIFO Theory                                                                               |                              |

|   |              | 9.2.5 Find Relevant Application Examples 10                                                                          |                              |

| Α | The          | sis Assignment 11                                                                                                    | 1                            |

|   |              |                                                                                                                      |                              |

| В |              | rce Code 11                                                                                                          | -                            |

|   | B.1          | WFIFO API                                                                                                            | -                            |

|   | B.2          | OPB Recorder API                                                                                                     | .7                           |

| С |              | DL Code 11                                                                                                           | -                            |

|   | C.1          | WFIFO                                                                                                                | -                            |

|   |              | C.1.1 WFIFO Top                                                                                                      |                              |

|   |              | C.1.2 WFIFO Logic                                                                                                    |                              |

|   |              | C.1.3 WFIFO BRAM                                                                                                     |                              |

|   |              | C.1.4 MPD                                                                                                            | 13                           |

|   |              |                                                                                                                      |                              |

|   | C a          | C.1.5 PAO                                                                                                            | 14                           |

|   | C.2          | C.1.5 PAO                                                                                                            | 14<br>14                     |

|   |              | C.1.5       PAO       14         OPB Recorder       14         C.2.1       MPD       15                              | 14<br>14<br>52               |

|   | C.2<br>C.3   | C.1.5       PAO       14         OPB Recorder       14         C.2.1       MPD       15                              | 14<br>14<br>52               |

| D | C.3          | C.1.5       PAO       14         OPB Recorder       14         C.2.1       MPD       15                              | 44<br>14<br>52<br>53         |

| D | C.3          | C.1.5       PAO       14         OPB Recorder       14         C.2.1       MPD       15         UART Logger       15 | 44<br>52<br>53<br>5 <b>5</b> |

# **1** Introduction

Today's signal processing systems such as mobile-phones and set-top boxes have requirements that can not be satisfied with a single-processor architecture. The primary reasons for choosing a multiprocessor architecture are that a single-processor has not enough computing power or that it's power consumption is too high. But the performance requirements can not be the only reason for the trend to multiprocessor architectures. It can be observed that dedicated components are replaced by general purpose processors whenever this can be done with acceptable effort.<sup>1</sup> This trend is clearly not motivated by the need for more computing power, because dedicated hardware usually is more powerful than a general purpose processor of similar size.

Although the required computing power and power consumption are important properties for the system design, it emerged that other points in architecture and software design are at least equally important for the success of the designed product. Depending on the field of activity, these points are known under different key words. Where the management talks about time to market, design costs or market size, engineers understand reuse, short and automated design cycles and programmability. Although this thesis does not discuss marketing aspects, engineers can benefit from this similarity of goals when explaining the necessity for a development step to the management. Independently from the professional background, the concepts aim at a more flexible solution while minimising the design time. The following list summarises these trends and their motivation.

- **Software Solutions:** Dedicated hardware is replaced by software running on processors. Programmable systems simplify upgrades, bug fixes and make it possible to provide a big array of products that are all based on the same hardware.

- **Reuse:** The reuse of hardware leads to shorter design time. No time is used for the hardware design of the reused blocks and the verification is limited to tests that check whether they are properly connected and configured. It is not necessary to test the complete functionality of the reused block if it was designed properly. Reuse also has a software aspect. In most current designs, much more engineering power is used for software design than for hardware design. Changes in the hardware can have major impact on the software and cause high costs.

- **Automation:** In the design cycles many steps are automated. Examples are automated testing environments and the automated system assembly from IP libraries. The shorter design cycles made possible by the automation allow multiple redesigns before the product is launched, which leads to better quality. On the other hand, it is possible to design a first version in a very short time. This version does not necessarily include the complete functionality but in many cases it is good enough for the customer to make first tests.

<sup>&</sup>lt;sup>1</sup> For high performance parallel systems, a similar trend can be observed. Parallel systems with specialised hardware and architectures are replaced by clusters built from off-the-shelf computing systems.

In this thesis, a solution for the implementation of signal processing systems that follows these trends is presented. A special property of signal processing systems is that they often have a stream-based or pipelined structure. An input signal is processed in a number of subsequent steps, and the output of one step serves as input for the next step. A popular way for modelling signal processing systems is the Kahn process network (KPN). The KPN models the system with a set of processes that are connected with FIFO buffers. Each process follows a sequential program and uses only the FIFOs for data exchange. The used FIFOs have unlimited size and blocking read. The blocking read stops the calling process in case there are no data available until new data arrive. The model has become popular because all systems modelled with KPN are determinate. Furthermore, synchronisation is done with a simple blocking read semantic.

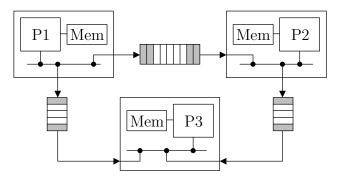

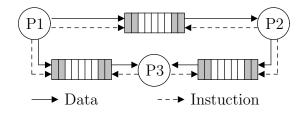

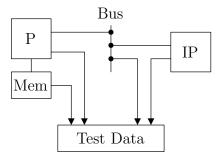

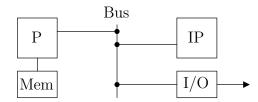

When implementing a KPN with a multiprocessor architecture, it is reasonable to treat the processes as the smallest unit and to map one or more of them on the same processor. In most cases, this is the best solution because it minimises the data dependencies between the processors and leads to a smaller load on the interconnection network. However, the common multiprocessor architectures are not very good for the realisation of such systems. The best one of them is the MIMD-architecture (Figure 1.1).<sup>2</sup> The following list outlines the problems of this architecture.

Figure 1.1: MIMD example architecture with processors P and instruction/data memories Mem.

- All communication modelled by the FIFO buffers has to share the same bus. This limits the data throughput and even if the interconnection network satisfies the data rates of the implementation, it limits the extendability of the system.

- A bus arbiter is required, which is equal to adding a global control structure to the system. This kind of global control is not included in the KPN model. It must therefore be shown that the bus arbiter does not violate the KPN rules and that the system delivers the expected results. For many situations, this is difficult and the automation of the design flow is very demanding.

- Synchronisation between the processes is based on low level mechanisms like interrupts and shared memory. This makes the behaviour of the system dependent on the used hardware and it is more difficult to migrate the design on a new processor type.

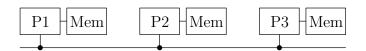

A solution for these problems is to use an architecture with a dedicated structure that is more similar to the KPN model. Figure 1.2 shows such an architecture. In this architecture,

<sup>&</sup>lt;sup>2</sup> Multiple Instruction Multiple Data.

each processor has its own bus and a special hardware block is used to implement the FIFO channel. This channel implements the blocking read synchronisation in hardware.

Figure 1.2: KPN based architecture with a dedicated structure.

Because the processor is the single master device, no bus arbitration or global scheduling is required. Each processor can use the full bus speed and this speed is not reduced when additional processing steps are added. The synchronisation is implemented in an isolated block and makes no use of low level mechanisms.

## 1.1 Problem Description: Limits of KPN

The KPN architecture offers distributed control and a simple interface for programming, but it also includes limitations that make the implementation of stream-based algorithms difficult or inefficient. The following three limitations that are of great importance for signal processing algorithms are addressed in this paper.

- **Reordering:** The communication channel behaves in a strict first in first out manner, which does not allow to read data in another order as they were written.

- Multiple Read: The communication channel does not allow to read the same data item more than once. After reading an item, it is deleted from the buffer and cannot be read a second time.

- **Skipping:** It is not possible to remove an item from the channel buffer without reading it. If the buffer contains unwanted data, all of these data must be read.

The first two limitations can be handled with the FIFO architecture shown in Figure 1.2 if a local memory is used to implement the reordering and the multiple read. In most cases, the memory used to store the instructions of the processor can be used for this purpose. In such an implementation, the process has to implement the memory management for the reordering memory which is a task that was not modelled by the original process network. Furthermore it requires computing time. A known solution for this problem is to use a special address generation unit (AGU) ([11], [15]). Implementing skipping is not possible with an architecture using FIFOs. A new buffer type is required for this purpose.

## 1.2 Solution Approach: WFIFO Concept

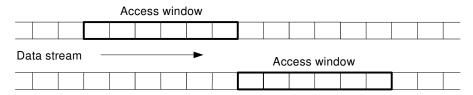

The solution presented in this thesis defines a new type of process network, the WFIFO process network. It is based on the Kahn process network, but the FIFO buffers are replaced by a new buffer type called windowed FIFO (WFIFO). The WFIFO buffer is similar to the normal FIFO but it allows multiple read, reordering and skipping at the head and the tail of the buffer. These memory regions at the head and the tail are called windows. They have a user-defined size and are allocated and released at runtime by API instructions. The API follows a protocol with three subsequent steps: acquiring, data read/write and releasing. With acquiring, a new window is allocated, then its content can either be written or read. Before acquiring the next window, the previous must be released. Details of the WFIFO concept are presented in Chapter 2.

## 1.3 Research Contributions

- The WFIFO concept for the communication in on-chip multiprocessor systems is presented in detail. It is shown how data are transferred over a WFIFO buffer and the protocol used is explained.

- The WFIFO buffer is implemented in hardware for a Xilinx FPGA platform. The problems and requirements of the design are discussed and details of the implementation are shown.

- The API is defined in detail and it is realised for the WFIFO hardware implementation. Extra functionality is added to the API to simplify testing.

- Different strategies for IP and system testing are discussed and the solution implemented for the WFIFO design is presented. For testing purposes, two special IPs are designed. The implemented solution allows to perform both functional and performance tests.

- The testing procedure is automated with a SW tool. The program is controlled over a command line interface and can run multiple tests on the same test system. After test execution, a test report is generated.

- The design of WFIFO architecture is automated with a SW tool. The application takes an abstract specification of the system as input and generates the target architecture for the FPGA platform used.

- It is discussed whether a process network with WFIFO buffers is determinate or not. It is shown that with some restrictions, a WFIFO process network is a subset of Kahn process networks.

- The WFIFO concept is compared with two other concepts that are motivated by similar ideas like the WFIFO concept.

- Aspects concerning the optimal usage of the WFIFO concept are discussed.

### 1.4 Related Work

Discussions on the extension of the KPN model have a long tradition and many publications have been issued. Most of these publications can be assigned to one of the following two approaches. The first includes design-flow-centric approaches and the second includes interface-centric approaches. The WFIFO model was designed with both of theses aspects in mind. It includes the definition of a new interface and the automation of the hardware design.

The interface-centric approaches focus on the improvement of the interface that is used by the processes to communicate. An interface that is related to the interface used by the WFIFO was presented in [3]. In contrast to the WFIFO, this interface allows multiple acquiring before releasing and the transfer of data blocks. The proposed system has a MIMD architecture with distributed memory which is very different to the WFIFO architecture. Another interface-centric paper is [13]. It presents a set of seven different interface definitions. The interfaces named CB and RB (Combined and Relative Blocking) are the ones that are most similar to the WFIFO approach. In contrast to the WFIFO interface, CB and RB both allow multiple acquiring before releasing. This paper is based on ideas from [1], which also discusses the design-flow aspects.

The design-flow-centric approaches focus on the automation of the design flow. One of these approaches it the Compaan/Laura tool-chain [8]. This tool-chain takes Matlab code with a nested loop structure as input and converts it into a KPN model. In a second step, dedicated hardware is generated and the KPN is mapped on this architecture. A set of solutions to overcome the multiple-read and the reordering limitations were presented in [11] and [15]. Another approach was followed with the SHIM model [2]. SHIM takes a C-like description as input where both hardware and software is described and shared variables are used to model the communication. From this description, a dedicated hardware and the required software is generated. A buffer using a rendezvous protocol is used to implement the communication channel.

## 1.5 Content of this Report

#### Introduction

**Chapter 2:** Introduces the concept of the WFIFO buffer, gives a first impression of the WFIFO API and shows how an algorithm can be modelled with a WFIFO process network. It also shows the structure of the target architecture and a simple example is made to give a first example of application.

#### **Practical Work**

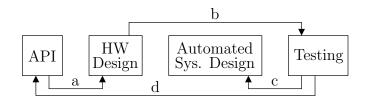

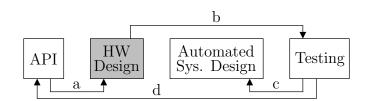

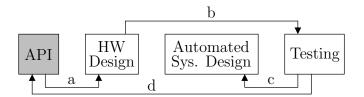

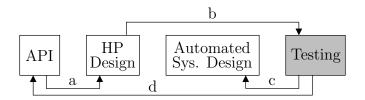

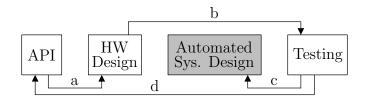

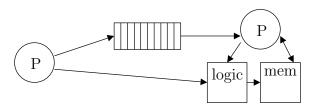

The practical work is described in four chapters which can not be completely separated. Figure 1.3 gives an overview of the dependencies. This figure is repeated at the beginning of each of the four chapters and the dependencies of the respective part are discussed. Each chapter starts with the general aspects and goes more and more into the details.

- **Chapter 3:** Presents the hardware implementation of the WFIFO concept. The requirements and problems for the hardware implementation are listed and details of the implementation are presented. Furthermore, the FPGA platform used is indicated and the selection of the processor and bus types is explained.

- **Chapter 4:** Defines the API in detail and shows how it was implemented for the designed WFIFO buffer. A concept to simplify testing is presented.

- **Chapter 5:** Discusses the problem of hardware testing by explaining the solution implemented for the WFIFO project. It also shows how testing was automated with the design of a modular testing environment. The presented testing concept addresses the IP verification and the performance measurement of complete systems.

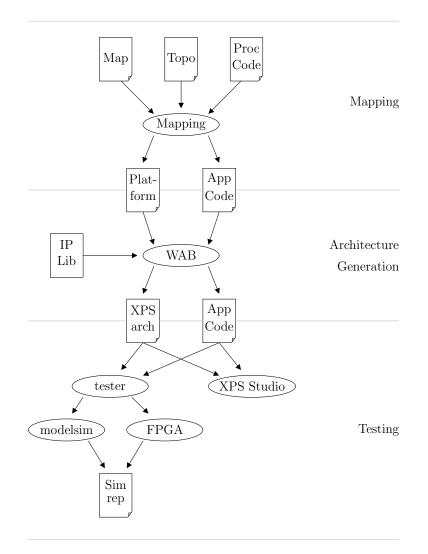

- **Chapter 6:** Presents the automation of the hardware design. A software tool was developed that can generate a complete and synthesizeable implementation of a WFIFO process network from an abstract specification.

Figure 1.3: Chapter dependencies of the practical work.

#### Theoretical Work

- **Chapter 7:** Discusses whether a process network with WFIFO buffers is determinate or not. A concept for describing the data transport in communication channels is presented. This concept is used to calculate minimum memory requirements for WFIFO channels and for channels with reordering memory.

- **Chapter 8:** Compares the WFIFO concept with two other approaches for implementing communication with multiple read and reordering in process networks.

- **Chapter 9:** Contains the conclusion and the outlook. The conclusion refers to the beginning of my work, gives an impression of its scope and lists the completed tasks. The outlook shows how the WFIFO concept could be further developed.

# 2 WFIFO: The Concept

# 2.1 WFIFO – Windowed FIFO

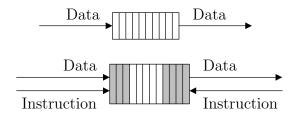

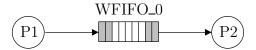

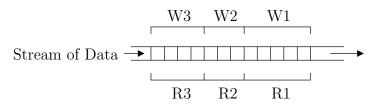

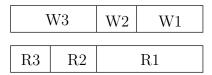

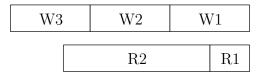

The WFIFO buffer is related to the normal FIFO but it offers more functionality and flexibility. The normal FIFO behaves in a strict first-in first-out manner which does not allow to read data in another order than they were written to the FIFO. Furthermore, each data item written to the buffer must be read exactly once. It is not possible to read the same item more than once or to remove an item from the buffer without reading it. Unlike the FIFO buffer, the WFIFO buffer allows to skip unwanted data. It also supports data reordering and multiple read within a continuous data segment located at the FIFO's head or tail. These segments are called windows, which has lead to the name WFIFO for this buffer structure. Figure 2.1 shows the simplified schematic representation of a FIFO and a WFIFO buffer. It shows that the WFIFO has a more complex interface. Read and write windows are indicated in gray.

Figure 2.1: Simplified schematic of FIFO and WFIFO with write port on the left and read port on the right side.

While the FIFO buffer allows a single instruction at both ports, i. e. data-write at the input port and data-read at the output port, the WFIFO supports two additional instructions at each port. Table 2.1 lists these instructions. They can not be used an in arbitrary order. The next section explains the required protocol for the instructions and what they are used for. A detailed description of the API is given in Chapter 4.

| Write Port Instructions                     | Read Port Instructions             |  |  |

|---------------------------------------------|------------------------------------|--|--|

| • Acquire-read-window(port, size)           | • Acquire-write-window(port, size) |  |  |

| • Data-read(port, offset, data)             | • Data-write(port, offset, data)   |  |  |

| $\bullet \ {\rm Release-read-window(port)}$ | • Release-write-window<br>(port)   |  |  |

Table 2.1: WFIFO instructions for read and write port.

#### 2.1.1 WFIFO Protocol

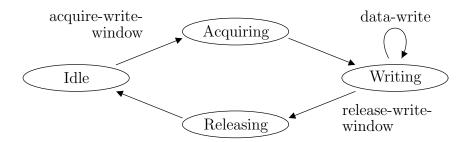

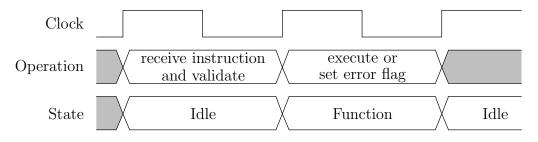

Writing to and reading from a WFIFO are two independent transactions, which both follow a protocol. The protocol is defined by three subsequent steps and four WFIFO-internal states (Figure 2.2). The enumeration below explains the steps for the write port of the WFIFO. It is assumed that the write port is currently in the idle state and the process connected to the write port wants to write some data to the buffer.

Figure 2.2: States of the WFIFO write port.

- 1. Before writing any data to the WFIFO buffer, a write window must be acquired, which is done by passing an acquire-write-window instruction to the WFIFO. This instruction takes the window size as argument. When receiving the instruction, the WFIFO port changes into the acquiring state. If there is enough free memory<sup>1</sup> in the WFIFO, it acquires the window and changes into the write state. From then on data can be written to the WFIFO (Step 2) or the window can be released (Step 3). If there is not enough memory, the WFIFO's behaviour depends on the instruction type used. There are two versions of the acquire instruction: a blocking and a non-blocking one. When using the blocking version, the WFIFO waits until enough memory becomes available and the calling process is blocked during this time. As soon as enough memory is available, the WFIFO changes into the write-state and wakes up the blocked process. If there is not enough memory for the non-blocking version, the WFIFO returns into the idle state and signals the calling process that acquiring failed.

- 2. As soon as the WFIFO reaches the writing-state, data can be written to the window. The write instruction takes the data to write and an offset position as arguments. The offset indicates to which position the data is written within the write window. The instruction can be repeated an unlimited number of times as long as the WFIFO is in the writing-state. It is possible to write the same offset position more than once, which results in overwriting the old value. If an offset position is never written, its value is undefined. The writing-state is left when executing the release instruction (Step 3).

- 3. The release instruction is executed to terminate writing, and it can only be executed if the WFIFO is in writing-state. When receiving the release instruction, the WFIFO

$<sup>^{1}</sup>$  The terms free-memory and internal FIFO used in this description are explained in 2.1.2.

changes into the releasing-state and closes the write window. After that, no further writing is possible until a new write window is acquired. After releasing is done, the WFIFO changes into the idle state.

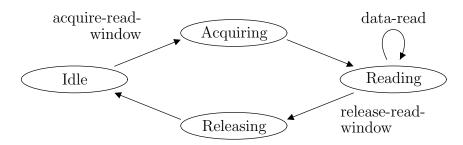

The protocol for the read port is very similar to the protocol of the write port. It is also defined by three steps and four WFIFO-internal states (Figure 2.3). The enumeration below is focused on the difference between the read and write protocols.

Figure 2.3: States of the WFIFO read port.

- 1. The read port also offers two acquiring functions a blocking and a non-blocking one. Acquiring can be executed successfully if there are enough data available in the internal FIFO buffer.

- 2. Step two is the same as for the write port except that data are read from the window instead of written.

- 3. Releasing the read window is equal to deleting all of its content from the buffer. No further read operations on the data within the window are possible. The memory that was occupied by the read window is added to the free memory.

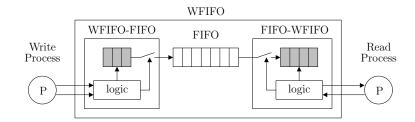

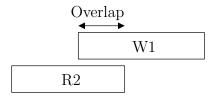

#### 2.1.2 WFIFO Data Transport

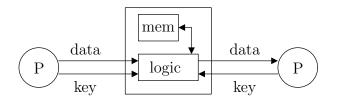

From the perspective of data transport, the WFIFO buffer can be understood as a normal FIFO channel with a reordering memory implemented as read and write windows at its head and its tail. Such a model is shown in Figure 2.4. The logic block is used to implement the WFIFO protocol. This model does not show the internal structure of the WFIFO. It is only used to describe the data transport between the WFIFO write and read port. Differences between the model and the WFIFO implementation are discussed at the end of this section.

Figure 2.4: Models used to explain the data transport in WFIFO buffers. The reordering memories are indicated in gray.

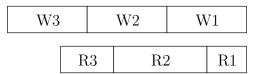

When the logic at the write port receives an acquire-write instruction, it enables writing to the reordering memory. This memory has a continuous address range starting with zero and a size as big as the specified window. Subsequent write instructions are redirected to this memory at the position indicated by the offset. When receiving a release instruction, writing is disabled and the content of the memory segment is shifted to the FIFO without changing its order.

The logic at the read port starts reading data from the FIFO when receiving an acquireread instruction. It reads as many items as specified by the window size and writes them to the reordering memory with the same addressing concept as the write window. Also here, the order of the data is not changed and the last item read has the memory address zero. After reading from the FIFO is finished, read operations are redirected to the memory position indicated by the offset. When receiving a release instruction, reading is disabled.

As indicated above, the realisation with FIFO buffer and reordering memory only models the WFIFO's functionality. This model is useful to explain the data transport but it does not describe all aspects of the WFIFO's behaviour correctly. In the WFIFO hardware implementation, a single memory block is used instead of the combination of FIFO and reordering memory. This memory block is segmented into four regions: free-memory, readwindow, FIFO-buffer and write-window.<sup>2</sup> Because the memory block has a finite size, there is a maximum amount of memory that can be occupied by the windows and the FIFO-buffer. If a process tries to acquire a new write window when all memory is used, it is blocked. This kind of blocking is not modelled correctly by the WFIFO model from above because it never blocks on acquiring. But the model can block in another situation: if the FIFO buffer has limited size, the model blocks during the release instruction if there is not enough free memory left to write all data. The implementation with the single memory never blocks during release.

$<sup>^2~</sup>$  A detailed description of the required memory management is given in Chapter 3.

## 2.2 System Modelling with WFIFO Process Networks

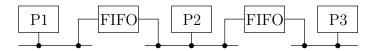

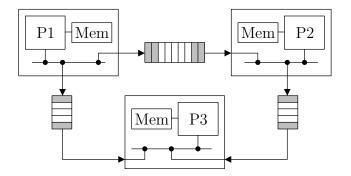

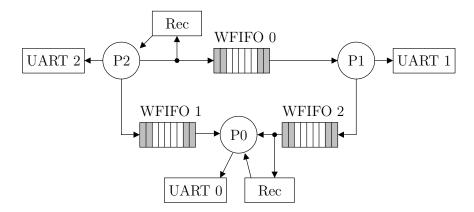

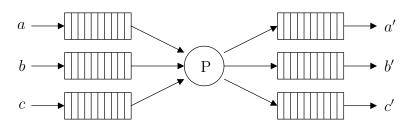

Implementing a signal processing system starts with modelling the system's behaviour as a WFIFO process network. This is similar to system modelling with Kahn process networks but windowed FIFOs are used instead of normal FIFOs. A system model includes the source code for the processes and the description of the topology of the underlying process network. For all communication between the processes, WFIFO buffers are used. They are accessed with the WFIFO API. A source code example is given in 2.4. Figure 2.5 shows a topology of a WFIFO process network with three processes.

Figure 2.5: Example WFIFO process network with P1 as data source and P3 as data sink.

In order to benefit from the advantages of the WFIFO concept it is important to use the additional options in a reasonable way. With the read and write windows, a segmentation of the data is introduced that was not necessary for the FIFO buffers in KPN networks. For making a good WFIFO design, the definition of the data segmentation is essential. There are situations where a segmentation is contained in the signal processing algorithm. In other situations, the segmentation must be defined by the designer. In Chapter 7 mathematical concepts are presented for data segmentation.

The advantages of a windowed FIFO can be summarised under multiplicity, reordering and skipping. Multiplicity means that the same data item can be accessed more than once. On the read port, the same item can be read an unlimited number of times as long as it is in the read window. On the write port it is possible to update values that were already written to the buffer until the write window is released. Reordering allows data items to be consumed in an order other than produced. Both, the producer and the consumer can reorder the data within the acquired windows. If the consumer does not read all data within the read window this can be seen as skipping of unwanted data. Skipping makes sense if it is not possible for the producer to know if data will be required by the consumer or not.

## 2.3 WFIFO Target Architecture

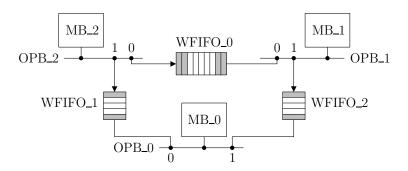

The target system has a dedicated architecture and is assembled from two building blocks. One includes the WFIFO buffer, the other a processor with a bus and a memory for instructions and internal data (Figure 2.6).

Figure 2.6: Building blocks for the WFIFO architecture. Mem is the instruction and local data memory of processor P1.

To build the target architecture, the topology of the WFIFO process network and a mapping definition is used. The mapping defines which processes have to share a processor. No mapping is required for the WFIFO buffers because each buffer is mapped on one WFIFO hardware block. The connections of the WFIFOs are well-defined by the topology and the mapping defined for the processes. Figure 2.7 shows a WFIFO architecture of the process network shown in Figure 2.5 for a one-to-one mapping.

Figure 2.7: WFIFO example architecture.

Since the WFIFO architecture is a dedicated solution, it is important to automate the hardware design flow. In contrast to heterogeneous architectures, it is simple to implement such an automation for a WFIFO architecture. Advantages are:

- Only two building blocks are used.

- No bus arbitration is required because each bus has a single master device, the processor, and a set of equal slave devices, the WFIFOs.

- Bus address range segmentation is simple because the WFIFOs require a range of equal and fixed size.

- No access arbitration for a global memory is needed.

- No global scheduler with access to all processors is needed.

## 2.4 Example of Application

In this section a first simple example of application is shown. Details of the API are given in Chapter 4. The example below does not use all the options offered by the WFIFO. It is a first and simple code example. The algorithm is given as a C-code sequence (Figure 2.9). It contains a producer and a consumer section. In the producer section, the two dimensional array A is written. In the consumer section it is read. The communication channel used when mapping the producer and the consumer section on two different processors must support multiple read and reordering. The code for the process network is given in Figure 2.10.

Figure 2.8: Topology of WFIFO process network for a consumer producer pair.

```

// P1: producer

for (i=0; i<4; i++) {

for (j=0; j<3; j++) {

write(A[i][j]);

}

}</pre>

```

```

// P2: consumer

for (i=0; i<3; i+=2) {

for (j=0; j<2; j++) {

read(A[i][j]);

read(A[i+1][j]);

read(A[i][j+1]);

read(A[i+1][j+1]);

}

}</pre>

```

Figure 2.9: Source code of the algorithm.

```

// P1: producer

void main() {

WFIFO_ACQUIRE_WRITE(0,6);

WFIFO_WRITE(0,0,A[0][0]);

WFIFO_WRITE(0,1,A[0][1]);

WFIFO_WRITE(0,2,A[0][2]);

WFIFO_WRITE(0,3,A[1][0]);

WFIFO_WRITE(0,4,A[1][1]);

WFIFO_WRITE(0,5,A[1][2]);

WFIFO_RELEASE_WRITE(0);

WFIFO_ACQUIRE_WRITE(0,6);

WFIFO_WRITE(0,0,A[2][0]);

WFIFO_WRITE(0,1,A[2][1]);

WFIFO_WRITE(0,2,A[2][2]);

WFIFO_WRITE(0,3,A[3][0]);

WFIFO_WRITE(0,4,A[3][1]);

WFIFO_WRITE(0,5,A[3][2]);

WFIFO_RELEASE_WRITE(0);

}

```

```

// P:2 consumer

void main() {

WFIFO_ACQUIRE_READ(0,6);

WFIFO_READ(0,0,A[0][0]);

WFIFO_READ(0,3,A[1][0]);

WFIFO_READ(0,1,A[0][1]);

WFIFO_READ(0,4,A[1][1]);

WFIFO_READ(0,1,A[0][1]);

WFIFO_READ(0,4,A[1][1]);

WFIFO_READ(0,2,A[0][2]);

WFIFO_READ(0,5,A[1][2]);

WFIFO_RELEASE_READ(0);

WFIFO_ACQUIRE_READ(0,6);

WFIFO_READ(0,0,A[2][0]);

WFIFO_READ(0,3,A[3][0]);

WFIFO_READ(0,1,A[2][1]);

WFIFO_READ(0,4,A[3][1]);

WFIFO_READ(0,1,A[2][1]);

WFIFO_READ(0,4,A[3][1]);

WFIFO_READ(0,2,A[2][2]);

WFIFO_READ(0,5,A[3][2]);

WFIFO_RELEASE_READ(0);

}

```

Figure 2.10: Source code for the WFIFO process network.

# 3 The Hardware Design

This chapter shows details of the WFIFO hardware implementation. The implementation includes the design of new IPs, namely the WFIFO IP and the selection of the target platform and the IP cores. All components together make it possible to realise a complete WFIFO architecture.

Figure 3.1: Overview of practical work.

Figure 3.1 shows the dependencies of the hardware design. The WFIFO hardware is used by the API and makes use of the testing infrastructure. Because the testing itself uses the API there is a closed loop including hardware design, testing and API. This means that the hardware design must be done in a way that allows to make tests. This fact is well known as DFT – design for testability. The interface between API and hardware is defined by the instruction format (See 3.5.1) and the bus driver. The interface offered by the testing environment is presented in Chapter 5.

## 3.1 Target Platform and Core Selection

#### 3.1.1 FPGA Platform

The hardware implementation of the WFIFO concept was designed for an FPGA platform. It is also possible to use the WFIFO concept in an ASIC, but the fact that the WFIFO architecture depends on the implemented algorithm makes an FPGA implementation more reasonable. An other reason for selecting an FPGA is the available software. Most FPGA providers offer a good software bundle that also includes an IP library for very low costs. A disadvantage of using FPGAs is that the hardware design becomes dependant on the target platform. For example, when designing a new IP, it is not enough to write the VHDL code. The software used for system design and FPGA mapping needs additional data about the new IP. The format and the content of these data depends on the software used. Another point is that certain components from the IP library like the processors are only available in a precompiled version that can not be used for other FPGAs. All of this makes it difficult to migrate the design to a platform of a different provider.

The requirements when selecting the FPGA for the WFIFO design were that an IP library must be available that includes processor cores and that it is possible to map a couple of them on the FPGA. ML300 Evaluation Platform from Xilinx with a Virtex-II chip was selected. ISE and EDK version 7.1 were used as design software. The most important software was the EDK which includes a big library of IPs and the application XPS Studio. With XPS Studio all steps of the design flow can be done. First, the system can be assembled and configured using the IPs from the EDK library. Then, application code for the processors can be added and compiled. And finally, XPS can generate a simulation model for Modelsim or it can generate the bitmap used for programming the FPGA. A total of four IPs were designed for this project. All of them are compliant with the standard of the XPS IP library. This makes it possible to assemble and simulate a complete WFIFO architecture with XPS Studio.

#### 3.1.2 Processor and Bus Selection

The first step in hardware design was to select those processors and buses from the IP library that are best for the WFIFO architecture. The library includes two processor types, the Micro Blaze and the Power PC. Table 3.1 shows the buses of these processors that can be used for attaching a WFIFO.

| Processor Type | Bus Name | Address Width | Data Width   | Throughput          |

|----------------|----------|---------------|--------------|---------------------|

| PPC            | PLB      | 32-bit        | 64 or 32-bit | 1600MB/s            |

| MB             | LMB      | 32-bit        | 32-bit       | $500 \mathrm{MB/s}$ |

| MB, PPC        | OPB      | 32-bit        | 32-bit       | $500 \mathrm{MB/s}$ |

Table 3.1: Interfaces of PPC and MB

The only differences of interest between MB and PPC are the computing power and the maximum data rates. Thats why it is not possible to make a decision between them without knowing the requirements of the implemented algorithm. But for the target platform used, the Micro Blaze is the only feasible solution because the ML300 board can only hold a single PPC. Since the WFIFO architecture uses several processors in most cases, PPC can not be used. However, it would be nice if the designed WFIFO IP could also be used together with Power PC processors as soon as a bigger FPGA is available.

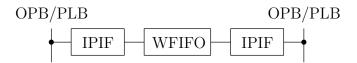

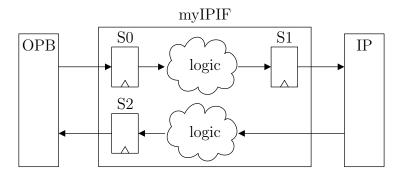

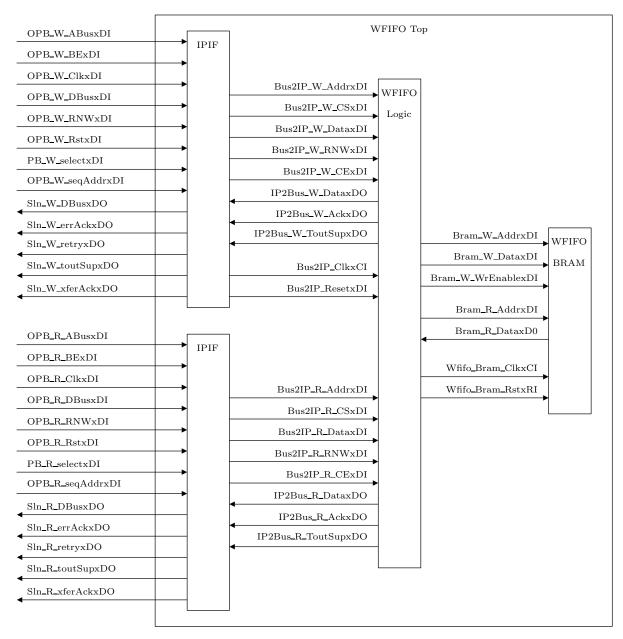

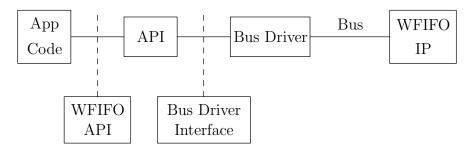

The problem when designing an IP for both MB and PPC is that the only bus type supported by both processors is the OPB bus. This is a good solution for MB processors but with PPC processors it is not possible to benefit from the higher data transferrate that is supported. One could design the WFIFO IP for the PLB bus and use an OPB to PLB bridge to connect with the MB. This approach has the disadvantage that an extra bus and bridge is required for each MB processor which increases chip size. Such a bridge does also increase the latency and reduces the system's performance. This is why another concept was preferred. The implementation made uses an extra IP called IPIF to connect the WFIFO to the bus (See Figure 3.2). The IPIF offers a standardised IP interface at one side and a specific bus interface at the other side. With such a design it is possible to connect the same IP to different bus types by using different IPIF implementations. Since the interface for the IP is the same for all bus types, it is not necessary to change it. The EDK library offers IPIF implementations for OPB and PLB bus. This was the reason to use the OPB bus instead of the LMB for the Micro Blaze. The LMB bus is used to connect the local instruction and data memory of the processor.

Figure 3.2: WFIFO implementation with IPIF bus adaptors.

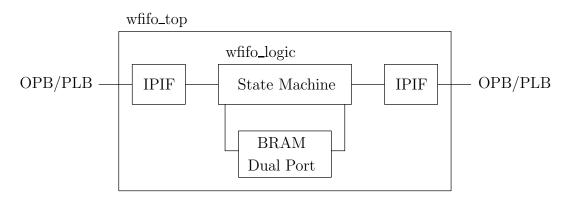

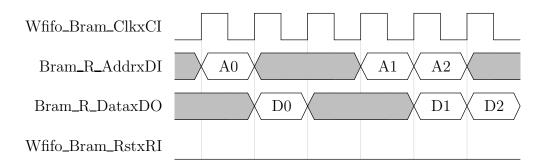

## 3.2 WFIFO Overview

Figure 3.3 gives an overview of the WFIFO architecture. The IP consists of two IPIFs, a dual port BRAM and the state machine. The IPIF first was taken from the EDK library but a reimplementation was required because the original included too many design errors (See 3.8). The memory is built from a set of BRAMs. To simplify the usage, different memory configurations have been integrated in a BRAM entity. Section 3.4 gives a short description of the BRAM entity. The interface to the state machine and the access rules are described in 3.7.2. The state machine is the heart of the WFIFO implementation. Its description is divided up in several sections. First, the interface and the instruction format used for the bus protocol are defined in 3.5.1. Details of the state machine are presented in 3.3 and the structure of the VHDL implementation is discussed in 3.7.6.

Figure 3.3: WFIFO architecture overview

#### 3.2.1 Requirements and Problem Description

This section list the requirements and the most important points to discuss for the WFIFO implementation.

- **Simultaneous R/W:** Die WFIFO IP is connected to two different buses. From one bus it receives the read instructions and from the other one the write instructions. The IP must be designed to support simultaneous read and write. At the same time it must guarantee that no conflicts in data access occur. This problem was solved with an adequate state machine architecture and memory management.

- **Bus interface definition:** In the WFIFO concept, only the API is defined. For the IP, design a bus protocol and an instruction format must be defined that allow an efficient API implementation.

- **Minimum latency:** The WFIFO IP must be designed for minimum latency because this has major impact on the performance of the entire system.

- **Protocol violations:** In the WFIFO protocol it was not defined how the buffer reacts if the protocol is violated. Such violations can be treated by the API software or by the hardware. If implemented in hardware an error signalling concept must be defined.

- **Easy to use:** The WFIFO IP should be easy to use but flexible in application. This was reached by integrating the entire WFIFO including the IPIF adaptors and the memory in a single IP. This IP can be configured with design parameters (See 3.6).

- **DFT:** The WFIFO IP must offer an interface that allows the testing of its functionality in an efficient way. This was considered in the error signalling concept and a software reset was added to make testing more efficient.

## 3.3 WFIFO State Machine

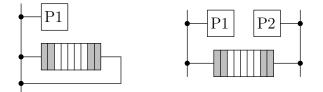

#### 3.3.1 Single and Dual Bus Application

The WFIFO has two different applications. Either it is used as a dual bus IP or as a single bus IP. Single bus means that both ports of the WFIFO are connected to the same bus. In

Figure 3.4: Single and dual bus WFIFO.

the dual bus case it is connected to two different buses (see Figure 3.4). This difference also has an impact on the design of the state machine. In the dual bus version it is possible that two requests arrive at the same time. In this case the state machine has to react to two commands at the same time. Furthermore it must be ensured that the two commands do not affect each other in a way not permitted. In the single bus version it depends on the bus type if two requests may arrive at the same time. The PLB bus allows simultaneous read and write, whereas the OPB does not. To keep things simple, an IP that is suitable for both cases was implemented. This results in an IP that is not optimal for the single bus application on the OPB bus but it can be used for all of the proposed applications. As will be seen later, this is not a disadvantage in terms of timing and throughput.

An implication of this architecture is that in the single bus application read and write access must be sent to different ports (different address ranges). The required address range of the single bus version is twice as large as for an IP optimised for the OPB bus. This is acceptable since the single bus application is assumed to be less important than the dual bus application.

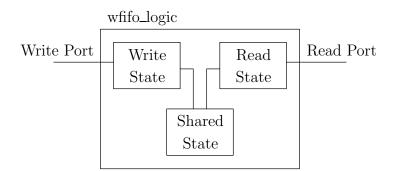

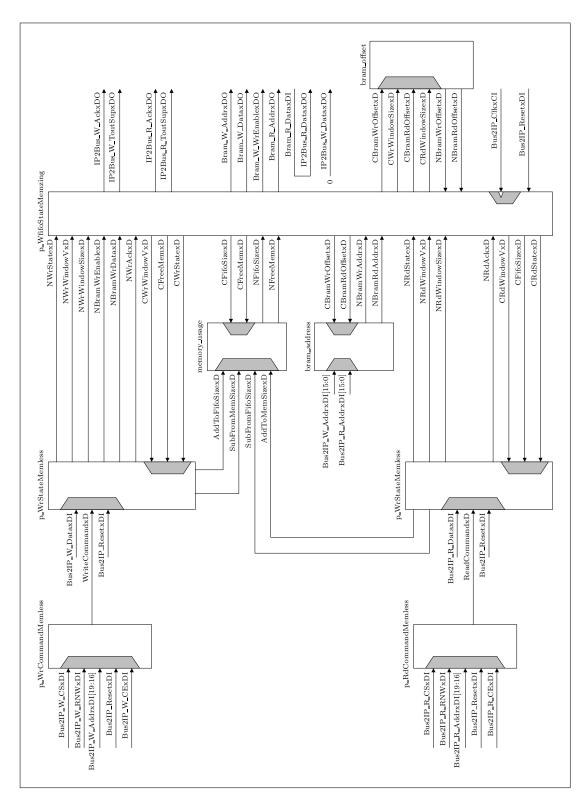

#### 3.3.2 WFIFO State Machine Architecture

For the architecture of the state machine, an implementation with two synchronised state machines is used (see Figure 3.5). One state machine is connected to the write port and handles all write commands, the other one does the same for the read port. Synchronisation is done over a set of shared states. From the functional point of view, an architecture with two synchronised state machines is not better than an architecture with a single state machine. But the version with two state machines is easier to specify and to implement. The reason for this is that the implementation with the single state machine not only has to encode all possible read and write states but also all possible combinations of them. Therefore it can even be assumed that the implementation with two state machines is more efficient in terms of chip size, because less bits are used to encode the states.

Figure 3.5: WFIFO state machine architecture

#### 3.3.3 Protocol Violations

The WFIFO concept only defines the WFIFOs behaviour in case the used instructions follow the protocol correctly. Examples of protocol violations are writing before acquiring or reading with an offset bigger than the acquired window. In such situations it must be ensured that the buffer is not set into an invalid or unknown state. There are two possibilities to address this problem. The first is to make sure that the WFIFO hardware never receives instructions violating the protocol. This can be done with a checking mechanism in the API. The second one is to design the WFIFO IP in a robust way that checks for protocol violations and rejects incorrect instructions. For the WFIFO design, the second solution was selected because it reduces the latency. Checking within the API does always need additional clock cycles, whereas checking can be implemented more efficiently in hardware. On the other hand, the hardware solution must pay attention to the design for testability.

The testing infrastructure used for the WFIFO design can access the WFIFO hardware only via the API. To test whether the WFIFO rejects incorrect instructions, rejection must be signalled to the API. To submit this status information, it is possible to use the error signal line of the bus or an extra bus transaction. Although the solution with the error signal seems to be faster at first sight, the solution with the extra bus transaction was chosen. The problems for an implementation using the error signal line are presented in 4.3.

The concept selected to detect protocol violations has impact on the state machine design. First, the state machine must check all incoming requests whether they are compliant with the protocol, and second it must support an additional state to read the status information.

#### 3.3.4 WFIFO States

Figure 3.6 shows the timing diagram for executing a WFIFO instruction. The incoming instruction is checked for correctness in the same clock cycle it arrives and is executed in the next clock period. With this solution, the buffer needs only two clock cycles to execute an instruction. Exceptions are the data read instruction that takes two clock cycles and the blocking acquiring in case that the WFIFO has to wait for data or free memory. For the total execution time, the time for bus transfer and pipelining in IPIF must be added. Table 4.5 gives an overview of the total execution times.

Figure 3.6: Timing diagram for WFIFO instructions. For the read data operation the function state takes two clock cycles.

This section presents the states of the read and write state machine and a simplified state transition function. A more detailed but also more abstract description of the state transitions is given in 3.7.4.

#### **WFIFO Write States and Transitions**

| Write State           | Shortcut | Function                                                                                                                                                                                                               |

|-----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle State            | WrIdle   | WFIFO is waiting for the next write function call.                                                                                                                                                                     |

| Acquire Write Ack     | AcWrAck  | WFIFO executes an acquire write operation and<br>signals acknowledge to the calling process. The<br>write function status is set to OK.                                                                                |

| Acquire Write Blocked | AcWrBlk  | WFIFO is waiting until free memory is big enough<br>for an acquire write operation.                                                                                                                                    |

| Acquire Write Failed  | AcWrFail | WFIFO is not able to execute a non-blocking ac-<br>quiring operation because there is not enough free<br>memory. Acknowledge is signalled to the calling<br>process and the write function status is set to<br>FAILED. |

| Release Write Ack     | ReWrAck  | WFIFO executes a release write operation and sig-<br>nals acknowledge to the calling process. The write<br>function status is set to OK.                                                                               |

| Write Data Acl        | WrDaAck  | WFIFO writes data to its memory and signals ac-<br>knowledge to the calling process. The write func-<br>tion status is set to OK.                                                                                      |

| Error State           | WrErr    | The last instruction received was incorrect. The instruction is not executed and the write function status is set to ERROR.                                                                                            |

| Write Status Ack      | WrStaAck | The current write function status can be read from<br>the data bus and acknowledge is signalled to the<br>calling process.                                                                                             |

**Table 3.2:** WFIFO write states. The write function status indicates the success of the last instruction. It can have the values OK, ERROR and FAILED.

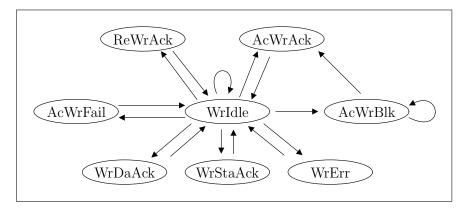

Figure 3.7: WFIFO state transition of the write state machine. The figure shows all possible transitions. The conditions for the transitions are listed in Table 3.3.

| Current State                             | Next State | Condition                                                                                                                              |  |

|-------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| WrIdle                                    | WrIdle     | No WFIFO write instruction received.                                                                                                   |  |

|                                           | WrErr      | The received instruction violates the WFIFO protocol.                                                                                  |  |

|                                           | AcWrAck    | The WFIFO receives a correct acquire write instruction and<br>the free memory is big enough for the acquiring.                         |  |

|                                           | AcWrBlk    | The WFIFO receives a correct and blocking acquire write in-<br>struction but the free memory is not big enough for the ac-<br>quiring. |  |

| AcWrFail The WFIFO re-<br>instruction but |            | The WFIFO receives a correct and non-blocking acquire write<br>instruction but the free memory is not big enough for the<br>acquiring. |  |

| ReWrAck The W<br>tion.                    |            | The WFIFO receives a correct release write window instruc-<br>tion.                                                                    |  |

|                                           | WrDaAck    | The WFIFO receives a correct data write instruction.                                                                                   |  |

|                                           | WrStaAck   | The WFIFO receives a correct status signal report instruction.                                                                         |  |

| WrErr<br>AcWrAck                          | WrIdle     | Transition occurs in any case.                                                                                                         |  |

| AcWrFail                                  |            |                                                                                                                                        |  |

| ReWrAck                                   |            |                                                                                                                                        |  |

| WrDaAck                                   |            |                                                                                                                                        |  |

| WrStaAck                                  |            |                                                                                                                                        |  |

| AcWrBlk                                   | AcWrBlk    | There is still not enough free memory for the acquire opera-<br>tion.                                                                  |  |

|                                           | AcWrAck    | Now there is enough free memory.                                                                                                       |  |

**Table 3.3:** WFIFO write state transitions.

### WFIFO Read States and Transitions

| Read State              | Shortcut | Function                                                                                                                                                                                                                                 |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle State              | RdIdle   | WFIFO is waiting for the next read function call.                                                                                                                                                                                        |

| Acquire Read Ack        | AcRdAck  | WFIFO executes an acquire read operation and<br>signals acknowledge to the calling process. The<br>read function status is set to OK.                                                                                                    |

| Acquire Read Blocked    | AcRdBlk  | WFIFO is waiting until enough data is available from the internal FIFO buffer.                                                                                                                                                           |

| Acquire Read Failed     | AcRdFail | WFIFO is not able to execute a non-blocking ac-<br>quiring operation because there are not enough<br>data in the internal memory. Acknowledge is sig-<br>nalled to the calling process and the read function<br>status is set to FAILED. |

| Release Read Ack        | ReRdAck  | WFIFO executes a release read operation and sig-<br>nals acknowledge to the calling process. The read<br>function status is set to OK.                                                                                                   |

| Read Data OK            | RdDaOk   | To execute the read instruction, the WFIFO needs<br>two states. In the OK state it provides the memory<br>with the read address.                                                                                                         |

| Read Data Ack           | RdDaAck  | The data can now be read from the data bus. The WFIFO signals acknowledge to the calling process and the read function status is set to OK.                                                                                              |

| Error State             | RdErr    | The last instruction received was incorrect. The instruction is not executed and the write function status is set to ERROR.                                                                                                              |

| Read Status Acknowledge | WrStaAck | The current read function status can be read from<br>the data bus and acknowledge is signalled to the<br>calling process.                                                                                                                |

Table 3.4: WFIFO read state

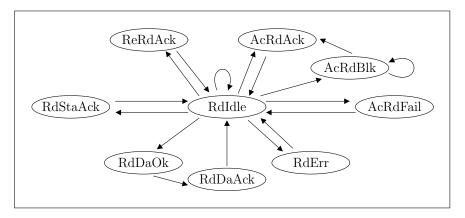

Figure 3.8: WFIFO state transition of the read state machine.

| Current State | Next State | Condition                                                                                                                                    |  |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| RdIdle        | RdIdle     | No WFIFO read instruction received.                                                                                                          |  |

| RdErr         |            | The received instruction violates the WFIFO protocol.                                                                                        |  |

|               |            | The WFIFO receives a correct acquire read instruction and<br>there are enough data in the FIFO buffer for acquiring.                         |  |

|               | AcRdBlk    | The WFIFO receives a correct and blocking acquire read in-<br>struction but there are not enough data in the FIFO buffer<br>for acquiring.   |  |

|               | AcRdFail   | The WFIFO receives a correct and non-blocking acquire read<br>instruction but there are not enough data in the FIFO buffer<br>for acquiring. |  |

|               | ReRdAck    | The WFIFO receives a correct release read window instruc-<br>tion.                                                                           |  |

|               | RdDaOk     | The WFIFO receives a correct data read instruction.                                                                                          |  |

|               | WrStaAck   | The WFIFO receives a correct status signal report instruction.                                                                               |  |

| RdErr RdIdle  |            | Transition occurs in any case.                                                                                                               |  |

| AcRdAck       |            |                                                                                                                                              |  |

| AcRdFail      |            |                                                                                                                                              |  |

| ReRdAck       |            |                                                                                                                                              |  |

| RdDaAck       |            |                                                                                                                                              |  |

| WrStaAck      |            |                                                                                                                                              |  |

| RdDaOk        | RdDaAck    | Transition occurs in any case.                                                                                                               |  |

| AcRdBlk       | AcRdBlk    | There are still not enough data in the FIFO buffer for acquiring.                                                                            |  |

|               | AcRdAck    | Now there are enough data in the FIFO buffer.                                                                                                |  |

Table 3.5:WFIFO read state transitions.

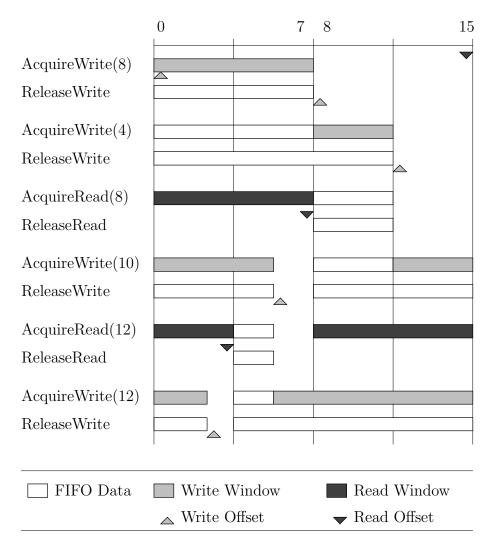

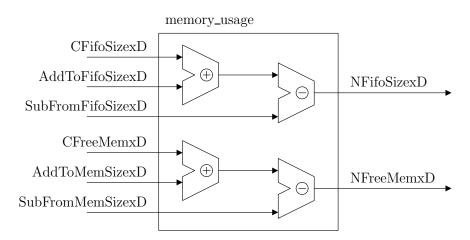

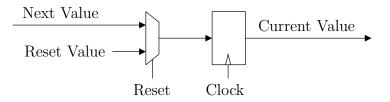

#### 3.3.5 Memory Management

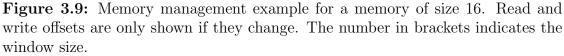

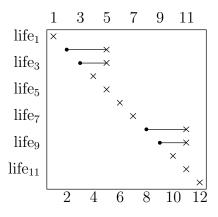

Since the WFIFO is implemented with a single memory block, a memory management is required. In the BRAM memory, there are four distinguishable regions: read window, write window, FIFO data and free memory. The size of these regions changes dynamically and every memory cell belongs to one of these regions. There are different options to map the regions to the BRAM. In this implementation a circular concept is used. Figure 3.9 shows how the size and the position of the four regions change while executing an example code sequence.

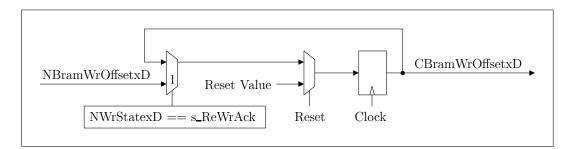

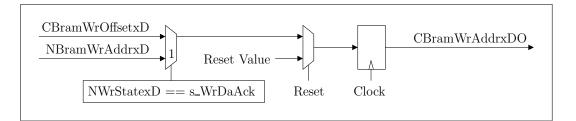

#### Address Translation

The address is calculated by adding the address passed by the instruction and the offset value. If the resulting value extends the address range defined by the BRAM size, the address is translated to the beginning of the BRAM memory by a modulo operator.

BramWrAddrxD = mod(BramWrOffsetxD + WrAddrxDI, BramSize)BramRdAddrxD = mod(BramRdOffsetxD + RdAddrxDI + 1, BramSize)

#### Offset Updating

The read and write offset are updated whenever a read or write window is released. When a write window is released, the occupied memory region is added to the FIFO data. When a read window is released, the memory region is added to the free memory. During read and write operations, the offset values are used to calculate the target address. During the rest of the time, the input address is set to zero and the offset serves as a dummy read address for the BRAM. The read and write BRAM address must never have the same value. This is ensured by setting the read offset one position before the next read window. In case there are no read or write windows but a maximum of FIFO data, two memory locations must be reserved for the offset pointers. Therefore, the maximum amount of data that can be written to the buffer is the BRAM size minus two. It is also possible to implement a memory management that uses only one empty address, but more complex state machines are required.

### 3.4 WFIFO Memory

The WFIFO memory is implemented with BRAM blocks. A BRAM is a parameterisable memory module that is available on all newer Xilinx FPGAs. The BRAM has two independent access ports. Simultaneous reading or writing on both ports is possible. The only limitation is that simultaneous access must address two different memory locations. Usually one BRAM memory is built up from a set of smaller BRAM blocks. The number of these sub-blocks and how they are connected depends on the required memory size. To hide this from the state machine, the different memory configurations are placed in a WFIFO BRAM entity that offers a memory-size-independent interface for the state machine. The IO signals of the BRAM entity and access rules are described in 3.7.2.

The total memory size is a parameter that is set during architecture design. Depending on the required data scheduling, there is a lower bound for this design parameter and it is the designer's responsibility to select this parameter properly. How the minimum memory size can be calculated is shown in section 7.5.

# 3.5 Bus Driver Interface

The physical interface between WFIFO IP and processor is a bus that includes an address and a data line and a set of transfer qualifier signals. This section describes the instruction format used on address and data bus. First the implemented format is shown, then it is discussed why this format was selected.

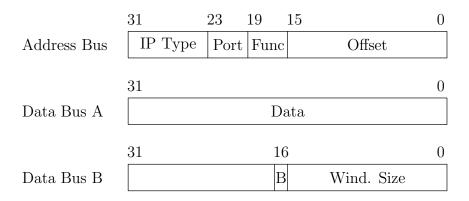

### 3.5.1 Implemented Instruction Format

Figure 3.10: WFIFO bus interface instruction format. For the data bus, two different formats are used: A for data transfer and B for the other instructions.

| Name    | Size (bit) | Range/Value   | Function                                              |  |  |  |

|---------|------------|---------------|-------------------------------------------------------|--|--|--|

| IP Type | 8          | 0x01          | The IP type is used to separate the address range     |  |  |  |

|         |            |               | of the WFIFO IP from other IPs. IP type for           |  |  |  |

|         |            |               | WFIFO IPs is one.                                     |  |  |  |

| Port    | 4          | 0x0-0xF       | The port number is used to identify the target        |  |  |  |

|         |            |               | WFIFO. If a WFIFO connects both read and write        |  |  |  |

|         |            |               | port to the same bus, two different port numbers      |  |  |  |

|         |            |               | must be used.                                         |  |  |  |

| Inst.   | 4          | 0x1-0x6, 0xF  | Instruction ID identifies the instruction to execute. |  |  |  |

|         |            |               | 1 Read                                                |  |  |  |

|         |            |               | 2 Write                                               |  |  |  |

|         |            |               | 3 Acquire Read                                        |  |  |  |

|         |            |               | 4 Acquire Write                                       |  |  |  |

|         |            |               | 5 Release Read                                        |  |  |  |

|         |            |               | 6 Release Write                                       |  |  |  |

|         |            |               | 7 Status                                              |  |  |  |

|         |            |               | F Mir/Reset                                           |  |  |  |

| Offset  | 16         | 0x0000-0xFFFF | Offset address for reading and writing to the         |  |  |  |

|         |            |               | WFIFO window.                                         |  |  |  |

Table 3.6: Instruction format address bus.

| Name        | Size (bit) | Range         | Format | Function                                          |

|-------------|------------|---------------|--------|---------------------------------------------------|

| Data        | 32         | all           | А      | Data for read and write.                          |

| Window Size | 16         | 0x0000-0xFFFF | В      | Window size for acquiring.                        |

| Blocking    | 1          | 0x10000       | В      | One for blocking, zero for non blocking acquring. |

Table 3.7: Instruction format data bus

#### 3.5.2 Instruction Format Evaluation

There are different possibilities for the bus transaction format. An implementation with a single instruction type format was selected because this simplifies the API implementation and the hardware design. To make a decision for the instruction format, Table 3.8 was used. This table lists all the information that must be transferred.

| Item Name      | Size    | Address | Data |

|----------------|---------|---------|------|

| Instruction ID | 4 bit   | yes     | yes  |

| Port number    | sizeP   | yes     | no   |

| Window size    | sizeW   | yes     | yes  |

| Offset         | sizeW   | yes     | yes  |

| Data           | 32 bit  | no      | yes  |

| IP type        | 4-8 bit | yes     | no   |

Table 3.8: Items to include in the instruction format with required size and possible bus selection.

For the size of the instruction ID, four bits are proposed. With four bits, sixteen different instructions are possible. Currently only eight are used and therewith it offers enough room for an extension of the API. The IP type is used to separate the address range of the WFIFO form other IPs connected to the same bus. Port number and IP type cannot be transfered by the data bus because they are used to identify the target WFIFO.