# High Availability Seamless Ring Protocol

# Implementation in FPGA

Xiaozhuo Jiang

Master Thesis 2009, February 13

Advisor ABB: Prof. Dr. Hubert Kirrmann Co-Advisor ABB: Dr. Jean-Charles Tournier Supervisor ETH: Prof. Dr. Lothar Thiele

Computer Engineering and Networks Laboratory, ETH Zurich

#### Abstract

The IEC committee SC65 WG15 "Highly Available Automation Networks" published the IEC standard 62439 in 2008 to provide several redundancy methods to overcome the lack of a commonly accepted redundancy solution in Industrial Ethernet. As one of these methods, the Parallel Redundancy Protocol (PRP) IEC62439 Clause 6 relies on the parallel operation of two local area networks, and provides completely seamless switchover in case of failure of links or switches, thus fulfilling all the hard real-time requirements of substation automation. The High Availability Seamless Ring (HSR) which is proposed in IEC 62439-3 applies the PRP principle to build a simple seamless ring by treating each direction as a separate network.

One main application of the HSR is the process bus in the substation automation network as specified in the IEC 61850 standard. This application is characterized by heavy traffic, real-time communication and requirement of bumpless switchover in case of fault.

One challenging issue in HSR is to reject the duplicated frames coming from the both ports of a node and the frames circulating in the ring. The algorithm applied in PRP cannot be wholly transplanted into HSR because of HSR's ring topology. In this thesis three algorithms are proposed to solve the duplicated and circular frame discarding. The proposed algorithms are compared with the help of the software network model. One algorithm is chosen. By designing a switch structure with the integration of the chosen algorithm, the HSR protocol is implemented in FPGA.

| 1 | Introdu | ction                                                             | 7  |  |  |

|---|---------|-------------------------------------------------------------------|----|--|--|

|   | 1.1     | .1 Context                                                        |    |  |  |

|   | 1.2     | Motivation                                                        | 8  |  |  |

|   | 1.3     | Tasks                                                             | 9  |  |  |

|   | 1.4     | I.4 Contributions                                                 |    |  |  |

|   | 1.5     | Overview                                                          | 10 |  |  |

| 2 | The Hig | h Availability Seamless Ring                                      | 11 |  |  |

|   | 2.1     | The Topology of HSR                                               | 11 |  |  |

|   | 2.2     | The Network Management                                            | 12 |  |  |

|   | 2.3     | The Communication Rules of the Switch End Node in HSR             | 12 |  |  |

|   | 2.3.1   | Sending                                                           | 12 |  |  |

|   | 2.3.2   | 2 Receiving                                                       | 13 |  |  |

|   | 2.3.3   | Forwarding                                                        | 13 |  |  |

|   | 2.3.4   | Cut-through                                                       | 13 |  |  |

|   | 2.3.5   | Bad Frame Handling                                                | 14 |  |  |

|   | 2.4     | Frame Format for HSR                                              | 14 |  |  |

|   | 2.5     | The Node Structure and Operation in HSR                           | 15 |  |  |

|   | 2.6     | Duplicate Handling                                                | 16 |  |  |

|   | 2.1     | The Problem with the Drop Window Algorithm in HSR                 | 17 |  |  |

| 3 | The Pro | oposed Solutions for Rejecting the Duplicated and Circular Frames | 18 |  |  |

|   | 3.1     | General Principle                                                 | 18 |  |  |

|   | 3.2     | Algorithm 1: Circular Buffer                                      | 19 |  |  |

|   | 3.3     | Algorithm 2: Hash Table with Open Addressing and Aging            | 21 |  |  |

|   | 3.3.1   | Why Open Addressing                                               | 21 |  |  |

|   | 3.3.2   | Open Addressing Algorithm and its Constraints                     | 21 |  |  |

|   | 3.3.3   | Open Addressing With Aging                                        | 22 |  |  |

|   | 3.3.4   | Choose the Random Probe Sequence                                  | 26 |  |  |

|   | 3.3.5   | Randomization of the Un-uniform Distributed Keys                  | 27 |  |  |

|   | 3.3.6   | The Randomness of Double Hashing                                  | 28 |  |  |

|   | 3.3.7   | Memory Access Serialization                                       | 28 |  |  |

|   | 3.4     | Algorithm 3: Hashing Combined with Circular Buffer                | 30 |  |  |

|   | 3.5     | Comparison of the Proposed Solutions                              | 32 |  |  |

# CONTENTS

|   | 3.6 C    | Conclusion to the Proposed Solutions                           | 33 |

|---|----------|----------------------------------------------------------------|----|

| 4 | The Soft | vare Simulation of the Proposed Solutions                      | 34 |

|   | 4.1 T    | he Setup of the Simulation Environment                         | 34 |

|   | 4.1.1    | The Node Class                                                 | 34 |

|   | 4.1.2    | The Frame Structure                                            | 35 |

|   | 4.1.3    | Generating Nodes in the Ring                                   | 35 |

|   | 4.1.4    | The Frame Generator                                            | 36 |

|   | 4.1.5    | The Queue                                                      | 36 |

|   | 4.1.6    | The Lookup Tables                                              | 37 |

|   | 4.1.7    | The Receiving Processing                                       | 41 |

|   | 4.1.8    | Send Coordinator and Sending Port Use Count Down               | 41 |

|   | 4.1.9    | The Sending Port                                               | 43 |

|   | 4.1.10   | The Receiving Port                                             | 43 |

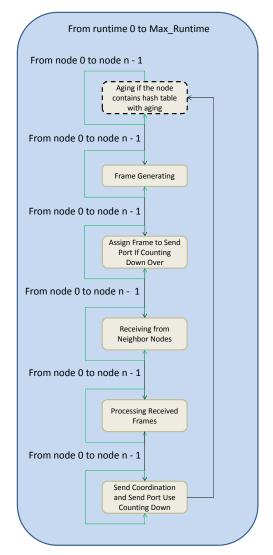

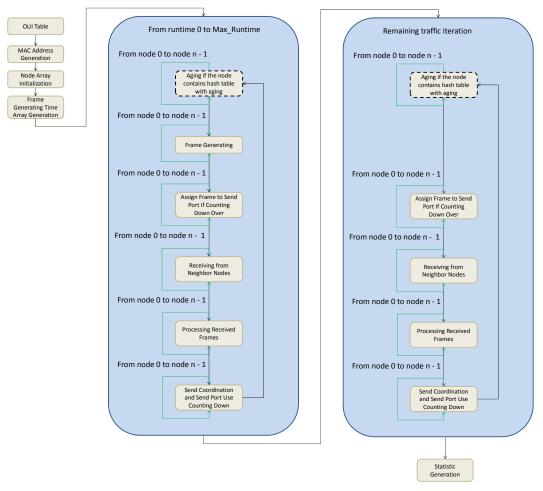

|   | 4.1.11   | Operation Parallelization and Simulation Process               | 43 |

|   | 4.2 S    | imulation Configuration                                        | 46 |

|   | 4.2.1    | Parameters Configuration                                       | 46 |

|   | 4.2.2    | Time Unit of the Simulation                                    | 49 |

|   | 4.2.3    | Simulation Methodology and Contents                            | 49 |

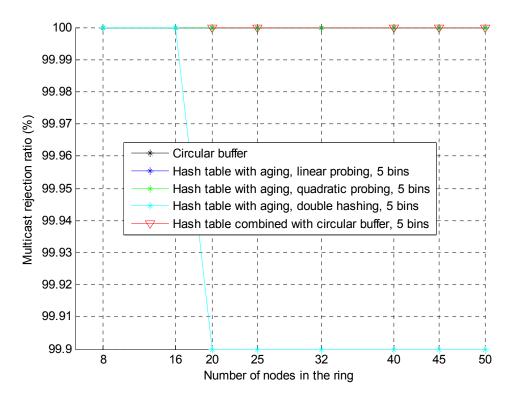

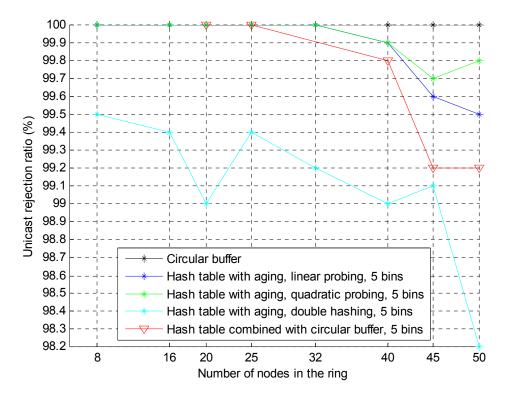

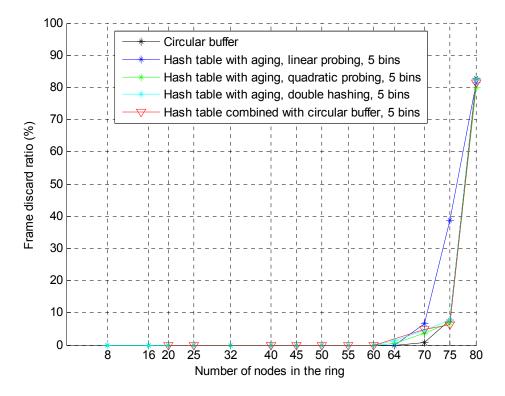

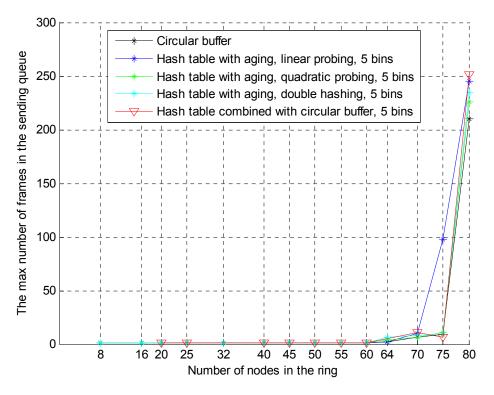

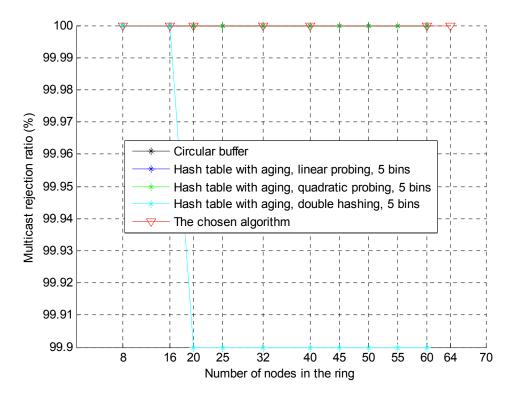

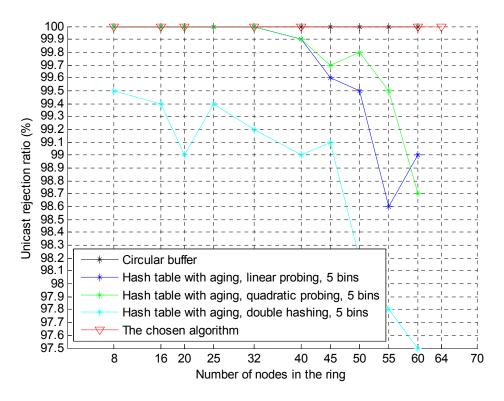

|   | 4.3 S    | imulation Results and Discussion                               | 51 |

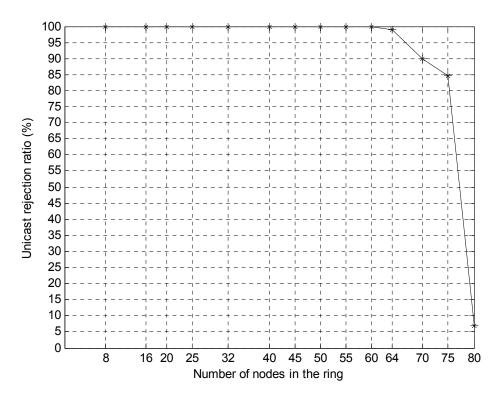

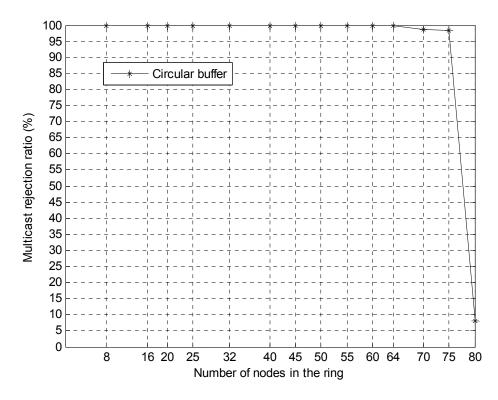

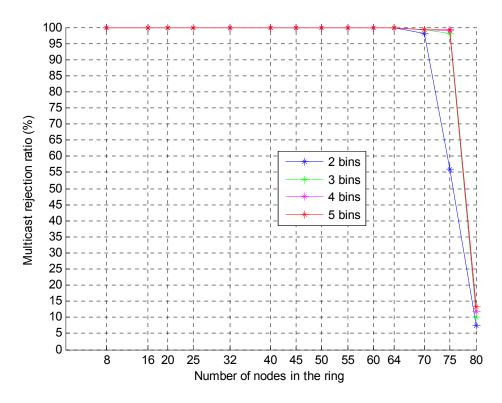

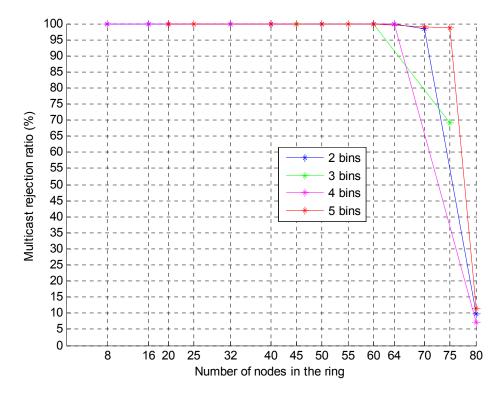

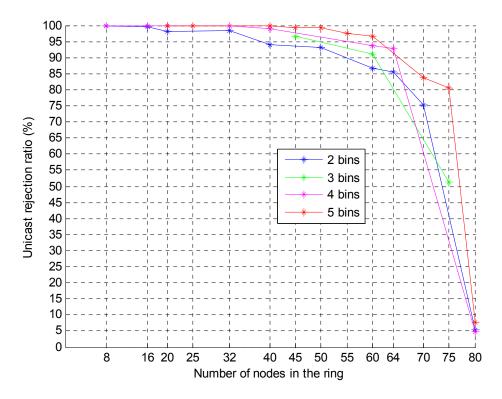

|   | 4.3.1    | The Simulation Results of Circular Buffer                      | 52 |

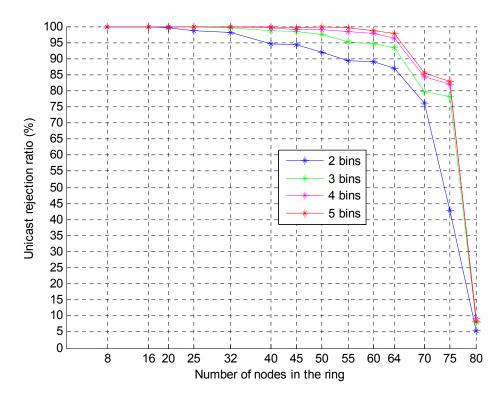

|   | 4.3.2    | The Simulation Results of Hash Table with Aging                | 54 |

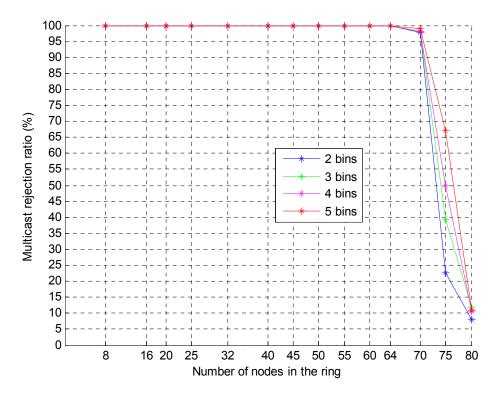

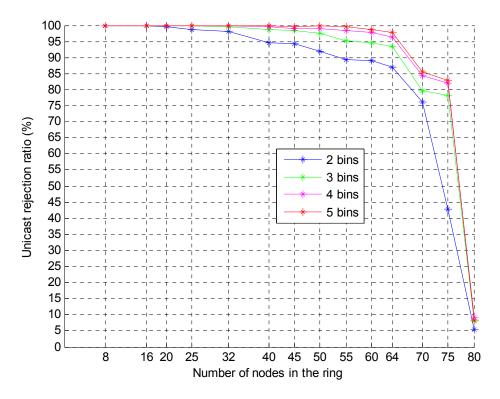

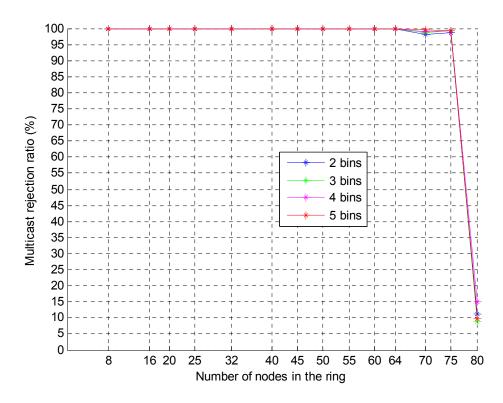

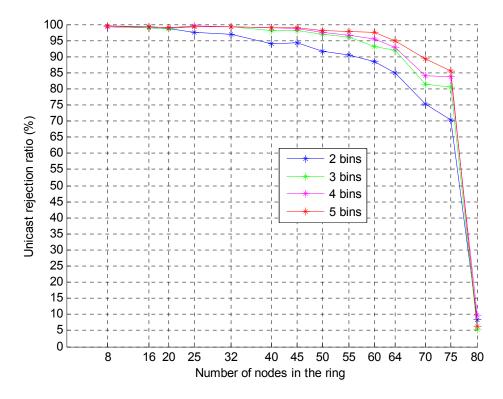

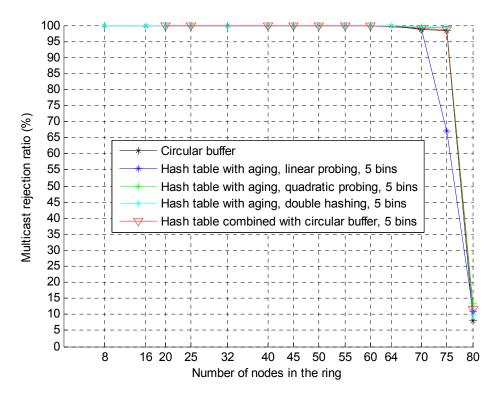

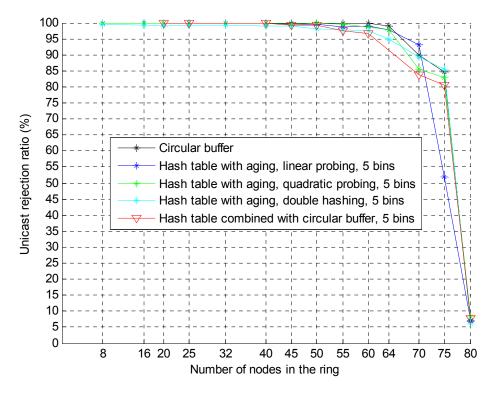

|   | 4.3.3    | Simulation Results of Hash Table Combined with Circular Buffer | 59 |

|   | 4.3.4    | Comparison of the Proposed Methods                             | 60 |

|   | 4.3.5    | Further Discussions                                            | 63 |

|   | 4.4 T    | he Chosen Algorithm and Modification                           | 67 |

|   | 4.4.1    | Choosing an Algorithm for Implementation                       | 67 |

|   | 4.4.2    | Modification before Implementation                             | 67 |

| 5 | FPGA Im  | plementation                                                   | 70 |

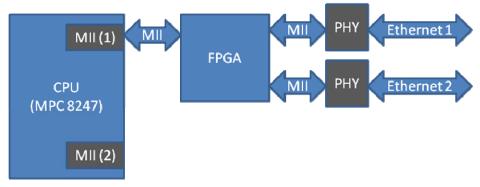

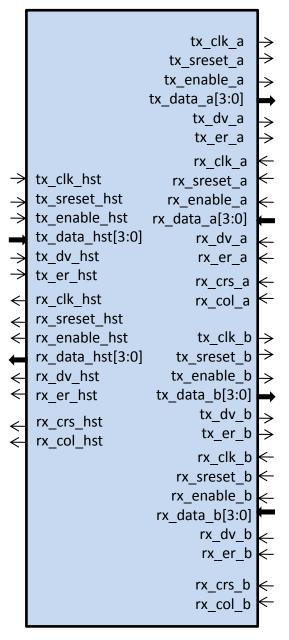

|   | 5.1 T    | he Hardware Platform and Interface                             | 70 |

|   | 5.2 D    | esign Process and Methodology                                  | 70 |

|   | 5.3 F    | unctional Design                                               | 71 |

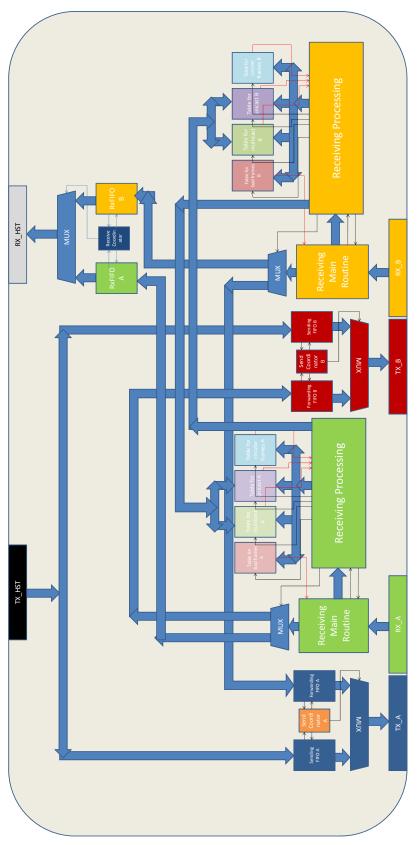

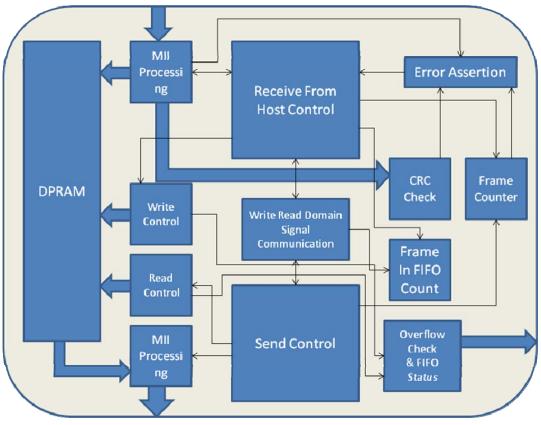

|   | 5.3.1    | An Overview of the Switch Element Structure                    | 71 |

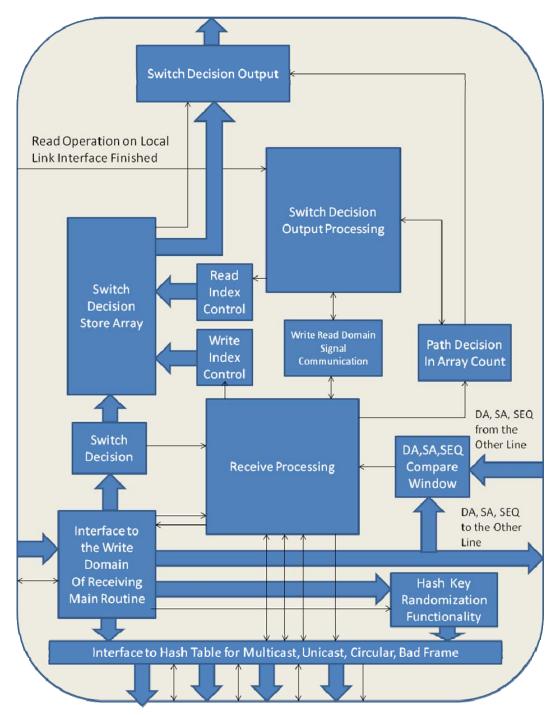

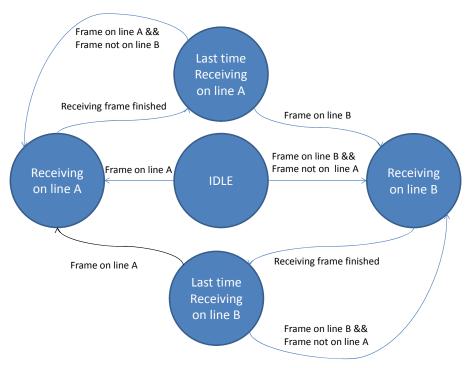

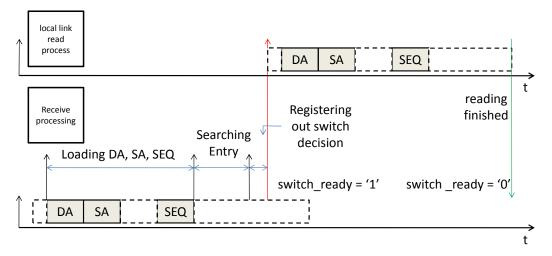

|   | 5.3.2    | The Receiving Main Routine                                     | 74 |

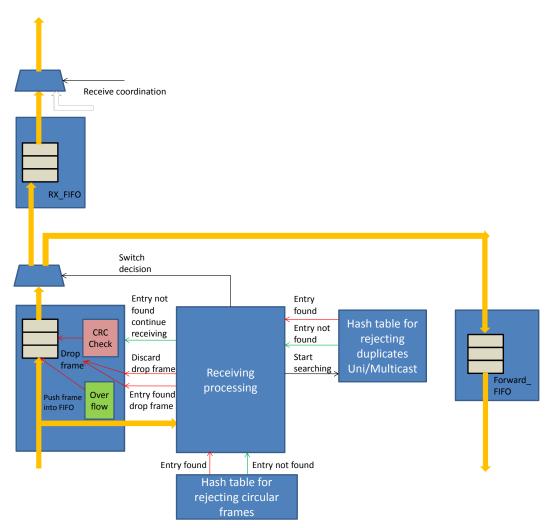

|    | 5.3.3      | The Receiving Processing                                         | 76  |

|----|------------|------------------------------------------------------------------|-----|

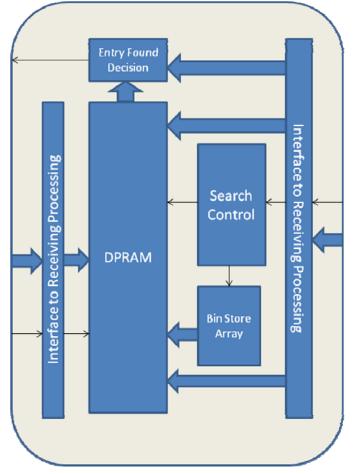

|    | 5.3.4      | Hash Table                                                       | 78  |

|    | 5.3.5      | Forwarding FIFO                                                  | 79  |

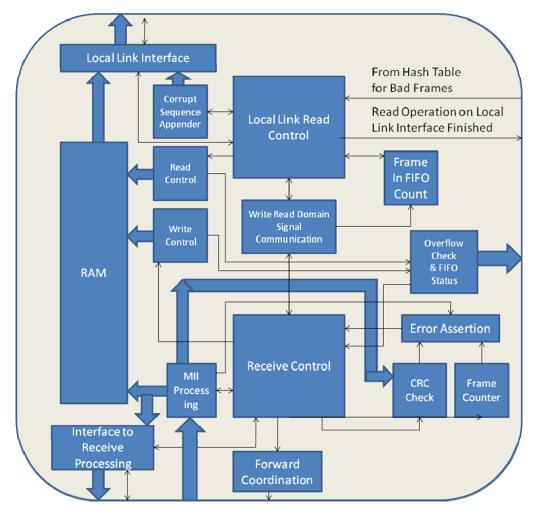

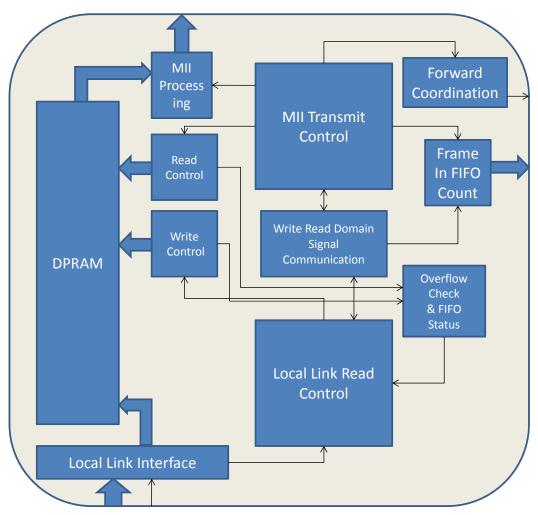

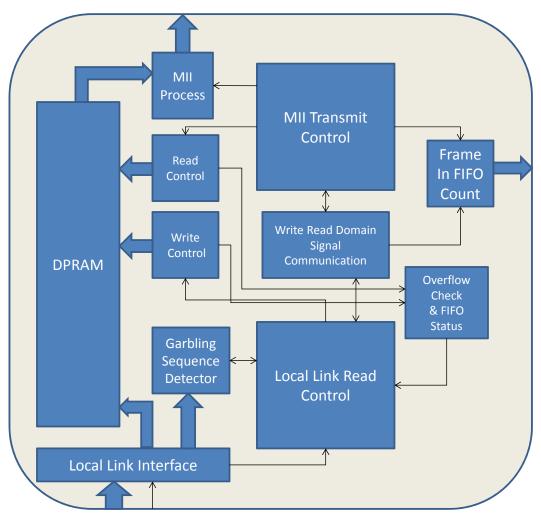

|    | 5.3.6      | RX_FIFO                                                          | 80  |

|    | 5.3.7      | TX_FIFO                                                          | 81  |

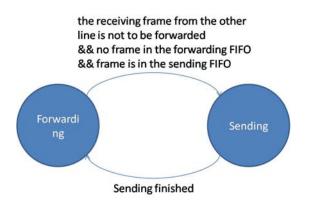

|    | 5.3.8      | Send Coordinator                                                 | 82  |

|    | 5.3.9      | Receive Coordinator                                              | 83  |

|    | 5.3.10     | Receiving Flow                                                   | 83  |

|    | 5.3.11     | Sending Flow                                                     | 83  |

|    | 5.4 F      | unctional Design Considerations                                  | 85  |

|    | 5.4.1      | Cut-through Implementation                                       | 85  |

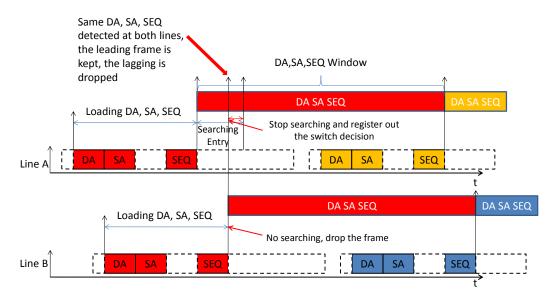

|    | 5.4.2      | DA, SA, SEQ Comparison Window                                    | 85  |

|    | 5.5 C      | esign Considerations about Timing                                | 86  |

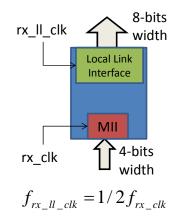

|    | 5.5.1      | Clock Cooperation between Lock Link Interface and MII Interfaces | 86  |

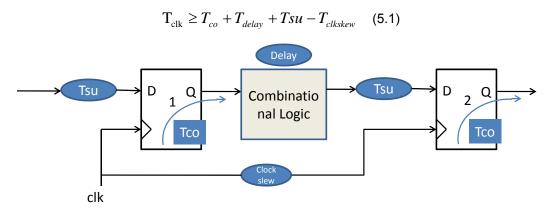

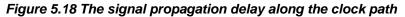

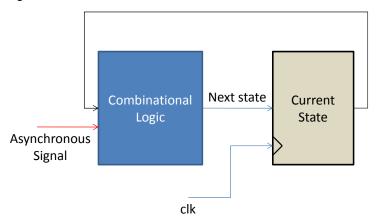

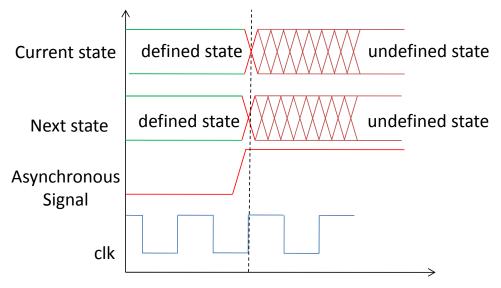

|    | 5.5.2      | The Critical Clock Path                                          | 87  |

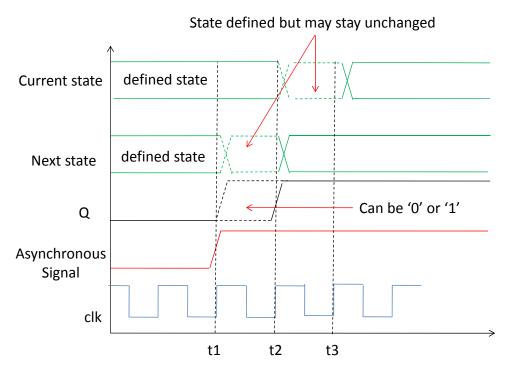

|    | 5.5.3      | Synchronization between Clock Domains                            | 88  |

|    | 5.6 S      | ynthesis and Evaluation of the Implemented Switch Element        | 91  |

|    | 5.6.1      | Synthesis                                                        | 91  |

|    | 5.7 E      | valuation                                                        | 92  |

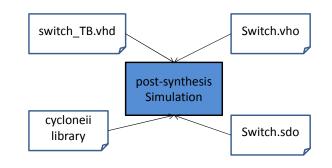

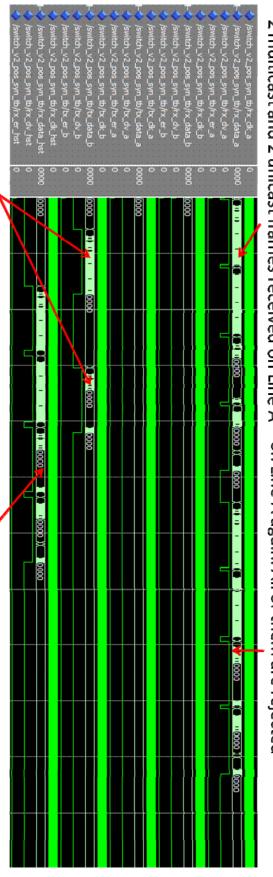

|    | 5.7.1      | Simulation Environment                                           | 92  |

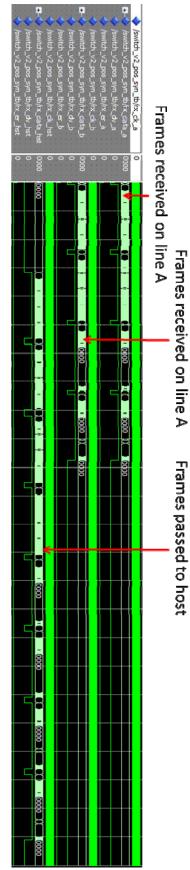

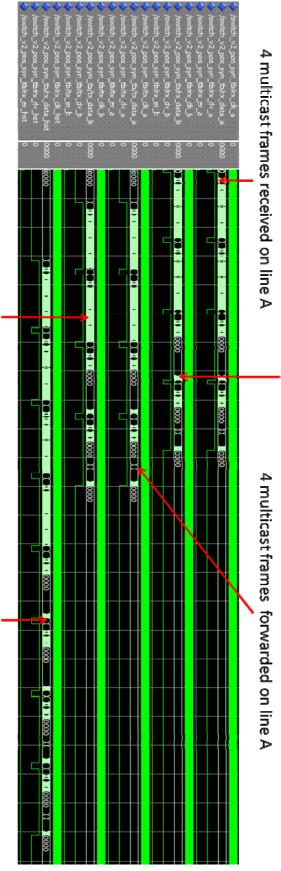

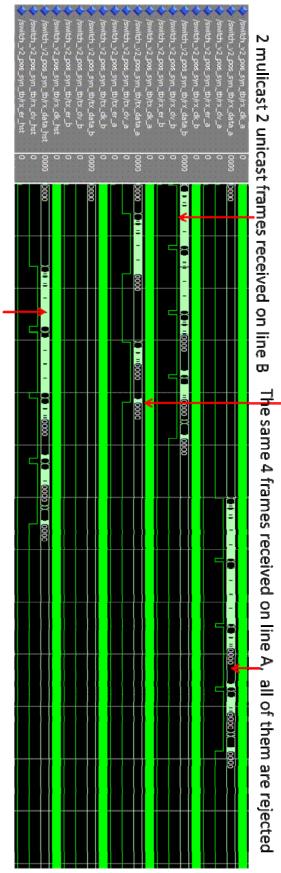

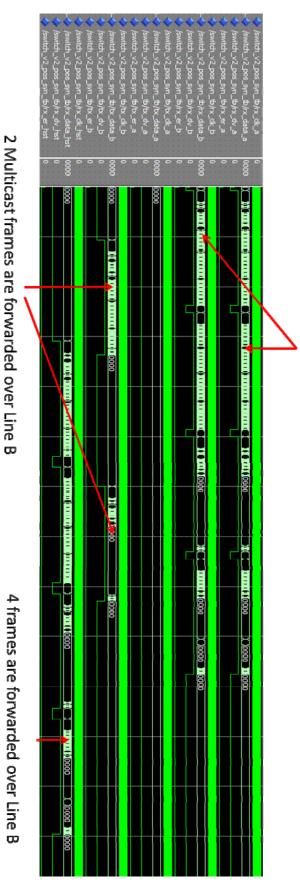

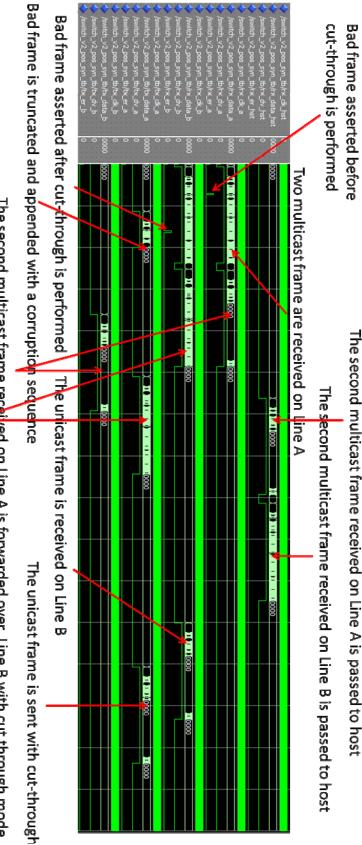

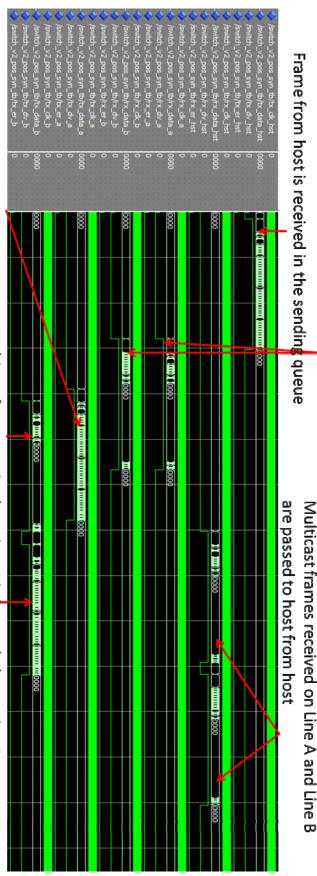

|    | 5.7.2      | Tested Functionalities                                           | 92  |

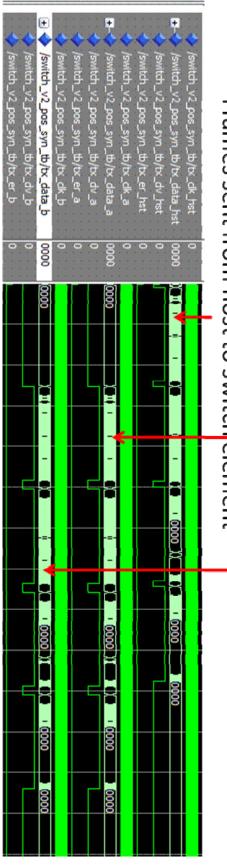

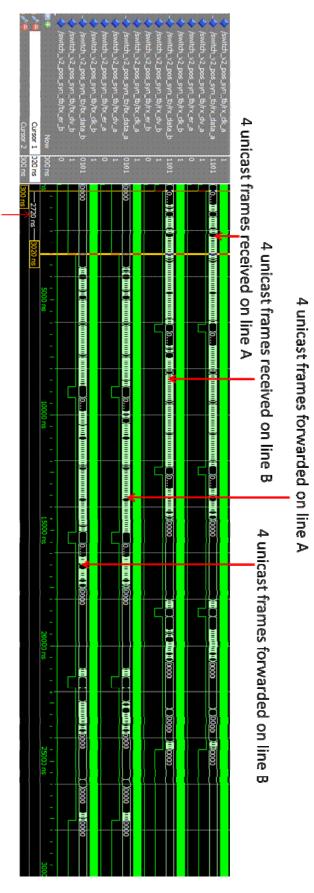

|    | 5.7.3      | Simulation Results                                               | 93  |

|    | 5.8 C      | onclusion of the FPGA Implementation                             | 105 |

| 6  | Conclusi   | ons and Future Work                                              | 106 |

|    | 6.1 C      | onclusions                                                       | 106 |

|    | 6.2 F      | uture Work                                                       | 107 |

| A  | ppendix A  | Abbreviations Used in the Thesis                                 | 108 |

| Bi | ibliograph | ıy                                                               | 109 |

# **1** Introduction

#### 1.1 Context

In April 2008 the IEC committee SC65 WG15 "Highly Available Automation Networks" published six industrial communication network protocols dedicated to provide the redundancy of the network. Among these 6 protocols, the Parallel Redundancy Protocol (PRP) has been selected for the IEC 61850 communication network within substations.

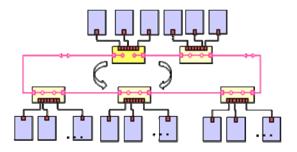

PRP applied the "redundancy in the nodes" method to offer the redundancy. Each PRP node (called a DANP or Doubly Attached Node with PRP) is attached to two independent LANs which may exhibit different topologies. The networks are completely separated and are assumed to be fail-independent. Figure 1.1 shows the topology of PRP.

Figure 1.1 An illustration of the PRP topology [1]

Compared to other protocols released in standard IEC62439, PRP provides completely seamless switchover in case of failure of links or switches, thus fulfilling all the hard realtime requirements of substation automation. Whereas other protocols like RSTP and MPR (Media Redundancy Protocol) need a recovery time [2].

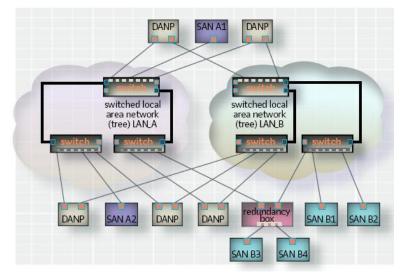

Since PRP requires doubling the network infrastructure, it overkills in some relative simple application scenarios. The High Availability Seamless Ring is proposed based on the PRP protocol (Figure 1.2). It allows a significant reduction of the hardware costs, since no switch is used, instead each end node must be equipped with a switch element to implement the ring protocol. Although the network layer and the algorithms in PRP and HSR are nearly the same, HSR cannot apply all the algorithms in PRP because of its ring topology and the application scenario of the HSR, which is characterized by high network traffic. Therefore additional features and modifications must be made to guarantee the performance of HSR. This becomes the motivation of this Thesis, which will be explained further in the next section.

Figure 1.2 An illustration of the HSR topology

# 1.2 Motivation

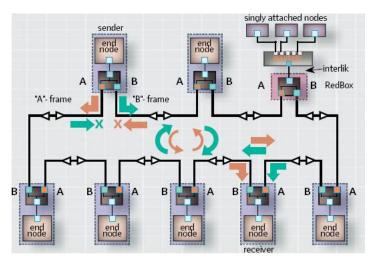

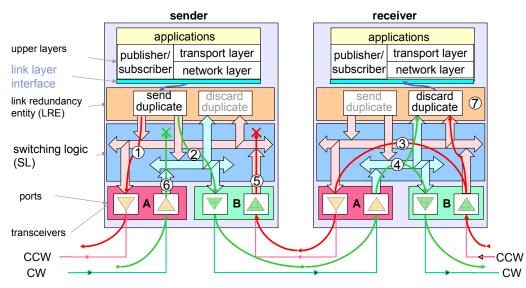

In PRP, an additional layer, the "Link Redundancy Entity" (LRE) (Figure 1.3) is placed under the link layer.

Figure 1.3 Location of the LRE in the network layer stack of PRP [3]

The LRE connects the upper layer and the two Ethernet controllers and behaves towards the upper layer like a single Ethernet interface. When transmitting, it appends the Redundancy Check Tag (RCT) in the outgoing frame, duplicates the frame and sends both frames over the two sending ports of the node. These two frames travel through the network and arrive at the receiving node with certain time difference. If the receiving node works in the duplicates accept mode, the LRE receives both frames of a pair and forwards them to the upper layer. The rejection of one duplicate should occur at the higher layer in principle. In this case, the designed application should be able to handle duplicates. For example, the TCP is designed to handle duplicate. Applications using UDP must be able to treat duplicate since UDP is a connection-less protocol. If the receiving node works in the duplicate discard mode, the LRE should pass the first frame of a pair to the upper layer and reject the second.

The duplicates rejection function of the LRE can be realized in software in PRP. But In the application scenario of HSR, the communication is often very heavy. If the function of

rejecting the duplicates of the LRE is executed in software, the processor will be heavily loaded.

Besides, unlike in PRP that nodes only send and receive frames, nodes in HSR must also be able to forward frames based on the forwarding rules. The routing of the frame is executed by the switch logic in HSR nodes. Again, if the switch logic is implemented in software, the processor is heavily loaded due to the heavy traffic in HSR.

To offload the processor, the duplicates rejection function of the LRE and the switch logic are preferably implemented in hardware. The performance of the implemented duplicates rejecting function should apply the "best effort principle".

One challenging issue in the implementation is to find an algorithm to reject the duplicated frames and circular frames (the generating of the circular frame will be explained in the next chapter), because the algorithm used in PPR is not resource efficient and not designed for handling the circular frames. Therefore, the motivation of this Thesis is to find an effective algorithm to reject the duplicated and circular frames and implement the HSR protocol (the switch logic and the LRE) together with the selected algorithm in hardware.

# 1.3 Tasks

The Tasks of this thesis are divided into 4 parts:

First, different algorithms are proposed to reject the duplicated and circular frames.

Second, a software simulation environment is set up to test the proposed algorithms.

Third, the hardware structure of the switch is designed and programmed in VHDL language, the functionality is simulated with the ModelSim of Menthor Graphics.

Fourth, the VHDL code is synthesized with Quartus of Altera and the function of the design is evaluated by the pos-Synthesis simulation.

# 1.4 Contributions

In respect to the work of rejecting the duplicated frames in HSR, the University Zurich of Applied Science has done an architecture study of the Redundancy Box in year 2007 [8]. In 2008 they implemented the RedBox in FPGA [7]. The algorithm they applied for rejecting the duplicated frames is "circular buffer". In this method, a frame is declared as not in the table only after the entire table is searched, which introduces a long delay. The work by Christoph Klarenbach introduced a method of integrating the real-time Ethernet in the FPGA[26], which gives an example for the FPGA implementation in this Thesis.

In this Thesis, 3 algorithms are proposed to reject the duplicated and circular frames in the ring. A software test environment has been set up to simulate the communication in the ring. The performance of the 3 algorithms is simulated and compared with the help software simulation environment. The advantages and disadvantages of the algorithms and their different configurations are also explained in respect of the performance and the hardware complexities. The structure of the switch has been designed to implement the HSR protocol including the selected algorithm.

The selected algorithm for rejecting the duplicated and circular frames has reached almost 100% rejection ratio under the network configuration given in IEC61850-9-2 standard and in a network scale less than 64 nodes in a ring. The searching time is significantly reduced compared with the algorithm proposed by the University Zurich of Applied Science. The limitation of the proposed algorithm in respect to the scale of the network is further discussed. Finally, the designed switch executes all the functionalities successfully according to the pos-Synthesis simulation.

#### 1.5 Overview

In chapter 2, the High Availability Seamless Ring is introduced. The introduction includes its topology, the communication rules, and the challenging issues by now.

In chapter 3, the three proposed algorithms are explained. The advantages and disadvantages are discussed in respect to the searching time and the complexity of the hardware implementation.

In chapter 4, the software simulation model is introduced. The performance of the three proposed algorithms with different configurations is compared. A short insight into the limitation of the proposed algorithms is given.

In chapter 5, the designed structure of the switch is explained; the way each component works is described in detail, several issues in the FPGA design is introduced. The programmed switch is synthesized in Quartus, a brief synthesis report is presented. After the synthesis, the pos-Synthesis simulation is performed to verify the correctness of the design

In chapter 6, a conclusion of this thesis and a view of possible future work are given.

# 2 The High Availability Seamless Ring

This chapter gives an overview of the High Availability Seamless Ring (HSR) protocol. The topology and the communication rules of the HSR are first described, then the network layer model and the structure of the switch unit is illustrated. The typical application scenario is introduced and the problems existing in the communication by now are explained.

# 2.1 The Topology of HSR

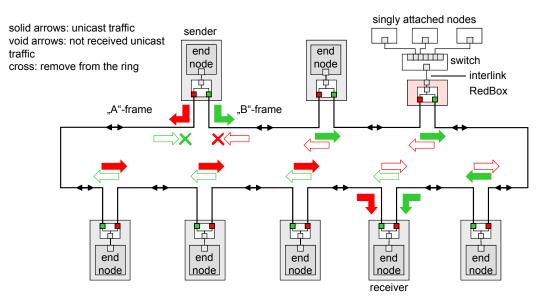

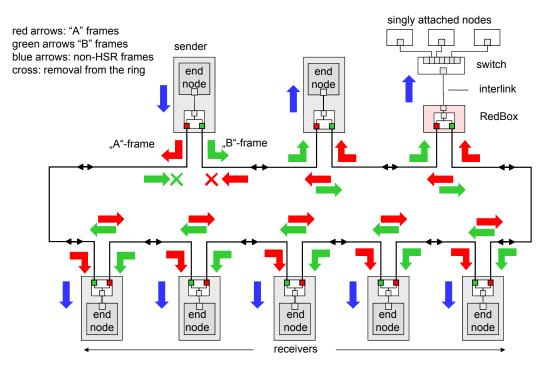

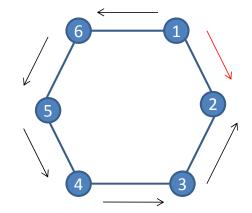

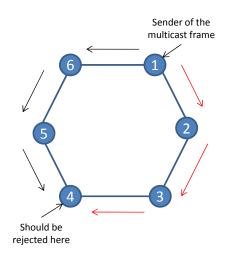

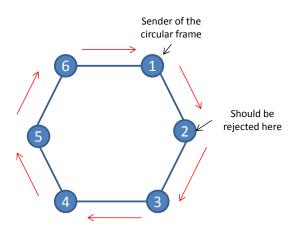

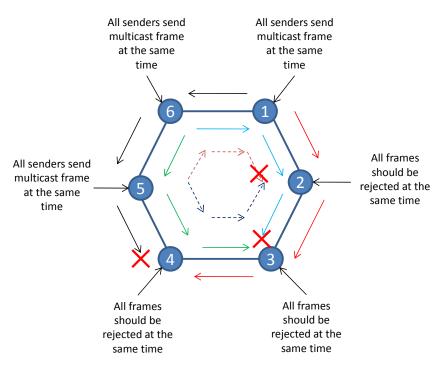

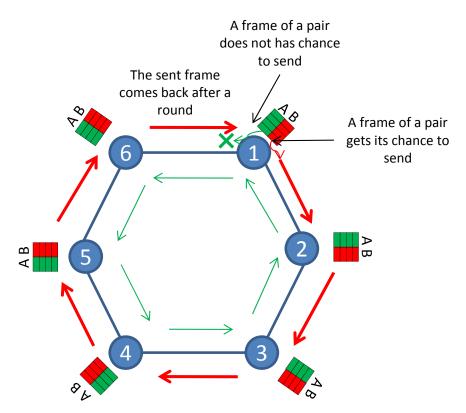

One topology of HSR is shown in Figure 2.1 and Figure 2.2 with unicast traffic and multicast traffic respectively. Each end node has two ports connected to the ring. For each frame to send, the node sends it duplicated over both ports (A-frame and B-frame). One frame of the pair travels in the ring in the clockwise direction, the other frame travels in counter-clockwise direction.

Nodes within the ring are restricted to be HSR-capable switching end nodes. General purpose nodes (e.g. the singly attached node in Figure 2.1) cannot be attached directly to the ring, but require a Redundancy Box (RedBox). A pair of such RedBox can be used to connect hierarchically a HSR to a PRP network. All the frames in the ring must be a HSR frame. A non-HSR frame must be appended with a HSR tag when it entries the ring (blue arrows in Figure 2.2).

Figure 2.1 HSR with unicast traffic: the solid arrows stand for the unicast traffic, the void arrows stand for not received unicast traffic, the cross stands for the traffic removed from the ring [3].

Figure 2.2 HSR with multicast traffic: the solid arrows stand for the multicast traffic, the void arrows stand for not received multicast traffic, the cross stands for the traffic removed from the ring [3].

# 2.2 The Network Management

A node has the same MAC address on both ports, and only one set of IP addresses assigned to that address. This makes redundancy transparent to the upper layers and therefore it is a layer 2 redundancy. This configuration allows the Address Resolution Protocol (ARP) to work the same as with a Singly Attached Node (SAN). TCP/IP traffic is not aware of the layer2 redundancy, but it is designed to deal with duplicates.

# 2.3 The Communication Rules of the Switch End Node in HSR

The communication rules are defined in the IEC 62439-3 standard [4].

#### 2.3.1 Sending

For each frame to send on behalf of the higher protocol layers, a sending node (e.g. "sender" in Figure 2.1) detects which kind of traffic (HSR or non-HSR) it generates. This decision is application-dependent; it can for instance be based on the protocol type or a priority field. By default, all traffic is HSR.

Based on that decision, the node shall:

- 1) for the HSR traffic (if the node is attached to the ring): send two frames tagged as HSR, one over each ring port, called "pair", otherwise

- 2) for a non-HSR traffic (if the node is not attached to the ring): send the frame unmodified to the switching element, which will treat it according to its bridging protocol (e.g. send only over the non-blocking port).

#### 2.3.2 Receiving

A receiving node (e.g. "receiver" in Figure 2.1) detects the type of traffic of the received frame based on the HSR tagging and shall:

- 1) for a non-HSR frame(if the node is not attached to the ring): pass it unchanged to its higher protocol layers, otherwise

- 2) for an HSR frame(if the node is attached to the ring): remove the HSR tagging and pass the modified frame to its higher protocol layer, if this is the first frame of a pair, otherwise

- 3) discard the duplicate if this is the second frame of a pair.

#### 2.3.3 Forwarding

A node that receives a valid frame over one ring port shall:

- 1) If it identifies this frame as a non-HSR frame, handle it according to the rules of its bridging protocol, otherwise:

- 2) If it identifies the frame as HSR frame, it shall forward it without modification over its associated ring port, except that it shall discard it:

- a) if it identifies the frame as an HSR frame that it already sent in the same direction, which is usually the case for multicast frames (solid arrows in Figure 2.2) but also for unicast HSR-frames without a receiver (void arrows in Figure 2.1);

- b) if the node is the sender of this node, as shown in Figure 2.1; this condition is enabled by default and can be disabled for debugging purpose.

- c) if the associated ring port of the node is not operating or its link not active. If a previously connected port is not connected to the network for a time longer than 1 s, a node shall purge the port's buffer so that it cannot send an obsolete frame, and only allow buffering when the port is reconnected.

These rules remove circulating HSR frames and open the ring, in the same way as an RSTP or similar protocol. It applies to frames originally sourced by the node and to frames circulating in case a device is removed after having sent a frame, and the ring is closed again, for instance by a mechanical bridging device or when a Singly Attached Node (SAN) is removed.

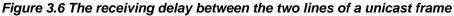

The arriving time difference between two frames of a pair depends on the relative position of the receiving node and the sending node. Assuming a worst case in which each node in the ring is transmitting at the same time its own frame with the largest size of 1536 octets, each node could introduce 125 us of delay at 100 Mbit/s. With 50 nodes, in case of uncast traffic, the time skew may exceed 6 ms, so there is possibility that the situation described above exists.

#### 2.3.4 Cut-through

Nodes in HSR should work in the cut-through mode to reduce the forwarding delay. After the destination address, source address and sequence number have been received and the frame is confirmed as not received or not sent before, the node begins forwarding the frame over the other line. The cut-through operation is not applied to the receiving port to the host. The frame passed to the host is always completely received first. Only good frames are passed to the host.

#### 2.3.5 Bad Frame Handling

Special care is needed to handle the bad frames when nodes in the ring are operating in the cut-through mode. If a frame is asserted as bad frame before the cut-though operation is performed, it is simply dropped. If a frame is detected as a bad frame after the cut-through operation is performed, a garbling sequence is appended at the end of the frame and the source address of this frame will be registered by the node. If a frame with the same source address is received again on the same line, no cut-through is performed, the frame is sent only after it is completely received and verified to be a good frame. If the frame is a good frame, the entry of this source address is cleared. Next time a frame with the same source address is received, the frame is sent in cut-through mode again.

A node in HSR should be able to detect the garbling sequence appended at the end of the frame. A garbling sequence tells a node that the frame is already been registered by another node as a bad frame, this node does not need to register this bad frame again. By doing so, only the first node which received the bad frame performs store-forward on the frames with same source address, other nodes still operate in cut-through when a frame with the same source address is received. This can reduce the transmission time in the ring of a good frame with the same source address as the bad frame. A bad frame appended with a garbling sequence will be passed around the ring until it is discarded by the node which sends it or is rejected as a circular frame.

# 2.4 Frame Format for HSR

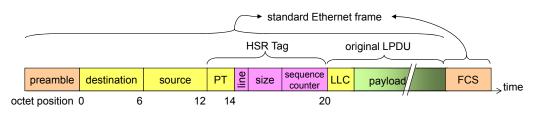

A HSR frame is identified uniquely by their source MAC address, destination MAC address and the HSR Tag. The frame format is shown in Figure 2.3.

The HSR tag is placed at the beginning of the frame to allow early identification of frames for cut-through operation. After the destination address, the source address and the sequence number are received, the frame is uniquely identified.

The HSR tag is announced by the dedicated Ethertype = 0x88FB, which is the same as IEC 62439-3's Ethertype. If the frame carries a tagging according to 802.1Q, it shall be inserted before the HSR tagging.

The 4 most significant bits of the16-bits HSR tag distinguish a PRP management frame from a HSR management frame or a HSR payload.

- a) 4-bit path identifier which can be a ring identifier or indicate a PRP supervision frame

- b) 12 bit frame size (LSDU\_size)

- c) 16-bit sequence number (SequenceNr)

Figure 2.3 The frame format of HSR [4]

The sequence number is inherited from PRP, where they are used to discard the duplicated frames when receiving. The concept of "Duplicate Discard" in PRP will be explained later in section 3.1, and the reason why it cannot be wholly applied in HSR is also given there.

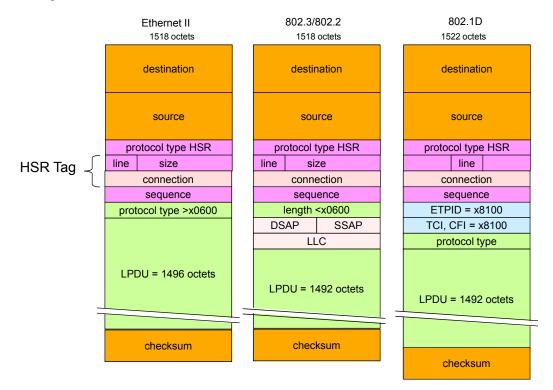

Because of the insertion of the HSR tag, the length of the frame may exceed the maximum length of 1522 octets allowed by the IEEE 802.1 D standard. But since the traffic in the ring is private, the modification can be done in the switch element to adapt the exceeded frame length and this will have no influence on the Ethernet traffic outside the ring.

Figure 2.4 Frame format in different Ethernet standard after insertion of the HSR tag. The additional six bytes could generate oversize frames of more than 1522 octets [7]

#### 2.5 The Node Structure and Operation in HSR

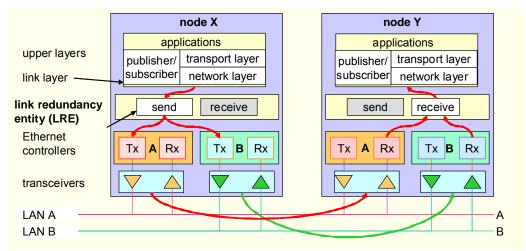

The structure of the node in HSR is shown in Figure 2.5.

When sending, the LRE duplicates each frame and send the pair of the frame over port A and port B (1, 2).

When forwarding, the switching logic relay frames from one port over the other port (3, 4), except it is the frame it already forwarded or it is the sender of this frame.

When receiving, the LRE receives both frames, keeps the first frame and discards the duplicate (7).

Figure 2.5 The node structure in HSR [3]

# 2.6 Duplicate Handling

Duplicate Handling is an important issue in HSR. The duplicate handling can work in two modes:

- a) Duplicate Accept, in which the sender LRE uses the original frames and the receiver LRE forwards both frames it receives to its upper protocol layers.

- b) Duplicate Discard, in which the sender LRE appends a Redundancy Control Trailer to both frames it sends and the receiver LRE uses that Redundancy Control Trailer to send only the first frame of a pair to its upper layers and filter out duplicates.

It is advantageous to discard duplicates already at the link layer. It is because not all the protocols in the upper layers can deal with duplicates. From the view of costs, the processor has twice as many interrupt requests as when only one ring exists. To offload the application processor, the LRE can perform "Duplicate Discard", which should be realized in hardware.

In PRP, the Sequence Number, which is located in the HSR frame format shown in Figure 2.4.1, is used to drop the duplicates (recall that HSR is a modified application of PRP). Each time an LRE sends a frame to a particular destination it increases the sequence number corresponding to that destination and sends both frames over both LANs.

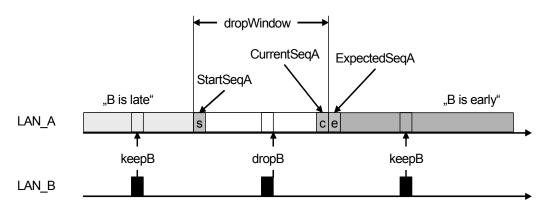

The algorithm used for rejecting the duplicates is the "Drop Window" algorithm. Briefly speaking, it builds a window at each line A, B. If the received frame at one line falls into the window of the other line, the frame will be dropped. This is shown in Figure 2.6.

Figure 2.6 The drop window algorithm [4]

#### 2.1 The Problem with the Drop Window Algorithm in HSR

The drop window algorithm works well in PRP because each node in PRP only sends or receives frames, it never relays a frame. In HSR, each node also forward frames except receiving and sending. As stated before, the situation may happen that a multicast frame losing the sender or a unicast frame losing both the receiver and the sender will circulate in the ring. There must be a mechanism to remove such circular frame from the ring. Since it is not possible to use the "Drop Window" algorithm for such purpose, it is preferred to find another algorithm which can not only be able to reject the duplicated frames but also the circular frames.

Another reason why the Drop Window algorithm is not used here is that the implementation of the "Drop Window" algorithm in hardware is less efficient than the lookup table method which will be introduced later in this Thesis [8]. For these reasons, new solutions are found and proposed in the next chapter.

# 3 The Proposed Algorithms for Rejecting the Duplicated and Circular Frames

In this chapter, three algorithms are proposed for finding an efficient way to reject the duplicated and circular frames. Their operation principle is explained, the advantages and disadvantages of each algorithm are discussed in respect to the collision possibilities, the searching time and the hardware implementation complexity.

# 3.1 General Principle

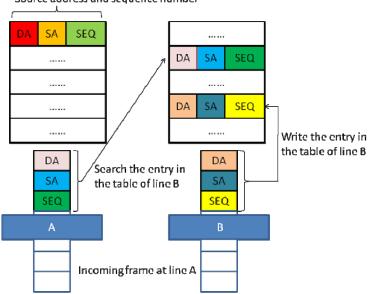

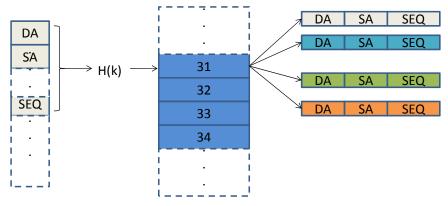

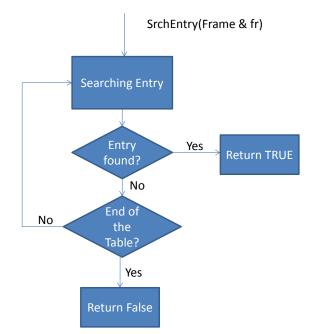

Instead of the "Drop Window" algorithm applied in PRP, algorithms based on look-up tables are applied. The basic idea is:

Each frame in HSR is uniquely identified by its destination address, source address and the sequence number (recall that the sequence number for each destination address is increased by one when a frame is sent to this destination address). Therefore the destination address, the source address and the sequence number can be stored as an entry in the table to show that this frame has already been received.

An entry is composed of destination address Source address and sequence number

Figure 3.1 The searching and writing operation in the table for rejecting the duplicated frames

The working principle is stated as below:

1. For rejecting the duplicated frames (the frames can be unicast or multicast frames)

There is one table for each line to store the entry of frames which have been successfully received on this line (means no error occur during receiving).

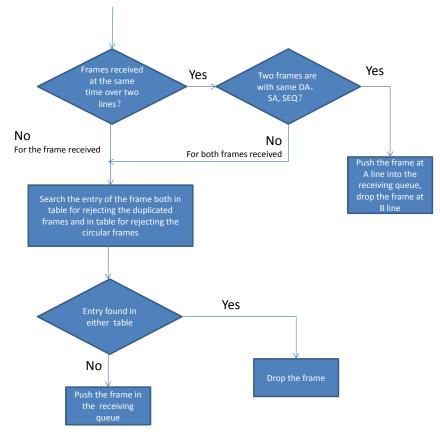

During receiving at one line, after the destination address, the source address and the sequence number of the frame have been received, the frame is searched first in the table of the other line. If it is found in the table of the other line, it will be discarded and the receiving process is aborted otherwise If the entry of this frame is not found in the table, the receiving process will continue. If the frame turns out to be a good frame at the end of the receiving, the entry of the frame will be stored in the table of the line at which it is received.

If frames of a pair are received on both lines when there is no entry of either frame in the table (for example two frames are received on both lines at the same time), the Window Function described in Section 5.4.3 is applied.

The case of rejecting the duplicated frames is illustrated in Figure 3.1.

2. For rejecting the circular frames (the frame can be any traffic type of frames)

To reject the circular frames, there is one table on each line to store the entry of frames which have been successfully received on this line (means no error occurs during receiving).

During receiving at one line, after the destination address, the source address and the sequence number of the frame have been received, the frame is searched first in the table of this line. If it is found in the table of the this line, it will be discarded and the receiving process is aborted otherwise

If the entry of this frame is not found in the table, the receiving process will continue. If the frame turns out to be a good frame at the end of the receiving, the entry of the frame is stored in the table of the line at which it is received.

The case of rejecting the circular frames is similar with the case of rejecting the duplicated frame except that the entry is searched and written in the same table of the line on which the frame is received but not in the table of the other line.

The entry of a frame is written in the table only after the frame is completely received and verified to be a good frame. If a frame turns out to be a bad frame it will not be registered in the table, so when the other frame of this pair is received on the other line, the entry will be not be found in the table and the frame is therefore received. The same reason applies for the circular frames.

The operation of rejecting the duplicated frame stated above implies that the table can be read and written at the same time. For this purpose, the Dual Port RAM should be used.

The general principle is clear by now, the issue left is to find an efficient data structure to implement such table. There are several methods to lookup an item in table. The conventional methods are like the binary search algorithm and hash table. Binary search is based on the sorted table. But here the sorting is difficult to define (e.g. what criteria should be used to sort the entries) and the hardware is difficult to implement. There are different ways to implement a hash table, some methods are suitable in our situation, some not. The discussion of the hash table will be conducted in later sections. In the following sections, three algorithms are proposed to implement the lookup table described above.

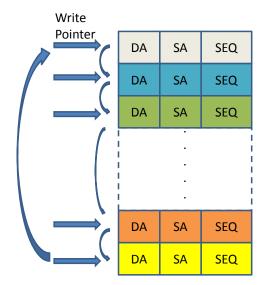

#### 3.2 Algorithm 1: Circular Buffer

The Circular Buffer method is introduced by the Zurich University of Applied Sciences (ZHAW, Winterthur) to implement the rejection of the duplicated frames in the Redundancy Box [7].

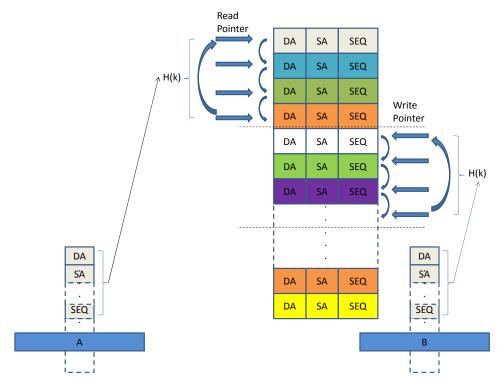

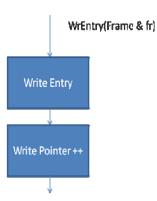

In this method, the entries are simply registered in the table one after another. The write pointer moves downwards by one after an entry has been registered. In this way, the entry of higher position is older. After the write pointer reaches the end of the table, it will go back to the beginning of the table and start over. This is shown in Figure 3.2. In this way, the older entry is automatically replaced by the new entries.

In this algorithm, the length of the table has to be selected according to the receiving delay of the frame of a pair between the two lines [8]. Take a ring with 6 nodes for example (Figure 3.3). If node 1 send a unicast frame to node 2, one frame of the pair goes the clockwise direction and arrives at node 2; the other frame of the pair travels the counter-clockwise and must goes through 4 nodes until arrives at node 2. Assuming that the length of all the frames in the ring is the same, node 1 could receive 4 other frames, until the frame sent by node 1 arrives at node 2, which means that 4 more entries are registered in the table during this time. Therefore the table should have places for at least 5 entries so that the entry of the first frame of a pair sent by node 1 is not overwritten by other entries before the second frame of the pair arrives at node 2.

Figure 3.2 The operation principle of a circular buffer

Figure 3.3 The receiving delay of a pair unicast frame in a ring

This is just a simple example to illustrate that the length of the table is related to the receiving delay between the two lines, the reality is more complex.

Because the entries are simply registered in the table one after another, the hardware implementation is simple. If the table is large enough, frames' entry can be found in the table before their entries are overwritten. But one should go through all the entries to verify that the received frame is not in the table. In a ring with more nodes, the search will cost more time and therefore cause longer delay when forwarding. If cut-through operation is required, this method is not suitable.

#### 3.3 Algorithm 2: Hash Table with Open Addressing and Aging

#### 3.3.1 Why Open Addressing

To increase the search efficiency, hash table is used. There are many algorithms to implement a hash table and resolve the collisions. The conventional ones are like chaining, open addressing and so on.

Chained hash tables have advantages over open addressed hash tables in that the removal operation is simple and resizing the table can be postponed for a much longer time because performance degrades more gracefully even when every slot is used. Indeed, many chaining hash tables may not require resizing at all since performance degradation is linear as the table fills. For example, a chaining hash table containing twice its recommended capacity of data would only be about twice as slow on average as the same table at its recommended capacity [9].

But chained hash tables need to allocate memory for adding elements to the linked list. The overhead required by the operation of allocating new memory will cause more delay and therefore is not preferred in real-time system. Furthermore, a memory allocator is more difficult to implement than the open addressing.

Compared with chaining, open addressing is [9]:

More space-efficient since it doesn't need to store any pointers or allocate any additional space outside the hash table, this makes it more suitable to be implemented in memory constrained devices like FPGA.

The Insertion of elements avoid the time overhead of memory allocation, and can even be implemented in the absence of a memory allocator.

Because it uses internal storage, open addressing avoids the extra indirection of the external storage required by chaining. It also has better locality of reference, particularly with linear probing. With small record sizes, these factors can yield better performance than chaining, particularly for lookups.

At last, they can be easier to serialize, because they don't use pointers.

#### 3.3.2 Open Addressing Algorithm and its Constraints

The open addressing algorithm can be briefly explained as follows [10]:

A hash table *T* is an array *T*[0,....*m*-1], m is a positive integer called the size of the table.

If we have a sequence of hash functions  $< h_0, h_1, h_2, \dots, h_{m-1} >$ , such that for any item *x*, the *probe sequence*  $< h_0(x), h_1(x), h_2(x), \dots, h_{m-1}(x) >$  is a permutation of  $< 0,1,2,\dots,m-1 >$ . In other words, different hash functions in the sequence always map x to different locations in the table.

x is searched by using the following algorithm, which returns the array index i if T[i] = x, "absent" if x is not in the table but there is an empty slot[11], and "full" if x is not in the table and there no empty slots. This is shown in figure below.

for

$$i = 1$$

to  $m - 1$

if  $T[h_i(x)] = x$

return  $h_i(x)$

else if  $T[h_i(x)] = \phi$

return Absent

return Full

Under the *strong uniformity assumption*, that is for any key  $k \in U$

$$\Pr\{(h_i(k), h_j(k)) = (i, j)\} = \frac{1}{m(m-1)} \quad (3.1)$$

the expected lookup time is calculated as

$$E(T(m,n)) \le 1/(1-\alpha)$$

(3.2)

Here  $\alpha = n/m$  is called the load factor of the table and n is the number of current element in the hash table.

Here we can see, with the increasing of the load factor  $\alpha$ , the expected lookup time increases dramatically, if the table is almost full, the lookup will take increased to certain degree that one has to go through the entire table to found out whether an element is in the table or not.

Deleting an element in the table is also not simple. We cannot simply clear out the slot in the table, because we may need to know that T[h(x)] is occupied in order to find other items. Instead simply deleting a slot, we should mark it as a wasted slot. But a sufficiently long operation of insertions and deletions could eventually fill the table with marks, leaving little room for any real data and causing searches to take linear time. Therefore the size of the table should be increased when the load factor reaches a threshold value. The time costs of such operation can be very expensive. This can be shown by the amortized analysis but not an issue in this thesis.

On the other hand, the implementation of a hash table in real-time system cannot afford the time cost of enlarging the hash table all at once, because it may interrupt time-critical operations. And the device like FPGA with a constrained memory may not allow the increasing of the table size [9].

Because it is not desirable to go through the entire table until to find out whether the element is in the table and it may not possible to resize the table, we have to find another way to implement the table. A commonly used technique "Aging" is applied here.

#### 3.3.3 Open Addressing With Aging

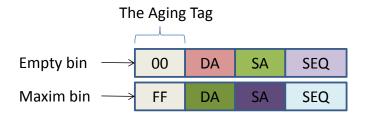

Figure 3.4 shows the entry structure in open addressing with aging. A one-byte "Aging Tag" (AT) is added at the beginning of each entry [12]. The meaning of the AT is:

x"00" An empty bin

x"FF" The maximum bin

At the beginning, the value of the AT is x''00''. Every time an entry is written to a bin, the AT of this bin is assigned to the value of x''FF''. An aging process runs in the background with certain time distance, which is determined by the scale of the network. The value of the AT is subtracted by one until the AT becomes x''00'' again. Therefore, the smaller the value of the AT is older the entry.

Figure 3.4 The entry format with "Aging Tag"

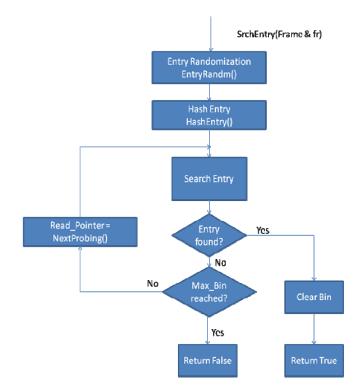

The searching algorithm is described as following

for

$$i = 1$$

to max\_bin

if  $T[h_i(x)] = x$

$T[h_i(x)]AT = x"00"$

return  $h_i(x)$

return Absent

This algorithm states if an entry is found in the table, the corresponding place will be cleared by writing AT of the bin with x"00". The *max\_bin* defines the maximum probe time, after the *max\_bin* is reached, the searching stops and return *Absent* to indicate that the entry is not found in the table.

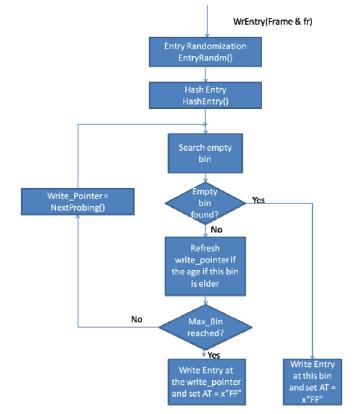

The writing entry algorithm is a little more complicated, which is described as follows

for i = 1 to max\_bin if  $T[h_i(x)]AT = \phi$   $T[h_i(x)] = x$   $T[h_1(x)]AT = x"FF"$ return else  $Oldest_Pos = T[h_i(x)]AT \le Oldest ? h_i(x) : Oldest _ Pos$   $Oldest = T[h_i(x)]AT \le Oldest ?T[h_i(x)]AT : Oldest$ return  $Oldest_Pos$  $T[Oldest_Pos] = x$

The figure above states, when writing an entry in the table:

If an empty bin is found, the entry will be written at this bin. If the bin is not empty, the AT of this bin will be stored in the variable **Oldest**, and the position of this pin is stored in the variable **Oldest\_Pos.**

Every time when the bin is not empty, if the AT of this bin is older than the **Oldest**, the **Oldest** will be replaced by the AT of this bin and the **Oldest\_Pos** is replaced by the position of this bin.

If no empty bins are found in the end, the entry will be written at the place of the *Oldest\_Pos* bin.

The algorithm described above is illustrated in Figure 3.5.

The advantage of introducing the *max\_bin* is that it constraints the searching and writing time in the worst case to *max\_bin* steps, so that the decision can be made in much shorter time than going through the entire table, which is the case in the conventional open addressing hash table.

The aging mechanism is necessary for deciding the bin to write when all the bins are filled with entries. In other words, the resizing of the table is replaced by just writing at the bin with the eldest AT. This takes place in the same store area, and do not require additional memories. Another use of AT, although dose not likely to occur under heavy traffic, is to time out the entries which are not received at the other line for a long time.

Figure 3.5 The search and write operation in modified hash table with open addressing

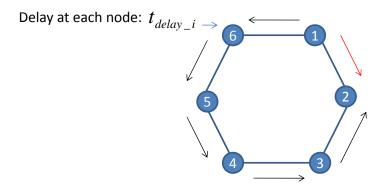

The time distance of subtracting the aging tag should consider the scale of the network. Take a look at the simple example of unicast traffic again, shown in Figure 3.6.

In the ring having nodes of number *n*, the transmit delay (the time delay between completely receiving a frame and completely sending it out) is  $t_{delay}$  at each node.

When for example a unicast frame of a pair sent by node 1 arrives at node 2, its entry is registered in the table. The time delay of the arriving of the second frame of this pair on the other line is calculated as

$$t_{delay\_total} = \sum_{i=1}^{n-2} t_{delay\_i}$$

(3.3)

Therefore

$$t_{subtract\_int\,eval} \ge \frac{t_{delay\_total}}{256}$$

(3.4)

Recall that the maximum of AT is x"FF".

Therefore the time distance of aging cannot be so frequent that the entry times out before the  $t_{delay\_total}$  is reached. In reality the traffic is more complex. One should configure the time distance of subtracting the aging tag enough long to ensure that the case described above does not happen.

#### 3.3.4 Choose the Random Probe Sequence

In practice the truly random probe sequence  $\langle h_0(x), h_1(x), h_{2}(x), \dots, h_{m-1}(x) \rangle$  is difficult to find, so one of the heuristics can be used

#### 1) Linear probing

Using a single hash function h(x), and define

$$h_i(x) = (h(x) + i) \mod m$$

(3.5)

The operation in this equation is simple, but it suffers from a phenomenon known as primary clustering, in which large chains of occupied positions begin to develop as the table becomes more and more full. This results in excessive probing

#### 2) Quadratic probing

Also using a single hash function h(x), and define

$$h_i(x) = (h(x) + i^2) \mod m$$

(3.6)

Unfortunately, for certain values of m, the sequence of hash values  $\langle h_i(x) \rangle$

does not hit every possible slot in the table; we can avoid this problem by making m a prime number. Although quadratic probing does not suffer from the same clumping problems as linear probing, it does have a weaker clustering problem known as secondary clustering: If two items have the same initial hash value, their entire probe sequences will be the same.

#### 3) Linear Double Probing

We use two hash functions h(x) and g(x), and define

. . . . .

$$h_i(x) = (h(x) + ig(x)) \mod m$$

(3.7)

To guarantee that this can hit every slot in the table, the stride function g(x) and the table size *m* must be relatively prime. This can be guaranteed by making m prime. The key advantage of linear double hashing over linear probing is that it is possible for both h(k) and g(k) to vary with k. Thus, in  $h_i(x)$  the probe sequence depends on k through both h(k) and g(k), and is linear in h(k) and g(k). A widely used member hash function proposed by Knuth is [13]

$$h(k) = k \mod m$$

$$g(k) = k \mod(m-2)$$

(3.8)

#### 3.3.5 Randomization of the Un-uniform Distributed Keys

The ordinary hash function h(x) used in equation (3.4) and equation (3.5) has a dramatic impact on the performance of linear probing and quadratic probing. A common choice like:

$$h(x) = x \mod m \quad (3.9)$$

This performs only well when the key x is uniformly distributed, so that this ordinary function can generate uniformly distributed sequences. When the key x diverges from the uniform distribution, the performance of linear probing and quadratic probing degrades dramatically[14].

This is unfortunately our case. Assume a ring has 10 nodes, the variation of the key which is the concatenation of the destination address, source address and the sequence number is limited. This is because:

- First, the first 3 bytes of the MAC address is the manufacturers Organizational Unique Identifier (OUI). In a ring, the manufacturers are not likely to exceed 20. So the variation of this part is very limited

- Second, if the traffic is multicast, the destination is always the multicast address. The most traffic in the ring is multicast traffic.

- Third, although the sequence number varies most frequently (from 0 to 65535), it varies only at the end of a key.

Therefore the key in our case is far from uniformly distributed.

Two approaches are commonly used to address this problem. First, one can apply a randomizing transformation to the keys prior to supplying them to Equation 3.9. This is actually a natural step to take in many applications. For example, consider compiler symbol tables, where strings must be converted into numeric key values in order to "hash" them into the table. One such popular algorithm, called **hashPJW()**[15], takes a string as input, and output an integer in the range  $[0,2^{32}-1]$ . The transformation performed by **hashPJW()** tends to do a good job of producing numbers that appear uniformly over certain interval, even when the strings being hashed are very similar.

A second approach involves using a more complicated ordinary hash function h(x) so that the initial probe into the hash table is more random. In addition, by randomizing the choice of h(x) itself we can guarantee good average-case performance (relative to any fixed ordinary hash function) through the use of universal hashing[16].

A set H of hash function is universal if it satisfies the following property:

For all pairs of distinct keys  $x \neq y$ , if a hash function *h* is chosen uniformly random from the hash function family set H, then

$$\Pr[h(x) = h(y)] \le 1/|V| \quad (3.10)$$

|V| denote size of V, the number of possible hashed values.

A good example of a universal hash function is

$h(k) = ((ak+b) \operatorname{mod} p) \operatorname{mod} m \quad (3.11)$

Here  $a \in \mathbb{Z}_p^*$ ,  $b \in \mathbb{Z}_p$ ,  $\mathbb{Z}_p^*$  denotes the set {1, 2, 3, ...., p - 1} and p is a prime number large enough so that every possible  $k \in U$  is in [0, p-1]. Thus, for fixed p and m, there are p(p - 1) different hash functions in this family.

Although the universal hash functions provide a good performance, the multiplication operation in the FPGA is very expensive especially when the key k is more than 32 bits. There are ways like addition tree can work around this problem, but again it sacrifices time and causes longer delay. Besides, the mod operation of a prime is difficult to realize. Only the mod operation of the order of 2 is able to be synthesized. Therefore, the randomizing transformation method is chosen.

#### 3.3.6 The Randomness of Double Hashing

If the goal is to minimize the total number of collisions and thus memory accesses, then from a probabilistic perspective, the ideal case for open address hashing is uniform hashing[17][18].

A uniform hash function always produces probe sequences of length m (in the table space), with each of the m! possible probe sequences being equally likely. The obvious way of implementing a uniform hash function involves the generation of independent random permutations over the table space for each key  $k \in U$ . However, the computational costs associated with this strategy make it completely impractical.

Through probabilistic analysis, the function described by Equation (3.7) offers a reasonable approximation to uniform hashing[19][20]. This conclusion is based on the **strong uniformity assumption** shown in Equation (3.1). Thus, these results only hold under the assumption that the keys will produce hash value pairs that are jointly uniformly distributed over the table space. This strong assumption has requirements both on the initial data distribution and the choice of h(k), g(k). As the most data set are far from uniform (which is indeed our case), and the popular candidate for h(k), g(k), which is described previously, has to be considered poor choices to satisfy the Equation (3.1).

#### 3.3.7 Memory Access Serialization

According the algorithm applied by the hash table with open addressing and aging. It can be seen that there are three processes that need both read and write access to the table:

- 1) The aging process, which runs in the background. It needs read the aging tag, and subtracts AT by one if it is not equal to zero.

- 2) The searching process, which read the entry in the table, and clear the entry by writing AT to x"00" if it is found.

- 3) The writing process, which first reads AT in the table and register the entry in the empty bin or the bin with the oldest AT if no bins are empty.

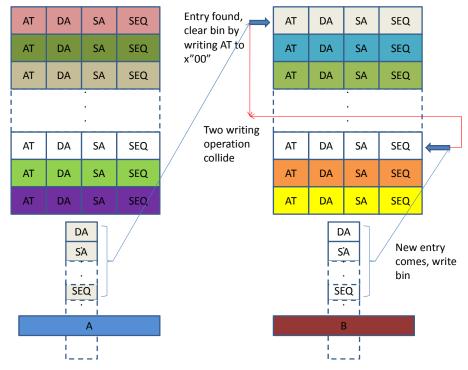

Since the table is located in the dual port memory, it is allowed that reading and writing happens at the same time. But if two reading or writing operations are to be executed at the same time, the two operations must be serialized. A collision between two writing operation in the table for rejecting duplicated frames can be show in Figure 3.7

For the table used for rejecting the circular frames, because the searching and writing process occurs at the same line and therefore naturally serialized (means the searching operation always come previous to the writing process), the serialization only have to be done between the aging process and the reading or writing process. Here the reading and writing process always have the higher priority than the aging process, because we want to make the decision as early as possible so that the cut-through can be performed earlier.

For the table used for rejecting the duplicated frames, the searching and writing is required by different lines, the sequence of their occurrence is not deterministic. Therefore the searching, writing and aging process should be serialized respectively. The searching process has the highest priority, the reason is same as stated above to enable earlier cut-through. Writing process has the second priority because it is not time critical like searching process. If during writing searching is required by other line, writing should be suspended and give the memory access control to the searching process. Finally the aging process has the least priority.

Figure 3.7 Clearing bin operation collides with the writing entry operation

The time period from the sequence number to the end of the frame is plenty for the aging process, because the subtracting of the AT is only executed in a pre-configured time distance, but not at very instance. The memory access control transfer state machine is shown in Figure 3.8.

Figure 3.8 The memory access control transfer state machine of the hash table for rejecting the duplicated frames

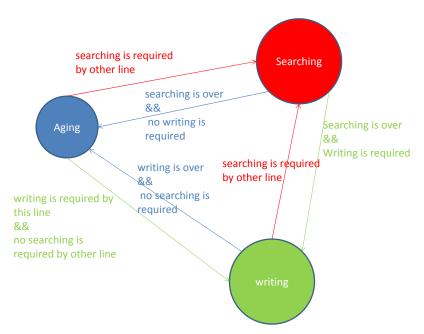

# 3.4 Algorithm 3: Hashing Combined with Circular Buffer

In the previous section, the hash table with open addressing is modified by adding the *max\_bin* parameter and the aging functionality to fix the worst case searching time and avoid resizing the whole table. But the aging functionality needs a process running on the background, and the serialization of the memory access among the aging, searching and writing process is also needed, these increase the complexity of the hardware implementation. To reduce the complexity of the implementation and still maintain a similar performance, the third algorithm is proposed.

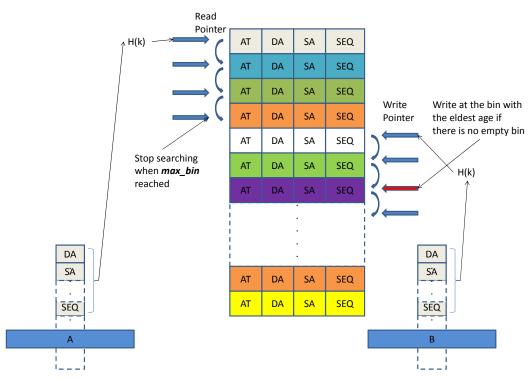

The proposed hash table structure combined with circular buffer is illustrated in Figure 3.9. The table is divided into several regions, the hash value of the entry decided into which region the entry falls. In each region there are number of *max\_bin* bins. The entry is written at the bin position.

Figure 3.9 The structure of the hash table combined with circular buffer

The concept is similar to the chained hash table, except the element attached to each bucket is limited to the number given by *max\_bin* parameter. If all the bins are taken, the entry is simply overwritten the eldest bin, and thus there is no need for memory allocator.

The operation principle is explained as follows:

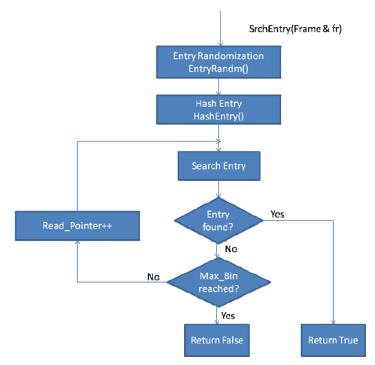

When searching an entry of a received frame:

When an entry is received, after the destination address, the source address and the sequence number are read, the hash value is calculated. The calculated value is mapped to certain area of the table. This mapping can be for example a mod operation.

The position of the read pointer in this area is the position after last searching in this area. If the entry is not found at the current position, the read pointer moves downwards by one. If entry is found, the read pointer stays at the next position to the position where the entry is found.

When searching steps has reached the *max\_bin*, searching stops and the read pointer go back to its last initial position.

When writing an entry of a good frame

Write the entry at the position of the write pointer and move the write pointer downwards by one.

If the write pointer has reached the end of the area, it goes back to the beginning of this area

Figure 3.10 Read and write operation in the hash table combined with circular buffer for rejecting the duplicated frames

In this algorithm, the maximum searching step is also limited to **max\_bin** times, and there is no aging mechanism being applied. Each area has its own read and write pointer. The writing operation iterates through the area, the oldest entry is simply overwritten. The writing entry process only does write operations, and the searching process only does read operation. Therefore there is no more than one process reading or writing at the same time and thus the memory access does not need to be serialized (Figure 3.10).

This simplifies the circuit dramatically compared with the hash table with open addressing and aging.

The map of an entry to certain area is done by the hash function

$$h(x) = x \mod m \quad (3.10)$$

Again, the key x here is far from uniform distributed, so the function for randomization of the un-uniform distributed Keys introduced in Section 3.3.5 should be used here before the hash operation.

A drawback of this method is that it does not find an empty bin to write the new entry which is done in the hash table with aging algorithm. Instead it just overwrite the oldest entry in the area. So the probability that an unused entry is overwritten is higher than the hash table with aging.

# 3.5 Comparison of the Proposed Algorithms

In Table 3.1 the proposed algorithms are compared in respect to their collision probability, worst case searching time, implementation complexity.

| Proposed algorithms                                | Collision Probability                                                                                                                                                                                                                                                                                                     | Worst Case<br>Searching<br>time               | Implementation Complexity                                                                    |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|

| Circular Buffer                                    | No collisions as long as the<br>length of the table longer<br>than frame arriving delay<br>between the two lines                                                                                                                                                                                                          | must go<br>through the<br>entire table        | simplest                                                                                     |

| Hash Table With<br>Open<br>Addressing and<br>Aging | Depending on the chosen<br>probe sequence<br>linear probe: primary<br>clustering<br>quadratic probe: secondary<br>clustering<br>double hashing: most<br>unlikely to collide compared<br>with two others<br>With the aging functionality,<br>the entry always search first<br>an empty bin to write and<br>then the oldest | limited by the <i>max_bin</i> parameter       | Most complex because of<br>the aging functionality and<br>the memory access<br>serialization |

| Hash Table<br>Combined with<br>Circular Buffer     | The oldest entry in each<br>area is simply overwritten,<br>but it is possible that the<br>overwritten entry is not used<br>yet                                                                                                                                                                                            | limited by the<br><i>max_bin</i><br>parameter | Moderate                                                                                     |

Table 3.1 Comparison of the proposed algorithms

# 3.6 Conclusion to the Proposed Solutions

In this chapter, three algorithms based on look up table are proposed to replace the drop window algorithm to reject the duplicated and circular frames in HSR.

The circular buffer method has no collision as long as the length of the table is larger than the frame arriving delay between the two lines, and it is simplest to implement. But to find out whether the entry is in the table or not, one should go through the entire table which causes long delay, this method is not suitable for realizing cut-through.

The hash table with opening address and aging functionality introduce the *max\_bin* to limit the maximum searching time. Aging kicks out the entries which already times out and ensures to write the entry only in the empty bin or bin with the oldest age. This can somehow reduce the collision probability and avoid resizing operation. But the need for implementation of the aging function and serialization of the memory access makes the circuit more complex compared with circular buffer and hash table combined with circular buffer method.

The hash table combined with circular buffer is similar with the chained hash table except that the oldest entry is simply overwritten if all the bins attached to the bucket are taken. By doing so the memory allocator is saved. But one drawback of this method is that a not yet used oldest entry may be overwritten.

A last it should be pointed out that the key of the hash function in our case is far from uniform, the randomization of the key should be done previous to hashing.

In the next chapter, the simulation environment will be built. The performance of the proposed algorithms will be simulated in respect to their rejecting ratio to the duplicated and circular frames.

# 4 The Software Simulation of the Proposed Solutions

In this chapter, a simulation environment is set up to evaluate the proposed algorithms. The basic unit in the simulation is a node. A node can accomplish all the tasks of a real end node in HSR and simulate the timing behavior of sending or receiving process. Because the program is written in C++, the operations of the nodes in the ring must be parallelized to simulate the parallel process in real hardware. The configuration of the simulation is explained and the simulation result is presented and discussed. Finally the hash table combined with circular buffer is chosen as the algorithm to be implemented in FPGA.

# 4.1 The Setup of the Simulation Environment

In this section, the structure of a node, which is the basic unit in the simulation environment, is illustrated. The components in the node and their way of work are explained in more details. The way of parallelizing the operations of a node is explained.

#### 4.1.1 The Node Class

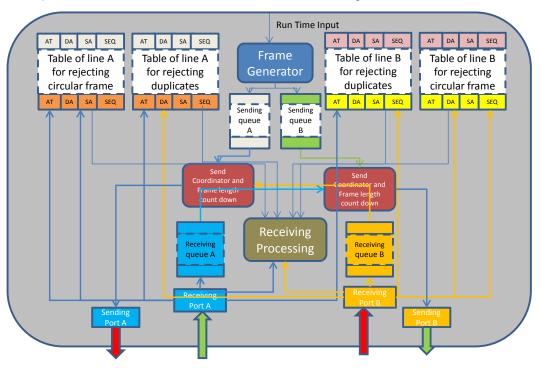

The node is the basic unit in the simulation environment. A node unit represents an end node in the HSR network. The node class designed here can accomplish all the tasks of the link layer of an end node. The tasks of a node in HSR have already been introduced in chapter 2. The structure the node class is illustrated in Figure 4.1.

Figure 4.1 The structure of the node class

As illustrated in Figure 4.1 one node unit contains 8 member objects:

- 1) One frame generator,

- 2) Two sending queues on each line,

- 3) Two receiving queue on each line,

- 4) Two tables for rejecting duplicated frame one each line,

- 5) Two tables for rejecting the circular frames on each line.

- 6) The "send coordinator and frame length countdown".

- 7) The "receiving processing" are two main control functions during sending and receiving.

- 8) The "sending port A, B" and "Receiving ports A, B" are a group of structure variable for storing the frame structure and status variables for labelling the sending and receiving status. This will be explained in next sections.

#### 4.1.2 The Frame Structure

Before going to the detail of single components in the node unit, the frame structure used in this environment should be explained first.

According to the HSR frame format, the frame here is a structure contains the destination address, the source address, the sequence number, the length of the frame, and a counter. The frame structure is shown in Figure 4.2.

| DA      |

|---------|

| SA      |

| Seq     |

| FrLen   |

| CircCnt |

#### Structure of Frame

Figure 4.2 The structure of the frame in the simulation

The destination address, source address and the sequence number together compose the entry in the hash table. The length of the frame *FrLen* is used to simulate the time behavior of receiving or sending a frame. The counter *CircCnt* records the number of the nodes this frame has gone through before being accepted or rejected. This can be used to evaluate the performance of the table for rejecting the circular frames.

#### 4.1.3 Generating Nodes in the Ring

A node is uniquely identified by its MAC address in the ring. To generate *n* nodes in the ring means to generate *n* different MAC addresses. According to the Ethernet protocol, the MAC address is divided into two parts: the first three octets of the MAC address is the Organizationally Unique Identifier (OUI) of the manufacturer, which is assigned by the IEEE Registration Authority; the last three Octets are assigned by the manufacturers.

There are two parameters can be configured. One is the OUI\_NUM, which determines how many manufacturers there is in the network. The second parameter is the number of nodes *n* in the network. If the OUI\_NUM is smaller than the number of nodes in the network, it means that there are some devices with the same manufacturer. This often corresponds to the reality considering the switch element used by the devices in the ring are from limited number of manufacturers.

When generating the nodes in the network, the OUIs are read out from the OUI tables at random locations, and assigned to the first three octets of the MAC address. Because the number of the nodes in the ring is larger than OUI, some OUIs are reused. The second three octets are generated randomly. Every time a MAC address is generated, it will be checked if it already exists in the network; if so, the second three octets should be

regenerated until this MAC address is not same with any MAC addresses generated before.

After nodes generating is over, a table of *n* different MAC addresses is created

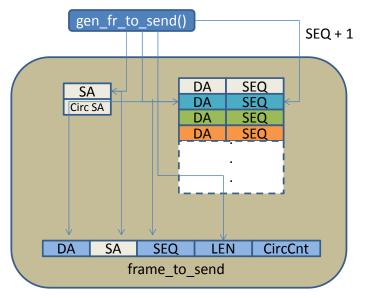

#### 4.1.4 The Frame Generator

The frame generator is a member object in the Node class. As shown in Figure 4.3, it has a table (the destination address table) of the MAC addresses of all other nodes in the ring plus a multicast frame address. This table is created from the table of the generated nodes. For example, if this node is the Nr. 2 node in the ring, then the MAC address at the second position in the generated nodes table will be taken as the source address of this node, and other addresses are put into the destination address table. Besides the MAC address of the node itself, it also contains a MAC address which does not exist in the ring. This MAC address is used to simulate a unicast frame losing sender and receiver or a multicast frame losing sender. The reason why this may happen is explained in Section 2.3.

Together with each address in the address table there is also a sequence number. Each time a frame with is generated, the sequence number of the corresponding destination address will be increased by one.

Figure 4.3 The structure of the frame generator and its

The probability of generating a multicast or a circular frame can be configured. When generating a frame, the function gen\_fr\_to\_send() randomly select a destination address from the destination address table and a source address from the source address table with the preconfigured probability and increase the corresponding sequence number by one. gen\_fr\_to\_send() also generate randomly the length of the frame between 64 and 1522. The chosen destination address, the source address, the sequence number, the generated frame length and the counter CircCnt are assigned to the variable frame\_to\_send.

#### 4.1.5 The Queue

The two sending queues and the two receiving queues are normal queues defined with the Frame type using the queue template in the Standard Library of C++. It can execute normal operations for a queue structure like push, pop, and return the size of the queue.

## 4.1.6 The Lookup Tables

The proposed lookup tables are circular buffer, hash table with open addressing and aging, hash table combined with circular buffer. Because the structures and operating principles of each kind of table are already introduced in the previous chapter, it will not be repeated here. But in order to show how the concepts of each table are implemented, three important functions, namely the hash function, the searching entry function and the writing entry function are explained in detail for each type of table.

## 4.1.6.1 Circular Buffer

The circular buffer method does not use any hash functions. The flow charts of search entry and writing entry functions are illustrated in Figure 4.4 and Figure 4.5 below.

Figure 4.4 The flow chart of the searching entry function in circular buffer

Figure 4.5 The flow chart of the writting entry function in circular buffer

#### 4.1.6.2 Hash Table with Open Addressing and Aging

As stated in the chapter 3, the key which is the entry composed of the destination address, source address and the sequence number, is far from uniform, therefore the randomization should be performed before hashing.

The randomization function is chosen as the *Hashpjw()*. It coerces a key into a permuted integer through a series of bit operations on each byte in the key.

The code of *Hashpjw()* is shown in Figure 4.6 bellow:

```

int hashpjw(const void *key) {

const char *ptr;

int val;

/*Hash the key by performing a

number of bit operations on it. */

val = 0;

ptr = kev:

while (*ptr != '\0') {

int tmp;

val = (val << 4) + (*ptr);

if (tmp = (val & 0xf000000)) {

val = val ^ (tmp >> 24);

val = val ^ tmp;

}

ptr++;

}

}

```

Figure 4.6 The hashpjw() funtion

This function is simple and proven to have a nice performance on randomizing the key. The bit operation is very suitable for implementing in the FPGA.

There are 3 probing sequences used: the linear probing, the quadratic probing, and the double hashing. The hash functions of each probing sequence are listed as following:

For linear probing and quadratic probing

$h(x) = x \mod m$

For double hashing

$h(x) = x \mod m$   $g(x) = x \mod (m-1)$

Note here m is not chosen as a prime number. The reason for doing this is that the mod operation of a prime number cannot be synthesized in FPGA, other reason is mod a number of power of 2 can simply be realized by only taking the  $\log_2 m$  number of the least significant bits. The effect of such choice must be evaluated through the simulation.

The flow charts of searching and writing entry function are shown respectively in Figure 4.7 and Figure 4.8.

Figure 4.7 The flow chart of the searching entry function in hash table with open addressing and aging

Figure 4.8 The flow chart of the writing entry function in hash table with open addressing and aging

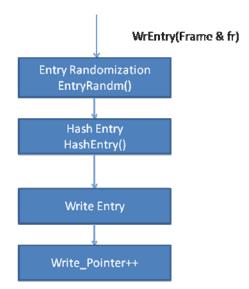

## 4.1.6.3 Hash Table Combined with Circular Buffer

For the hash table combined with circular buffer, the hash randomization function is still *Hashpjw()*. The hash function is:

$$h(x) = x \mod m$$

The flow charts of the searching and writing entry function are shown in Figure 4.9 and Figure 4.10 respectively.

Figure 4.9 The flow chart of the searching entry function in hash table combined with circular buffer

Figure 4.10 The flow chart of the writing entry function in hash table combined with circular buffer

## 4.1.7 The Receiving Processing

The receiving processing is a function which watches the receiving status on the two lines. Its tasks include searching and writing the entry of the received multicast frame and to the node dedicated unicast frame in the table for rejecting duplicated and circular frames, pushing the frame in the receiving queue if the frames are not found in either of the two tables. If frame comes at the same time, it should compare the two frames and make decisions. The way this function works is shown in Figure 4.11.

Figure 4.11 The flow chart of the receiving processing

## 4.1.8 Send Coordinator and Sending Port Use Count Down

Because each node has only one send port on each line, the using of the sending port must be coordinated between sending and forwarding. The basic principle of coordination is: the *forwarding always has the priority*. The reason for doing that is to ensure the traffic in the ring is not delayed by the frames injected by the nodes.

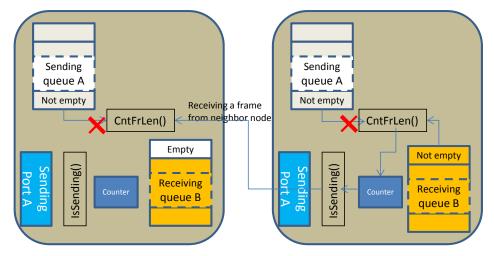

The functionality of send coordinator and frame length counting down is realized by two functions: CntFrLen() and *IsSending()*.

The CntFrLen() implement the count-down functionality and thus simulates the time behavior of the network. For example, if the receiving queue is not empty, the length of the frame on top of the queue will be loaded to the counter and the counter is counted down by one at each simulation time. During counting down, no new loading is allowed.

This stands for the time of using the sending port by this frame. After the counter reaches zero, the frame will be popped from the queue, and assigned to the sending port waiting to be received by the node next to it.

For the node next to this node, the receiving port should also be used when count-down is ongoing at the sending porting of this node. The node next to this node should sense that it is sending a frame. This *IsSending()* function tells the neighbor node that it is sending. If a frame requires to be sent a frame to the ring, but it sense the neighbor node is sending a frame towards it, the sending to the ring should not be allowed, because the receiving frame will probably be forwarded later. This operation principle is shown in Figure 4.12.

Figure 4.12 The sending coordination principle and frame length counting down

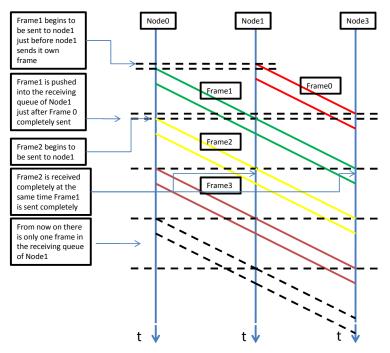

With such principle, the number of the frames in the receiving queue will never exceed 1 on the precondition that all frame are of the same length. Let us consider the following scenario:

Figure 4.13 The number of frames in the receiving queue will never exceed 1