# Network Protocols for Embedded Devices

## with Dynamic Hardware/Software Mapping

Florian Deragisch

Master's Thesis MA-2011-28 November 2011 until May 2012 Advisors: Ariane Keller, Daniel Borkmann, Dr. Stephan Neuhaus Supervisor: Prof. Dr. Bernhard Plattner

#### Abstract

The rise of today's Internet began with the emergence of the *World Wide Web* and hasn't come to an end ever after. The technological advances in the fields of processor architectures and memory storage technologies in the last decade were tremendous. As a result, new devices such as smartphones, tablets or sensor nodes came to market that connect more users and machines to the Internet. This rapid development stands in contrast to the evolution of the Internet which has been going slowly. A static one-size-fits all protocol stack is no longer suited to provide an efficient communication environment that takes the diversity of devices into account. Imagine a sensor node running a full fledged TCP/IP stack which is highly inefficient in terms of battery lifetime. Fortunately, more sophisticated approaches have been proposed to take these resource constraints into account.

There have been substantial efforts in the field of dynamic and reconfigurable communication protocol stacks: The Autonomic Network Architecture (ANA) is a novel network architecture that enables flexible and dynamic rearrangements of the protocol stack. A lightweight version of ANA called LANA makes use of those principles and concepts and even provides a high-performance software framework for network protocol stacks. Another research project, called EmbedNet has been proposed as a hardware design of adaptive network nodes. Like LANA, it relies on ANA and provides means for partial reconfiguration during run-time in hardware.

Those frameworks are meta-architectures which means they lack of protocol functionality. To this end, the scope of this thesis is protocol development for network modules that can be executed in hardware (EmbedNet) or software (LANA). In order to allow for a run-time transition from software to hardware execution and vice versa, we have developed a state transition mechanism.

With the implementation of Huffman (compression protocol) and CRR (reliability protocol), we have shown that computationally expensive algorithms (Huffman) offer more potential for optimized hardware implementations, than simple flow control protocols (CRR). Huffman coding, for instance, offers a lot of parallelism that can be exploited, whereas CRR is limited by the width of its data bus. A Huffman hardware module has been designed and implemented that runs up to 22 times faster than the software module. The expected speed-up for the CRR hardware implementation is rather small, because software and hardware execution is very similar.

Memory access time to fill internal buffers is the common bottleneck that is shared among software and hardware implementations. Additionally, the implemented concept of state transition mechanism, allows flexible task migration for future protocols added to the protocol stack. At last, this thesis brought the involved frameworks one step further with respect to reliability, usability and functionality. New mechanisms and extensions have been designed and implemented that will be of great value for future projects.

#### Acknowledgements

With this master thesis I complete my studies in Information Technology and Electrical Engineering at the Swiss Federal Institute of Technology (ETH) Zurich.

I would like to express my gratitude to a number of people who have contributed to this thesis. First of all, I would like to thank Prof. Dr. Bernhard Plattner for supervising my thesis.

Further, I would like to thank my advisors Ariane Keller, Daniel Borkmann and Dr. Stephan Neuhaus. I am thankful for all the effort and help of Ariane, especially concerning hardware design and implementation decisions. Special thanks to Daniel who helped me a lot with his software and Linux kernel knowledge throughout the course of this thesis. Thanks to Stephan for sharing his expertise and experience in writing papers and giving talks.

I deeply appreciated the interesting and helpful discussion during our weekly meetings. I learned a lot of new things during the process of this thesis and enjoyed working on this project. It would not have been possible to write this thesis without the support and help of my advisors.

Zurich, June 2012

Florian Deragisch

# Contents

| 1        | Intr | roduction                                  | 9         |

|----------|------|--------------------------------------------|-----------|

|          | 1.1  | Motivation                                 | 9         |

|          | 1.2  | Goals                                      | 11        |

|          | 1.3  | Outline                                    | 12        |

| <b>2</b> | Rel  | ated Work and Background Information       | 13        |

|          | 2.1  | ANA                                        | 13        |

|          |      | 2.1.1 Architectural Abstractions           | 13        |

|          |      | 2.1.2 Core Machinery                       | 15        |

|          | 2.2  | LANA                                       | 15        |

|          |      | 2.2.1 Components                           | 16        |

|          | 2.3  | ReconOS                                    | 18        |

|          |      | 2.3.1 Programming Model                    | 18        |

|          |      | 2.3.2 Execution Model                      | 19        |

|          | 2.4  | Architecture                               | 20        |

|          | 2.5  | Compression Algorithms                     | 21        |

|          |      | 2.5.1 IP Payload Compression (IPComp)      | 22        |

|          |      | 2.5.2 IP Payload Compression Using DEFLATE | 22        |

|          |      | 2.5.3 Huffman                              | 24        |

|          |      | 2.5.4 Huffman Hardware Implementations     | 24        |

|          | 2.6  | Reliability Protocols                      | 25        |

| 3        | Des  | ign                                        | <b>27</b> |

|          | 3.1  | Huffman Coding                             | 27        |

|          |      | 3.1.1 Software Module                      | 27        |

|          |      | 3.1.2 Hardware Module                      | 28        |

|          | 3.2  | Continuous Repeat Request                  | 30        |

|          |      | 3.2.1 Software Module                      | 30        |

|          |      | 3.2.2 Hardware Module                      | 32        |

|          | 3.3  | State Transition                           | 34        |

| 4        | Imr  | blementation                               | 37        |

|          | 4.1  | Huffman Coding                             | 37        |

|          |      | 4.1.1 Software Module                      | 38        |

|          |      | 4.1.2 Hardware Module                      | 43        |

|          | 4.2  | Continuous Repeat Request                  | 48        |

|          |      | 4.2.1 Software Module                      | 49        |

|          |      | 4.2.2 Hardware Module                      | 54        |

|          | 4.3  | State Transition                           | 58        |

|          |      | 4.3.1 Software Module                      | 59        |

|          |      | 4.3.2 Hardware Module                      | 60        |

| <b>5</b>     | Eva    | luation                           | 65  |

|--------------|--------|-----------------------------------|-----|

|              | 5.1    | Testing Platform                  | 65  |

|              | 5.2    | Testing Methodology               | 65  |

|              | 5.3    | Huffman Coding                    | 66  |

|              |        | 5.3.1 Software Module             | 66  |

|              |        | 5.3.2 Hardware Module             | 69  |

|              | 5.4    | Continuous Repeat Request         | 73  |

|              |        | 5.4.1 Software Module             | 73  |

|              |        | 5.4.2 Hardware Module             | 77  |

| 6            | Con    | clusion and Future Work           | 81  |

|              | 6.1    | Conclusion                        | 81  |

|              | 6.2    | Future Work                       | 82  |

| Re           | eferei | nces                              | 85  |

| A            | Tasl   | <b>C</b> Description              | 89  |

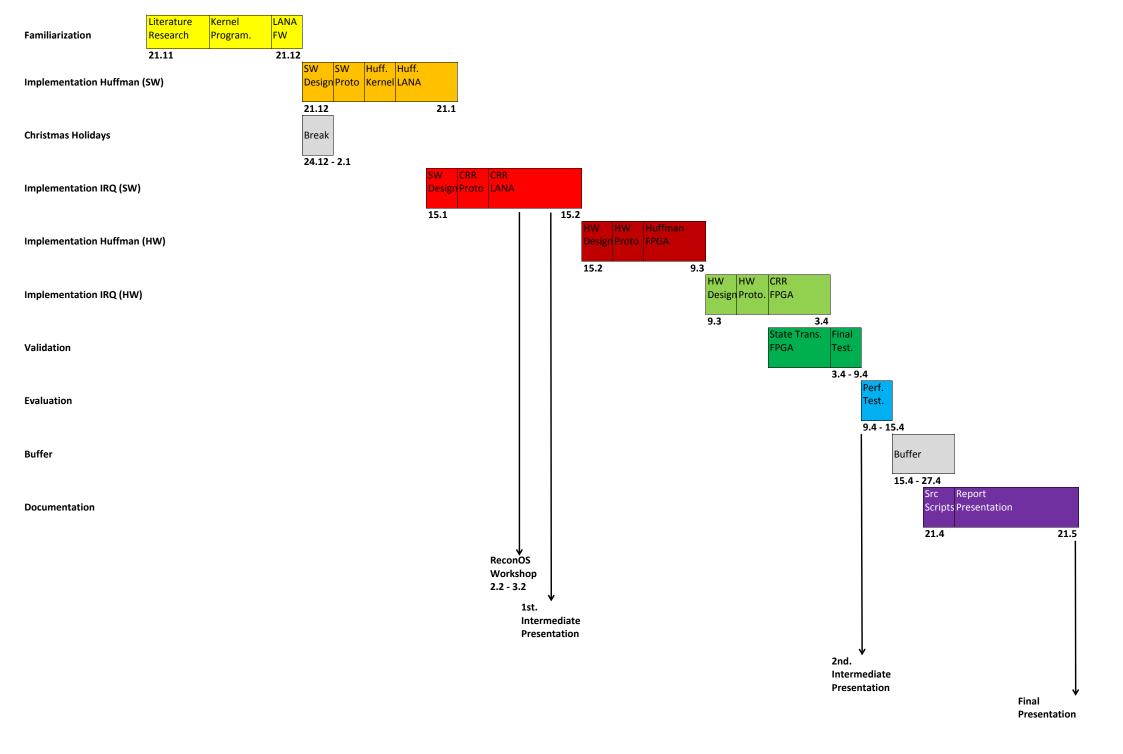

| В            | Pro    | ject Plan                         | 95  |

| $\mathbf{C}$ | Get    | ting Started                      | 97  |

|              |        | Loading Functional Blocks in LANA | 97  |

| D            | Con    | tent of the Attached CD           | 99  |

| $\mathbf{E}$ | Dec    | laration of Originality           | 101 |

# List of Figures

| 1.1                 | Static TCP/IP stack compared to a flexible ANA stack[1] 11                               | L |

|---------------------|------------------------------------------------------------------------------------------|---|

| $2.1 \\ 2.2 \\ 2.3$ | ANA sample network    14      LANA sample configuration    16      Hardware thread    18 | 3 |

|                     |                                                                                          |   |

| 2.4                 | System on Chip including software and hardware                                           |   |

| 2.5                 | Huffman Tree                                                                             | 5 |

| 3.1                 | Hufman Coding in software                                                                | 3 |

| 3.2                 | Huffman hardware architecture                                                            | ) |

| 3.3                 | CRR sender procedures 32                                                                 |   |

| 3.4                 | CRR receiver procedures                                                                  |   |

| 3.5                 | CRR hardware architecture                                                                |   |

| 3.6                 | State transition mechanism                                                               |   |

| 0.0                 |                                                                                          | ĺ |

| 4.1                 | Ethernet frame and Huffman header format (length in bytes) 37                            | 7 |

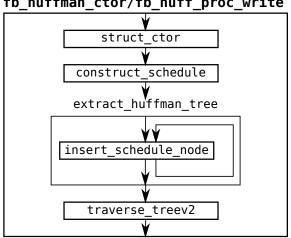

| 4.2                 | Overview of the Huffman constructor                                                      | Ĺ |

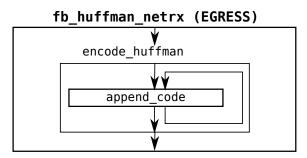

| 4.3                 | Involved Huffman functions for encoding                                                  | 2 |

| 4.4                 | Involved Huffman functions for decoding                                                  | 2 |

| 4.5                 | Encoding and decoding in hardware 43                                                     | 3 |

| 4.6                 | FIFO interface between NoC and FB                                                        | 5 |

| 4.7                 | Coding FSM                                                                               | 7 |

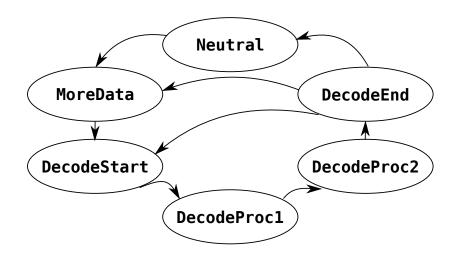

| 4.8                 | Decoder FSM                                                                              | 7 |

| 4.9                 | Frame and CRR sender format (Data) (length in bytes)                                     | 3 |

| 4.10                | Frame and CRR receiver format (ACK) (length in bytes) 49                                 | ) |

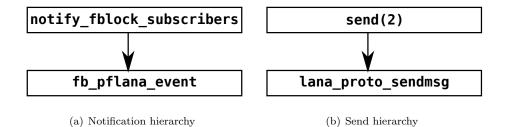

|                     | Hierarchy of involved functions                                                          | 1 |

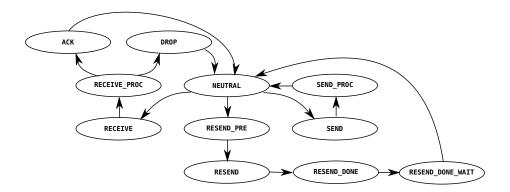

| 4.12                | CRR sender FSM                                                                           | 3 |

|                     | CRR receiver FSM                                                                         | 7 |

|                     | Protocol state data structure                                                            | ) |

|                     | State transition in software                                                             | ) |

|                     | ReconOS state transition FSM                                                             |   |

|                     | State transition FSM                                                                     |   |

|                     |                                                                                          |   |

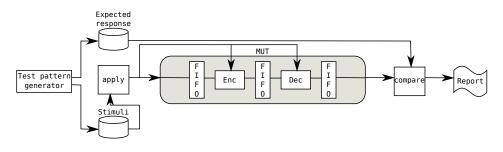

| 5.1                 | Huffman setup                                                                            | 3 |

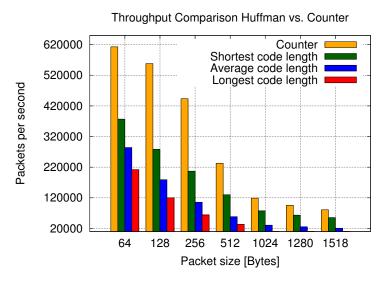

| 5.2                 | Huffman module throughput                                                                | 3 |

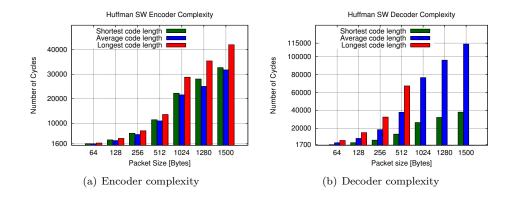

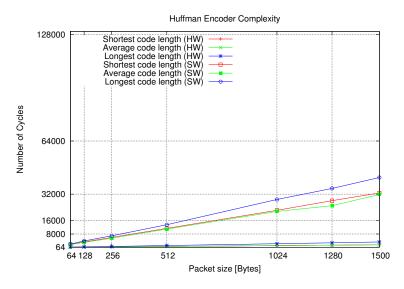

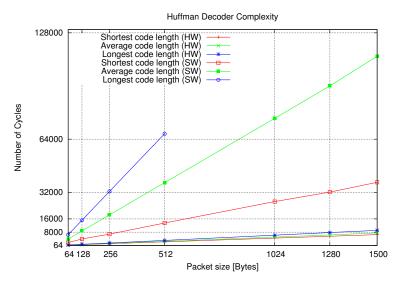

| 5.3                 | Huffman complexity                                                                       | ) |

| 5.4                 | Huffman testbench                                                                        | ) |

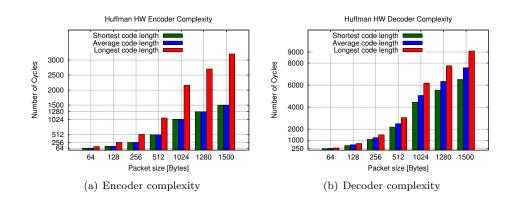

| 5.5                 | Huffman complexity                                                                       | L |

| 5.6                 | Encoder comparison                                                                       | 2 |

| 5.7                 | Decoder comparison                                                                       | 3 |

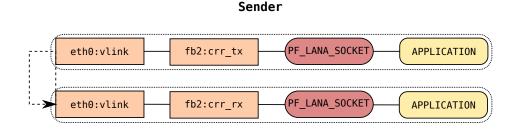

| 5.8                 | CRR setup                                                                                | 1 |

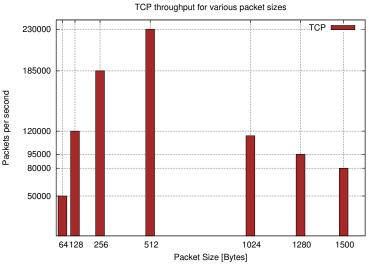

| 5.9                 | TCP throughput                                                                           | 5 |

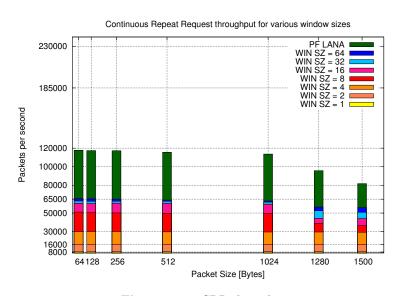

| 5.10 | CRR throughput                 | 76 |

|------|--------------------------------|----|

| 5.11 | CRR testbench                  | 77 |

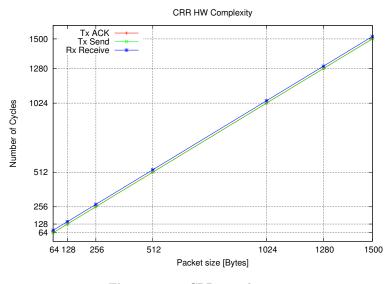

| 5.12 | CRR complexity                 | 78 |

|      | Bind FB to a socket            |    |

| C.2  | Waiting user space application | 98 |

## Chapter 1

## Introduction

## 1.1 Motivation

The origins of today's Internet reach back into the late 1950's when the U.S. Department of Defense wanted a command-and-control network that could survive a nuclear war. As a consequence, the Advanced Research Projects Agency (ARPA) was founded as a defense research organization. ARPA's focus eventually turned to networking, when it was trying to figure out how to provide remote access to computers. It was not until the late 1960's that an experimental network called ARPANET went on air [2]. As time went by, additional networks were connected to the ARPANET which became increasingly complex. As a result, new protocols that are still being used today such as Domain Name System (DNS), were created to organize hosts into a hierarchical system. The Internet exploded in size with the emergence of the World Wide Web (WWW) in the early 90's and has been growing ever since.

The Internet has changed a great deal since the early days and its primary objective is no longer to survive a nuclear war, but to provide the base for its future growth. The Internet is part of our daily life and changed not only in terms of users, but also concerning usage and networking devices. There is a demand to be connected at all times. Be it to communicate through social media, check emails, do online banking, join a video conference, or browse the Internet for information. In the last decade, new devices with a need to connect to the Internet showed up on the horizon. Mobile phones turned into smartphones that offer more advanced computing ability and connectivity. Sensor networks and other embedded systems are used to gather and evaluate data from sensor nodes, or send data to remote servers, for instance. The PermaSense project is an example for such a network under extreme conditions [3]. Devices as well as their offered services have different requirements to the underlying protocol stack regarding quality of service (QoS), functionality, flexibility, performance, resource usage, power usage, reliability as well as safety and security. A static one-size-fits-all protocol stack is unsuited to fulfill these challenging requirements.

Let's take a look at mobile and embedded devices: A critical requirement for mobile devices is long operation time. Ways to extend operation time are to use bigger batteries, which is rarely an option, or to reduce power consumption. A major part of a sensor nodes' energy consumption is caused by communication and data transmission[4]. A sensor node may not need a full fledged communication stack running on the device at all times. At times only basic connectivity is sufficient to fullfil the needs, for instance by using a low-power protocol stack [5], whereas at other ocasions some specific functionality may be required. The difficulty is that with current protocol stacks, we are not able to change the stack dynamically. We would need a flexible communication stack that can be changed during run time, depending on our needs and external events. Further energy savings could be achieved through custom-made packet structures which would result in smaller header size and therefore less overhead. Another interesting approach is to migrate functionality from software to hardware and vice versa, as required. Software offers a higher level of flexibility, whereas hardware offers higher performance or lower energy consumption, depending on its design goals.

In contrast to devices and network usage are the underlying protocols such as TCP/IP that haven't changed conceptually since they had been made public. At the time IP was developed, no one expected such a widespread use as we are experiencing today. The Internet and especially IPv4 became victims of their own success: IPv4 address shortage is a real problem, and as of 15 April 2011, APNIC was the first regional Internet Registry to run out of freely allocated addresses [6]. The potential IPv4 address shortage was recognized early and the IEFT began working on the intended succeedor of IPv4 called IPv6 [7]. However, the IPv6 deployment is proceeding slowly [8].

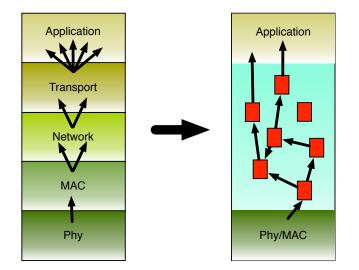

The cases above show both the inflexibility and inefficiency of the current protocol stack and the difficulties to deploy changes. All of these weaknesses can be overcome with a flexible protocol stack in hardware and software: A first step towards this goal has been taken with the Autonomic Network Architecture (ANA) [9]. The objective of autonomic networking is to enable autonomous formation and parametrization of nodes, and to introduce self-awareness and self-expression into the system. This means that the systems will sense its environment through sensors or its internal states (self-awareness) and react appropriately in a smart way (self-expression). The protocol functionality in ANA is split up in so called functional blocks (FB). The functionality of such a FB can vary from a simple forwarding block up to a full TCP/IP stack. Those blocks form a graph-like construct that abstracts the system's protocol stack. FBs can be added, removed, linked and delinked during run time. Therefore functionality can be added, changed or removed from the protocol stack without restarting the operating system or any of its networking components. See Figure 1.1 for a comparison between a legacy network protocol stack and a flexible ANA stack. A better performing and lightweight version of ANA (LANA) that runs in the Linux kernel was developed [1].

To provide sufficient performance or energy efficiency, it is necessary that protocols can not only be executed in software but also in hardware. This implies that not only the software but also the hardware protocol stack can be changed during runtime. First steps towards such an adaptive networking environment have been presented in Lubbers et al. [10] and Keller et al. [11] and follows the concepts developed in the ANA project on a hardware level. Networking protocols are split up into smaller blocks the same way it was introduced for ANA. The core technology to enable flexibility is the utilization of run-time reconfigurable hardware. The target system is a reconfigurable System on Chip, an embedded device equipped with an FPGA. Further, an abstraction for programming reconfigurable CPU/FPGA systems was provided [12] that hides software/hardware boundaries. A multithreaded programming model had been extended towards reconfigurable hardware. Thread interaction and integration of software and hardware threads is built upon previous research which presented an execution environment called ReconOS [12],[13]. Further research efforts combing ReconOS and ANA principles, resulted in a reconfigurable networking environment called *EmbedNet*.

This master thesis focuses on the networking aspect of EPiCS[14] (*EmbedNet*). EPiCS uses the network architecture presented from the ANA project as a basis. LANA and EmbedNet are meta-architectures in the sense that they don't offer any protocol functionality. To this end, we develop a compression and reliability proto-

col in this thesis that can be run as functional blocks in either software (LANA), or hardware (EmbedNet). In addition, they can be migrated from software to hardware or vice versa. To enable migration, a transition mechanism was necessary which would transfer the internal protocol state and set up new functional blocks accordingly.

Compression protocols are interesting for devices with limited resources such as sensor nodes or embedded devices for efficiency reason. Compression can help to increase the energy efficiency of sensor nodes when transferring data. Further, it increases the bandwidth utilization, because the same amount of information can be sent with less data. We chose to implement the Huffman coding algorithm, because its algorithm offers a high level of parallelism that can be exploited. This parallelism is required for a fast hardware implementation where we expect to see a big speed-up. Further, the Huffman algorithm is often used as a back-end to other combined compression methods such JPEG or Vorbis [15].

Reliability protocols are critical for correct data transmission between nodes. We chose a Continuous Repeat Request protocol with selective repeat strategy, because it offers flexibility and performance through the choice of its window size. A reliability and compression functional block provide an efficient protocol stack to transfer large amounts of data in a network.

Figure 1.1: Static TCP/IP stack compared to a flexible ANA stack[1].

## 1.2 Goals

The goal of this master thesis is to develop several networking protocols for Em-bedNet. Those developed protocols should run both in software and hardware. For protocols to be exchangeable, it is critical that they have exactly the same functionality, such that tasks can be migrated. Those protocols need to be implemented in C for execution in software and in VHDL for the execution in hardware. To allow for dynamic changes in the mapping of protocols to either hardware or software, a mechanism for transferring protocol state between the two implementations is needed. Depending on the used protocol, this state transition mechanism transfers internal data such as sequence numbers, frames or configuration data between functional blocks.

The implemented functional blocks will be evaluated against their software and hardware counterpart. Two protocols with specific characteristics and different

expenses in computation time were chosen in order to evaluate system bottlenecks as well as strengths and weaknesses of hardware and software implementations.

## 1.3 Outline

The structure of this thesis is as follows: Chapter 2 (Related Work and Background Information) presents the context of this thesis, the ANA architecture and its principles in more detail. Next, the LANA framework, which was used as the underlying foundation for the protocol stack in software, is presented. ReconOS as the foundation of Embednet is introduced and also current research in the fields of compression algorithms and reliability protocols. In chapter 3 (Design) we look into the design and architecture of software and hardware components, as well as the state transition mechanism. Chapter 4 (Implementation) delves into implementation specific details and presents implementation optimizations. We also point to limiting factors, bottlenecks and faced challenges throughout the implementation process. Functional verification and a performance evaluation where we compare software and hardware execution is done in chapter 5 (Evaluation). Next, we present testbenches and experiments used to test correct functionality. The conclusion and an outlook into future work can be found in chapter 6 (Conclusion and Future Work).

## Chapter 2

# Related Work and Background Information

Research projects that are related to this thesis are covered in this chapter. We will begin with a quick overview of ANA's architecture and principles. Next, we introduce its lightweight successor LANA, which is used as a software framework to build a flexible software protocol stack. ReconOS provides our software-hardware interface and is handled in the next section. Finally, we talk about compression algorithms and reliability protocols, as well as available hardware implementations.

## 2.1 ANA

EmbedNet [11] is part of the EPiCS project and focuses on the introduction of selfawareness and self-expression in computer networks and how to realize this goal in hardware. ANA is the underlying concept of our software and hardware frameworks and is presented in this section.

ANA defines a framework and execution environment that enables network stacks to operate in a continuously changing environment. A major principle of ANA is to strive for flexibility and genericity on all levels of its architecture. There are no rigid specifications such as protocols or header fields. ANA is a framework to host and interconnect different multiple heterogenous network instances. ANA, unlike the Internet, does not know a unique and globally shared addressing scheme. The core abstractions that build ANA's architecture and allow to model communication systems with a simple but structured framework concept are described next:

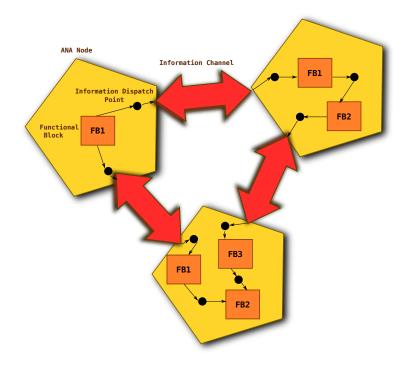

## 2.1.1 Architectural Abstractions

Network compartments model the ANA world from a coarse-grained point of view. A network compartment is a homogenous network region with respect to addresses, packet formats, transport protocols and other services. Each compartment is free to use whatever addressing or routing protocols it wants. However, each compartment must support a generic *compartment API* in order to offer access to its communication services. Network compartments can be modelled as black-boxes that support a generic communication API. An Ethernet segment, an IPv4 network, or a peer-to-peer-system could be a possible network compartment.

In each network compartment, a distributed set of protocol entities collaborate in order to provide communication services to other compartments. Information channels abstract the nature of those communication services (unicast, multicast, broadcast, datagram, reliable stream, etc). When interacting with a compartment, an entity really interacts with a software component implementing the compartment's operation. Those components are called function blocks.

- **Functional Blocks (FBs)** abstract any protocol entity generating, consuming, processing and forwarding information in ANA. ANA's protocol stack is built of functional blocks, that can vary greatly in complexity and size. A functional block can be as simple as a forwarding module or as complex as a full fledged TCP/IP stack.

- **Information Dispatch Points (IDPs)** are inspired by network pointers [16] and are similar to file descriptors in Unix systems. Functional blocks are always accessed via one or multiple IDPs attached to it. This binding of an IDP is dynamic and can be changed during runtime which offers the possibility to reconfigure the network stack. The binding between IDPs and FBs are stored in the core forwarding table of the ANA node and are fully decoupled from addresses and names. ANA's next hop entity is always defined by an IDP.

- **Node compartments** are basically ANA nodes that are a network themselves composed by the functional blocks running on the host. Node compartments are similar to network compartments, except that they don't provide information channels. This allows functional blocks to discover each other and interact inside the node compartment like with other network compartments.

Figure 2.1: ANA sample network

#### 2.1.2 Core Machinery

- Information Dispatch Points (IDPs) are identified by a 32-bit integer and are always accessed via their numerical values. The information dispatch table (IDT) stores the bindings between IDPs and FBs in each ANA node. The IDP object structure keeps track of various information such as its owner that created the IDP, its callee that is bound to it, its status and its visibility. A key feature of IDPs is the rebinding ability during run time on demand. Since the data flow should not be disrupted, it is crucial that FBs are able to continue using their IDPs, even during rebinding. When performing IDP rebinding, it is necessary to migrate the state that a FB maintains for a given IDP.

- **Event notification system** allows the autonomic entities of a system to react to networking changes. The system's scope is node-local and allows certain blocks to subscribe to certain events in order to be informed at a later stage, in case any of these events take place. The supported events are such as when an IDP is deleted, redirected, unpublished, busy, or ready to receive data. These events allow a functional block to witness network changes and dynamically adapt to new conditions. Such a behaviour is required to promote autonomic algorithms and reduce human interventions.

## 2.2 LANA

This chapter covers the lightweight version of ANA which is called LANA [17]. It shares the basics of its architecture and principles with ANA, so we will only point out LANA-specific features, that are relevant to understand how it is operating. We will look more into implementation details this time as compared to ANA, because LANA was the framework used for our compression and reliability protocols in software.

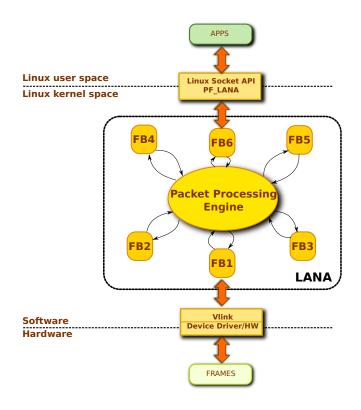

LANA is a complete redesign of ANA from scratch that aims at a slim code size and better optimized code. Various optimizations took place such as pass by reference, instead of value for network packets which are forwarded between functional blocks. The whole code runs in Linux kernel space only which improved the performance and reduced code size, because existing kernel functions and data structures could be reused. As in LANA, functional blocks build up the protocol stack. LANA's core consists of the following elements:

- **Packet processing engine (PPE)** calls all functional blocks that are connected with each other in a graph. It basically works like a switch and forwards packets to their next hop.

- Functional block builder creates new functional block instances.

- Functional block notifier dispatches event messages between functional blocks.

- **Functional block registry** and other helper data structures manage created functional block instances.

- **User space configuration interface** performs various functional block configuration tasks such as block binding.

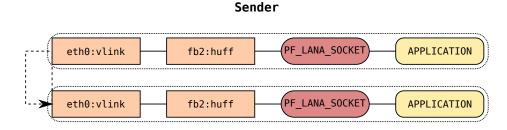

Some functional blocks can be part of the *virtual link layer* (vlink), which represents the interface between device driver and the LANA system. The connection between LANA and user space on the other hand is established through the *BSD* socket layer.

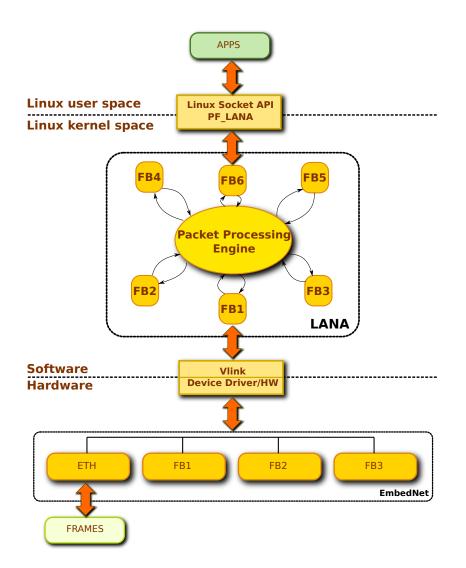

Figure 2.2: LANA sample configuration

### 2.2.1 Components

Figure 2.2 shows a sample configuration of LANA on our system. We will now briefly discuss the different components and how they interact with each other.

**Functional blocks** build up LANA's protocol stack. LANA is basically a metaarchitecture or a framework without any protocol functionality. Functional blocks are indirectly accessed through their information dispatch point, similar to ANA. The protocol stack is built by connecting different functional blocks with each other and adding up more and more functionality.

Binding and unbinding is realized by event messages. Therefore, functional blocks can subscribe to an arbitrary number of other functional blocks. Connected blocks are automatically subscribed to each other. Event messages can also be used to send protocol specific messages to other functional blocks. The message notifier interface is independent from the packet data interface. During run time, it is possible to replace functional blocks, possibly with a newer version, for maintenance or updating reasons. The IDP can be transfered to the new block without other functional blocks being aware of this.

We distinguish between functional block modules and functional block instances:

- **Functional block modules** are Linux kernel modules that provide a constructor and destructor for its functional block instance and further used functions.

- **Functional block instances** are memory structures with a private data area which is initialized and deinitialized by the corresponding functional block module.

The **functional block builder**'s task is to create functional block object instances. Two functions are registered to the functional block builder, namely the constructor and destructor. Both of these functions need to be implemented specifically for each functional block, because private data parts may vary between FBs. Some struct members of the private data structure are mandatory, because they are used for protocol stack configuration. Once an FB is no longer in use, it is the destructor's task to clean up internal data and to free allocated memory from this FB.

The **functional block notifier** notifies FBs about new events (e.g. binding) or configuration instructions. The functional block notifier construct is distributed across all FBs, which means that each block needs to keep track of its subscribed block and its subscriptions to other blocks.

All active FB instances are stored within the **functional block registry** which consists of two functionalities. A FB's IDP can be retrieved through its name, and a FB's structure though its IDP. We can address a FB instance from user space by its name, whereas in kernel space addressing is done through IDPs.

The core of LANA is called **packet processing engine (PPE)**. Its main task is to call one functional block after the other. Each FB provides a network packet receive function handler that is invoked from the packet processing engine for every packet passing through the protocol stack. It is also the FB's responsibility to either drop or forward a packet. Forwarding is done through writing source and destination IDP into the private area of the socket buffer structure. The destination IDPs are received through configuration notifications and stored internally in their private data. The FB changes the private area of the socket buffer structure according to its internal configuration in a similar way like a network router would change a packet's MAC address. Next, the receive handler returns by telling the PPE what to do with this packet. In case the packet should be forwarded, the PPE maps the IDP address to a pointer to the structure of the functional block instance. After that, the receive handler function of the next FB in line is invoked. This procedure continues until the protocol stack either reaches a dead end or the vlink/pf lana socket.

The PPE further contains a backlog socket buffer queue, which can be used for newly created socket buffers from inside a FB. Newly created packets can be placed in the backlog queue from outside of the context of the PPE.

Besides the socket buffer, information about the path direction is given to the PPE and the FB's receive handler. We differentiate between **ingress** (towards user space) and **egress** (towards PHY).

The **virtual link** can be seen as the entry/exit point for frames from/to the PHY. It represents the glue from the OS to the LANA protocol stack. FBs in this layer are special cases that behave differently than regular FBs and implement the underlying network technology such as Ethernet, Bluetooth or others.

The **BSD** socket layer is similar to the virtual link layer except that it provides the interface between LANA (kernel space) and our application that opened the socket (user space). FBs in this layer need to provide common system calls from the Berkeley sockets API.

Finally, all LANA configurations are controlled from user space through two user space applications, fbctl and vlink. The fbctl tool on the one hand, performs all FB related configurations like creation or deletion of FB instances, binding, unbinding or subscription to other blocks, as well as replacing FB instances with another during runtime. vlink, on the other hand, controls FB of the virtual link layer.

## 2.3 ReconOS

ReconOS [12] is an execution environment which is based on existing embedded operating systems and extends the multithreaded programming model from the software domain to reconfigurable hardware. ReconOS is targeting CPU/FPGA systems for creating flexible multithreaded applications. Software and hardware threads integrate and communicate seamlessly and transparently with the operating system and its services.

#### 2.3.1 Programming Model

Portability and flexibility are two major long term objectives of the ReconOS programming model. Therefore ReconOS tries to reuse established interfaces and functionalities from existing APIs. The following operating system objects are provided for ReconOS applications:

- **Threads** represent the basic units of execution that build an application in ReconOS. Synchronization and communication is achieved by using other operating system objects.

- **Semaphores and Mutexes** control synchronization, protect critical code or manage access to shared resources.

- Shared memory, message queues and mailboxes provide means for inter-process communication. Mailboxes and message queues can provide both communication and synchronization at the same time.

Since all interthread activity uses those objects, it is not necessary for a ReconOSthread to know whether its communication or synchronization partners are located in hardware or software. This not only provides complete transparency but also portability to other platforms, as long as those operating system objects are supported.

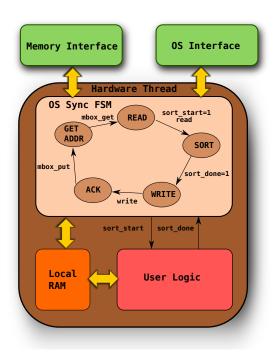

ReconOS software threads are POSIX-threads and handled by the standard OS scheduler, and therefore independent from ReconOS extensions. Things are different from a hardware point of view: Hardware tasks run concurrently. Furthermore, hardware description languages such as VHDL offer no mechanisms to implement blocking calls. To this end, a hardware thread's interacting operating system is managed by a single sequential state machine. The state transition in the synchronization state machine depends on control signals from the operating system interface (OSIF). Only after a previous operating system call has returned, the next state can be reached. It is the developer's task to split a hardware thread into a collection of user logic modules and a synchronization state machine.

Listing 2.1 shows the basic idea of such a state machine. We will remain in STATE\_GET\_ADDR, as long as we haven't received a message from a message box. Only after that will be able to update the current state.

Hardware threads take the same scheduling and stack size parameters as a software thread. These threads are used for the hardware thread's associated delegate thread running in software. Delegate threads will be explained in more detail in Section 2.3.2. It is assumed that the hardware thread is already present in the reconfigurable fabric, when creating a hardware thread in software.

Operating system objects will almost always be shared among different threads. Software threads access shared resources through global variables, for instance, accessible by all threads. This approach does not work when dealing with hardware threads. ReconOS therefore associates an array of resources with every hardware thread. The thread designer needs to define integer constants that act as indices of the the resource array, and use the symbolic constants as arguments. Further, ReconOS can directly access same memory areas as software threads, which allows for efficient sharing of data among threads.

```

reconos_fsm: process (i_osif.clk,rst,o_osif,o_mem,o_ram) is

variable done : boolean;

begin

case state is

when STATE_GET_ADDR =>

osif_mbox_get(i_osif, o_osif, MBOX_RECV, addr, done);

if done then

if (addr = X"FFFFFFF") then

state <= STATE_THREAD_EXIT;</pre>

else

len <= conv_std_logic_vector(RAM_SIZE,24);

addr <= addr(31 downto 2) & "00";</pre>

state <= STATE_READ;</pre>

end if;

end if;

when STATE_READ =>

memif_read(i_ram,o_ram,i_mem,o_mem,addr,X"00000000",len,done);

if done then

sort_start <= '1';</pre>

state <= STATE_SORTING;</pre>

end if;

end case:

end process;

```

Figure 2.3: Hardware thread

### 2.3.2 Execution Model

Hardware threads require a run-time environment to connect them to an existing operating system kernel. Carefully defined mechanisms for synchronization and communication between hardware circuitry and the operating system are necessary. In Reconos this is the task of the operating system interface (OSIF) which connects to the hardware thread's OS synchronization state machine and local RAM. On the other side, it connects to the system memory bus (PLB) and an OS control bus (DCR).

A fundamental aim of ReconOS is transparency of thread-to-thread communication and synchronization. This way we can easily replace a software thread with a functionally equivalent hardware thread. Every hardware thread in ReconOS is associated with exactly one software thread, it's *delegate*. The delegate thread's responsibility is to execute operating system calls on behalf of its corresponding hardware thread. As a result, the hardware thread is hidden behind his delegate thread and appears like a normal software thread to the operating system. Delegate threads are standard OS threads with additional parameters to access the OSIF hardware.

## 2.4 Architecture

The given development environment for the reconfigurable system on chip (rSoC) is a Xilinx ML605 evaluation board that comes along with a Virtex6 FPGA [18]. Among others, the ML605 offers, among others, the following features:

- Virtex 6 FPGA

- 512 MB DDR3 Memory

- 128 Mb Platform Flash

- System ACE CF and CompactFlash Connector

- 10/100/1000 Tri-Speed Ethernet PHY

Xilinx' Microblaze softcore is used as a CPU in our system. It is a highly configurable 32-bit Harvard architecture processor [19]. This system provides the performance to run a Linux system, which is used for the LANA software framework and the ReconOS software-hardware interface. The FPGA is big enough to leave additional space needed for our functional block modules.

Figure 2.4 shows the whole architecture of the rSoC. In the hardware domain, we have a PHY from the Ethernet interface and several hardware functional blocks. Those FBs are interconnected with each other and pass their frames from one block to another. As in software, the complexity of those functional blocks can vary significantly. The internal structure of those blocks are ReconOS-specific and were presented in Section 2.3.1.

In hardware the passing of frames between FBs is independent from ReconOS and is the task of a Network on Chip (NoC) [20]. The NoC works like a normal network that consists of routers and switches in hardware that forward packets along their way depending on their routing tables. The internal addressing of this NoC follows ANA's principles with each FB having different IDPs. It is basically LANA's counterpart in hardware.

The software hardware interface consists of ReconOS that is used to control the hardware threads through an FSM, and the NoC that can pass frames from software to hardware and vice versa. Frames are passed through a shared memory that resides in RAM and acts as a ring buffer. ReconOS can also be used to configure and initialize FBs. It can also be used to collect the state or internal data from a hardware thread.

LANA that resides in Linux kernel space, builds the software protocol stack. The vlink is responsible to forward and receive frames coming and going to the hardware.

Figure 2.4: System on Chip including software and hardware

Sockets pass frames between kernel space and user space. The structure of the graph can be configured through user space tools that bind FBs.

Finally, there are the applications running in Linux user space, that open LANA sockets, used to interact with the LANA protocol stack.

## 2.5 Compression Algorithms

In this section we give an overview of suitable compression protocols for network frames and their hardware implementations. What follows is an elaboration of those different protocols and why we chose this specific protocol to implement. Finally, we want to introduce some existing opencores and other research projects and point out how they differ from my implementation.

The reasons to implement a compression protocol for a flexible network stack are diverse: Compressed data not only increases the effective transmission rate, but it also makes more efficient use of bandwidth. Further, smaller packet sizes increase energy efficiency, because power consumption decreases. As a trade off, the compression and decompression may require additional cycles in software or additional circuitry in hardware. This added complexity results in an additional delay [21]. We argue here that the advantages outbalance the disadvantages, especially when compression and decompression runs in hardware. Besides payload compression protocols, further header compression protocols exist such as described in Degermark et al. [22], and Bormann et al. [23]. As opposed to other available compression algorithms, our protocol needs to be lossless. After decompression, the frame must be exactly the same as it was prior to compression.

#### 2.5.1 IP Payload Compression (IPComp)

The IP Payload Compression protocol (RFC 3173) [24] reduces the size of IP datagrams by compressing datagrams in order to increase the communication performance between two nodes. This is especially useful when communication is over a slow or congested link. It is proposed that compression and decompression are realized through either CPU capacity or a compression coprocessor.

IPComp has the disadvantage that small datagrams are likely to expand as a result of compression overhead. Hence, seperate protocol header is necessary which is responsible for the expansion of small payloads. To this end, the protocol follows a non-expansion policy, that only transmits packets in compressed form, when its size is smaller than the original packet's size. Before utilizing the IPComp protocol, two nodes must first establish a connection, called IPComp Associaton (IPCA). There is no default compression algorithm for IPComp and it is even possible to choose different algorithms for each direction. IPComp is more like a compression protocol framework, because it does not suppose any compression algorithms to be used.

#### 2.5.2 IP Payload Compression Using DEFLATE

RFC 2394 describes how to integrate the DEFLATE compression algorithm into IPComp [25]. The DEFLATE algorithm is widely used today by the famous PKZIP and gzip compressors, or by the freely distributed zlib library [26]. The algorithm was designed by Phil Katz and its details can be found in Deutsch [27].

The DEFLATE algorithm can be used for an arbitrarily long input data stream, using only an a priori bounded amount of intermediate storage, and hence is well suited to be used in data communication. It further compresses data efficiently and comparable to the best currently available general-purpose compression methods and is not covered by any patents [27].

The achievable compression ratio is highly depending on the input data set. English texts usually compress better than executable files [27]. The algorithm is made up from two other compression algorithms, namely **Huffman coding** [28] and **LZ77 compression** [29].

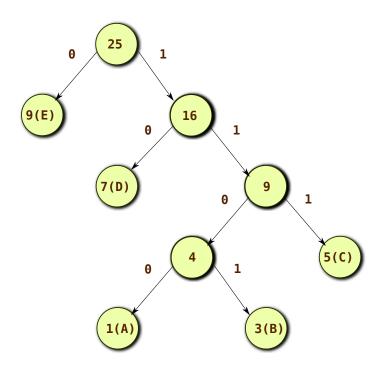

Huffman coding is a form of prefix coding, which means that there is no valid codeword in the system, that is a prefix of any other codeword [30]. For instance {11, 10} would be a valid prefix code, wheras {11, 110} would not, because after reading two bits it could either be the first code, or the second code. The algorithm starts by sorting and assembling the alphabet depending on their weight. Weight means the frequency or likeliness of a code element. The two elements with the lowest weights are chosen and linked to a parent node. Those two nodes are now the leafs of this parent node with the smaller one being on the left side. The parent node's weight is the sum of his two children nodes. Next, the two nodes with the smallest weight are chosen from all the nodes, including the parent nodes. They are linked to a parent node again and this continues, until we have one big tree with all the nodes connected to it. In order to extract the code words, the tree needs to be traversed for every character from our alphabet starting from the root node. Taking the left edge results in adding a 0, wheras the right edge adds a 1 to the bitstream. Figure 2.5 shows the resulting Huffman tree and Table 2.1 the corresponding codes.

Figure 2.5: Huffman Tree

| Char | Weight | Code |

|------|--------|------|

| А    | 1      | 0011 |

| В    | 3      | 0010 |

| С    | 5      | 000  |

| D    | 7      | 01   |

| Е    | 9      | 1    |

Table 2.1: Huffman code table

LZ77 compression works by scanning the data for repeated patterns. A sliding window is used to buffer the previous input data stream. When the next sequence of characters from the data to be compressed has been seen before in the sliding window, the input sequence will be replaced by a distance and a length. The distance describes the position of this stream in the sliding window and the length represents the number of characters, that are identical. RFC 2395 proposes using LZS compression algorithm for IPComp, which is similar to LZ77 [31].

The DEFLATE algorithm first uses the LZ77 algorithm to replace sequences that occur multiple times in the data stream. Next, the Huffman coding module is building its alphabet and code table from the already compressed data. In RFC 1951 the following Huffman coding schemes can be selected:

- Compression with fixed Huffman codes : The same code is used for all data frames

- Compression with dynamic Huffman codes : For each data frame a specialized code is created

### 2.5.3 Huffman

Our main field of application that we had in mind when looking for a compression algorithm was the transmission of different data types between nodes. As a starting point, we are interested in applications such as a chat between nodes, or to transfer books. We want our implementation to be feasible for small and large packet sizes. Therefore, a large header structure, like IPComp is using, was not an option. The same holds true for dynamic Huffman codes, that analyze bitstreams and build the corresponding Huffman table on the fly. This would have resulted in a much bigger design, not only for software, but also for hardware with higher resource requirements and bigger latencies. Each packet would need to carry its own Huffman table, which was used for encoding. The decoder would decode the received data based on the transmitted Huffman table. Fixed Huffman codes are fine for languages, because the frequency variations of each char are rather small.

The implementation of the DEFLATE algorithm in software and hardware was simply out of this thesis' scope. We therefore chose to implement a Huffman module in software and hardware, which is also part of the DEFLATE algorithm. Since functional blocks can be dynamically linked with each other, a later LZ77 module could be used to build up the DEFLATE algorithm on our flexible protocol stack.

#### 2.5.4 Huffman Hardware Implementations

In this section, we cover some existing Huffman implementations in hardware from current research and existing open cores. Our main goal is to maximize the performance throughput of our hardware modules and operate at high frequencies of roughly 100 MHz.

A hardware implementation is described in Rigler et al. [32] for Huffman and LZ77. The implementation was done for dynamic Huffman codes but does not present any raw numbers such as frequency and performance or elaborate on code sizes. [33] presents various Huffman implementations that follow JPEG, MPEG and plain Huffman standards. JPEG and MPEG standards are lossy and therefore not comparable to our implementation. The used code size remains unmentioned in this paper, so it's difficult to compare with our approach. The achieved frequency of this implementation was close to 10 MHz which is too low for our reconfigurable system on chip, and therefore not suitable. In fact most Huffman implementations on FPGA from current research follow the JPEG compression standard such as Acasandrei et al. [34] that achieved 100 MHz in a parallel design. Further examples are Agostini et al. [35] and available OpenCores implementation for a JPEG decoder [36].

Current research focused more on JPEG and MPEG codec implementations. Our approach aims at a highly pipelined and parallel running encoder and decoder, that offer the flexibility to dynamically change our code alphabet during run-time. The architecture of our compression modules will be presented in the next chapter.

## 2.6 Reliability Protocols

To implement a realibility protocol was a consequence of our first choice to implement a compression protocol. When developing a chat or file transfer application, we need to be sure, that, i.) packets arrive at the destination host, and ii.) that they arrive in the correct order. The transfer of large files is not possible without the guarantee that packets arrive reliably and correctly. Todays most famous network protocol that offers reliability is the **Transmission Control Protocol** (TCP). TCP is the protocol of choice when a reliable link needs to be set up between two nodes. Zandy et al. [37] extends the reliability of TCP by detecting failures to TCP connections and preventing applications from becoming aware of them in the context of mobility. Unfortunately, TCP's implementation is very complex, and thus not implementable in hardware with a reasonable amount of effort. Since TCP is a flow control protocol, it is not well suited to be implemented in hardware anyway, because the expected speed up is negligible. However, an approach to migrate some parts of TCP to hardware gained in popularity in recent years: A so called TCP Offload Engine [38] takes over CPU expensive tasks such as checksum and sequence number calculations, sliding window calculations, connection establishment and other key features of TCP. The idea is to designate those tasks to hardware to reduce interrupts to the host CPU, copy fewer bytes over the system bus and reduce CPU requirements for the protocol stack processing.

The **Reliable User Datagram Protocol** (RUDP) is another transport layer protocol that provides reliable data transmission [39]. It's situated between TCP, that adds too much complexity and overhead, and UDP, that lacks guaranteed-order packet delivery. RUDP's list of requirements is as follows:

- Reliable delivery of packets

- Only retransmit segments that were lost and not full blocks

- Sequenced delivery is optional

RUDP is not a formal standard and has not been proposed for standardization. According to Partridge et al. [40] there were some problems with the specifications that have never been fixed.

Most of the current research related to transport and reliability protocols, is done in the context of sensor networks [41],[42]. Stann [42] evaluates on the placement of reliability on different levels of the protocol stack. Those presented protocols are designed especially for wireless links between sensors nodes. We are aiming at a more general approach that fits our flexible protocol stack and can be used for a wide variety of system architectures.

Tanenbaum [43] introduces a variety of reliable network protocols like **Idle Repeat Request** (IRQ) and **Continuous Repeat Request** (CRR) with changing complexity. Some of these presented implementations are similar to our approach, a CRR protocol, which will be presented in the next chapter.

Research in the field of reliability protocols outside of sensor networks seems to be extensions to TCP for wireless/ad hoc communication, probably because of the dominant role of TCP. Most of the presented papers deal with mobility and faulty links in a sensor network context, but those problems are concerning layer one, the physical link, and not the transport layer. Research and implementation towards hardware seem inexistent. This is probably due to the inflexibility of hardware, compared to software, and the small expected speed up from a hardware implementation. 26

## Chapter 3

# Design

The following chapter shows the architecture of the used flexible protocol stack in software and hardware. We explain the interactions between software and hardware components and their interfaces. Additionally, design decisions concerning Huffman compression and Continuous Repeat Request modules are presented from a software and hardware point of view. Finally, we present the state transition from software to hardware and vice versa.

## 3.1 Huffman Coding

### 3.1.1 Software Module

The Huffman Linux kernel module is encoding or decoding incoming payload data for a given alphabet. This alphabet could be preset as a default alphabet, which is used when the module is loaded, or it can be set dynamically at a later point in time through a proc filesystem call [44]. The module consists of the following components:

- Packet Reception Handler: Invoked for incoming and outgoing frames (to/from FB)

- Event Notifier Handler: Binding and unbinding to other FBs

- **FB Constructor:** Allocation and intialization of the private data structure. Is invoked when adding the FB

- **FB Destructor:** Deinitialization and deallocation of the private data structure. Is invoked when removing the FB

- Module Init/Exit: Linux kernel module constructor and destructor. Are invoked by insmod and rmmod when loading/unloading the module

- Huffman Routines: All Huffman related functions responsible for building the Huffman tree, extracting code words, encoding and decoding data

Next, we describe how the code base is extracted from our alphabet:

Our chosen area of application was the compression of text. We configured our system with an alphabet for English language. However, the underlying system can be used for any language. As a base for our alphabet we chose bytes, because for most programming languages a **char** (1 byte) is used to express characters. There are other languages that contain more characters than our alphabet, or special characters such as the umlauts in the German language. In order to support those

kind of languages, a base change to multiple bytes would be necessary, such as UTF-16 or UTF-32 [45].

The American Standard Code for Information Interchange (ASCII) is a characterencoding scheme that is based on the English alphabet. The alphabets we used, mostly contain a subset of the ASCII alphabet including all characters, numbers, punctuation characters and other special characters.

In order to obtain the weight of each member in the alphabet, it is necessary to do a letter frequency analysis. We could use a precomputed letter frequency table, or write a script that counts all the different letters in a large textfile, such as a book for example. Next, all our letters are sorted from the smallest to largest weight (frequency) in increasing order.

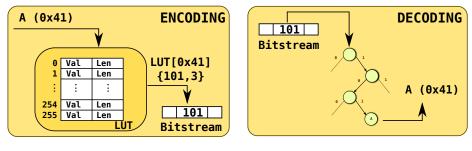

Once our alphabet with its weight is set up, we build our Huffman tree as it was described in Section 2.5.2. Now that we have the Huffman tree, we extract the Huffman code for each letter in the alphabet. We traverse the tree for all possible leafs. Each leaf is a letter from our alphabet and its corresponding Huffman code is the path, which was chosen to reach it. As mentioned earlier, the path on the left adds a 0 and the path on the right adds a 1. The whole bitstream is stored as an integer together with its length. The length is required, because the value 5 could be 101 or 0000101, for instance. The values and lengths are stored in a lookup table with 256 indices. The indices represent the ASCII value of the original character.

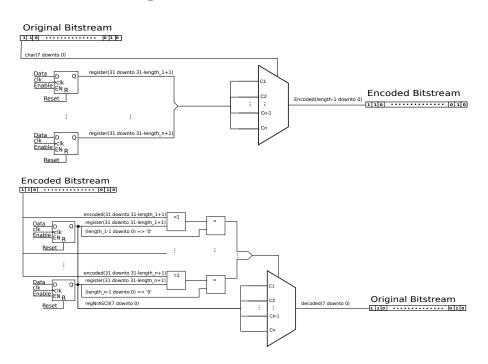

Therefore, encoding is just a quick jump to the right index in our table. Once we read the code, we just need to shift it to the correct position and append it to the encoded bitstream. The encoding procedure is shown in Figure 3.1(a).

The decoding is more complicated: We are faced with an arbitrary long bitstream and don't know how long our code word is going to be. Therefore, each time we traverse the Huffman tree according to the bitstream starting from the root. Once a leaf is reached, we can be sure that it is the decoded character, since all characters are leafs in a Huffman tree. The reason being that Huffman is a prefix code. Figure 4.4 shows how the Huffman tree is traversed until the original character is extracted.

(a) Huffman encoding method

(b) Huffman decoding method

Figure 3.1: Hufman Coding in software

#### 3.1.2 Hardware Module

From a hardware point of view, we have more options and freedom to design our architecture compared to software. We assume, the main problem and bottleneck of our software implementation is the decoding. We need to process incoming data bitwise, because we don't know where the boundaries between different characters will be. Possibilities to exploit parallelism are limited on today's processor architectures. There are systems with up to 8 CPU cores, but the size of our code

alphabet will be much larger than this. However, things look different for hardware implementation using concurrent processes.

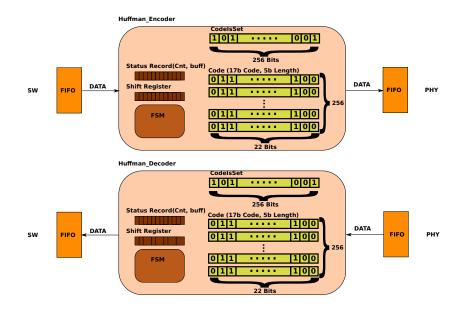

Figure 3.2: Huffman hardware architecture

Figure 3.2 shows the structure of our Huffman FB in hardware. The hardware module contains the following elements:

- **Register Bank:** A bank of 256 rows that store the codewords (comparable to the LUT in software)

- **256-bit Register:** A register that stores which codes were set in the register bank

- Shift Register: A shift register is to process the header of a packet

- Status Records: Stores internal data

- Finite State Machine: Controls the data input and output flow of the module

#### **Register Bank**

The most important part is provided by the memory(register bank): In order to fully exploit possibilities of parallelism that we are given in hardware, and fullfil the flexibility requirements, we need to store our codewords in clock enabled D-Flip-Flops. The clock enable signal works like a write enable that makes sure that data is not overwritten accidentally. A register bank is used to store the codewords and their lengths. Those values need to be precomputed in advance and then written to a Huffman module. In our design, we accomplish this through the ReconOS interface from the operating system. Those register banks consist of 256 register rows that store the values that are given from the ReconOS interface and the state machine. Next to the register bank, there is another 256-bit long register that keeps track of the ASCII chars that were set in the code alphabet. Each bit represents one row of the register bank. The codes are stored in the position of their ASCII code. For instance, Figure 3.2 shows code words being stored in 22 bits. 17 bits are used for the code word, and 5 bits for the length.

#### Finite State Machine

The finite state machine (FSM) is responsible to detect new incoming frames and change its state accordingly. Before the module starts encoding or decoding, it needs to know whether the packet is a valid Huffman packet. Therefore, it needs to write the incoming data into a shift register to compare the Ethernet type of a packet with its Huffman-specific header. Once a Huffman frame has been detected, the FSM switches its internal state and the coding starts.

#### **Buffer Control**

When designing the architecture, one major difficulty was having variable code lengths. The length of a code for our chosen alphabet may vary between 3 and 17 bits (or more for larger alphabets) depending on its weight and the total number of members in the alphabet. The encoding maps a character of 8 bits to a code word of 3 to 17 bits, whereas the decoding maps a code word of 3 to 17 bits to a character of 8 bits, for instance. To overcome this challenge, an internal data structure that keeps track of data buffer, data buffer pointer and packet length was introduced. Those data structures in VHDL, called records, are very similar to the well known structs from other programming languages.

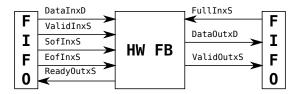

#### I/O

All FBs are directly connected to an asynchronous First-In, First-Out (FIFO) memory. The FIFO not only contains the data of our frames, but it also controls the Huffman-internal FSM through its signals. The FIFO signals when a new frame starts and an old frame ends. On the other hand, our hardware modules need to do the same when writing the data into the output FIFO. A more detailed lowlevel description of the interface between hardware FB and FIFOs will take place in Chapter 4.

## 3.2 Continuous Repeat Request

#### 3.2.1 Software Module

The Continuous Repeat Request (CRR) module introduces a reliability protocol to the LANA stack. Every data transfer is acknowledged on the receiver side such that the sender knows a frame was transmitted successfully. The CRR FB in LANA is made up of the following subroutines:

- Packet Reception Handler: Invoked for incoming and outgoing frames (to/from FB)

- Event Notifier Handler: Binding and unbinding to other FB

- **FB Constructor:** Allocation and intialization of the private data structure. Is invoked when adding the FB

- **FB Destructor:** Deinitialization and deallocation and of the private data structure. Is invoked when removing the FB

- Module Init/Exit: Linux kernel module constructor and deconstructor, which are invoked by insmod and rmmod when loading/deloading the module

- **CRR Routines:** Are responsible for queueing incoming frames, buffering outgoing frames, controlling sequence numbers and windows

- **Packet Timers:** Timers are tracking open (unacknowledged) packets and control the retransmission of lost or delayed packets

- **Open Packets Buffer:** Is a linked list, that buffers all open (unacknowledged) packets. The oldest packet is in the first position. Buffering is necessary, because we may need to retransmit frames in case of loss or delay

- **Packet Queue:** New packets are queued in a linked list, when the transmission window is full

The buffer is used to store packets that have been sent already and are kept in the buffer until the appropriate acknowledgement has been received received. The queue is a simple FIFO queue that stores packets which are sent at a later point in time. The CRR module was split up in a sender and a receiver. Next, we introduce the architecture and concepts of both modules separately:

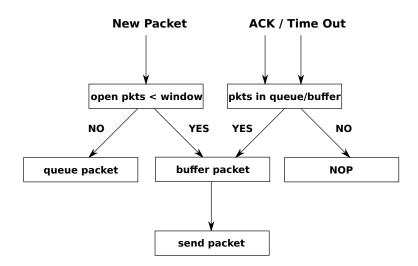

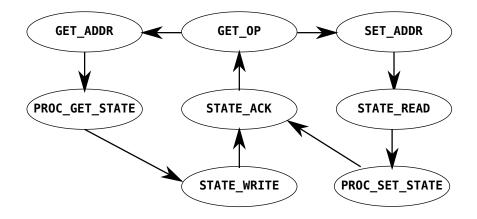

The **CRR sender module** is responsible for providing reliable data transmission in our protocol stack. Each packet destined for transmission eventually invokes the sender's packet function handler. In contrast to Idle Repeat Request (IRQ) [46], CRR offers the possibility and flexibility to send several packets at once. The number of open (unacknowledged) packets is defined by the sender's window size. As long as the number of open (unacknowledged) packets is smaller than the window size, arriving packet headers are tagged, processed accordingly, and sent out directly. Note that all open packets need to be buffered, because of potential retransmission. In case that the number of open packets has reached the maximum, which is the window size, then the packet is stored in a queue for later transmission. If the packet has been received successfully, we will receive an acknowledgement (ACK) from the receiver, which states, that the frame was received successfully. The ACK triggers a decrease of the number of open packets. Hence, the next frame can be sent. The next frame will be fetched from the queue and buffered before transmission. Each packet starts a timer before it leaves the sender module. Frames or ACKs that are lost along the way cause a timeout to occur. If the corresponding ACK arrives before the timer runs out, the timer is stopped and restarted when the next frame is sent. If the timer runs out, we reschedule the oldest frame for retransmission and move it to the end of the buffer list. The oldest packets reside in the beginning of the buffer list, the same holds true for the queue. Again, the buffer stores open (unacknowledged) packets, whereas the queue (FIFO queue) stores packets that are sent next. The basic logic of the sender is pictured in Figure 3.3.

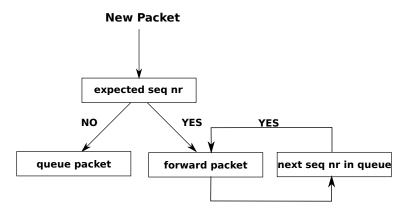

The **CRR receiver module** is the counterpart to the sender module and responsible for forwarding data frames in the correct order to the higher level protocols, as well as sending ACKs for each received frame. The architecture on the receiver side is much simpler, because we only need a packet queue to store out of order packets. The receiver expects to receive a frame with a certain sequence number. Sender and receiver need to be configured in exactly the same way, such that they have the same window size. When a frame is received, the sequence number is checked. If it matches the expected sequence number, the frame is forwarded to the user space. The expected sequence number is then incremented. If there are unforwarded packets in the queue (out of order packets), their sequence numbers are compared to the next expected sequence number. If they match, they are forwarded as well and the expected sequence number is incremented again. This continues until the queue is

Figure 3.3: CRR sender procedures

either empty or the sequence number doesn't match. Each received frame that fits the CRR frame structure and Ethernet type is acknowledged, even if it is an old frame that has been received before. ACK frames could have been lost or delayed along the way. This way, the sender doesn't know that the receiver has already received it successfully and retransmits the frame again. Figure 3.4 shows the basic control flow from the receiver side for valid frames.

Figure 3.4: CRR receiver procedures

### 3.2.2 Hardware Module

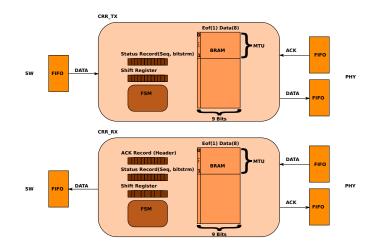

The CRR hardware implementation differs from the Huffman module in many ways: CRR is a control flow protocol that introduces reliability into our data transmission. Unlike Huffman, it doesn't involve computationally expensive operations that could be done much more efficiently. CRR contains a lot of memory accesses e.g. frames need to be buffered for potential retransmissions. The hardware module, in contrast to the software module, does not contain a queue. Memory is sparse on an FPGA and we simply cannot queue frames the same way as we did in software. Therefore, we only buffer open (unacknowledged) packets and read a new packet every time an ACK is received. There is a small delay introduced through the CRR module, because the header needs to be received completely, before the module decides, whether it is a valid CRR frame or if it's an old CRR frame. However, the predominant part of the delay is caused by the transmission time from sender to receiver and back, due to the protocol design.

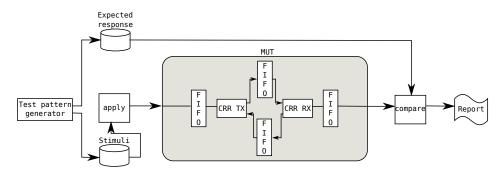

Figure 3.5: CRR hardware architecture

Figure 3.5 shows the structure of our CRR FB in hardware. The following elements make up for its functionality:

- **BRAM:** An area and performance optimized memory that is used to buffer frames

- Shift Register: A shift register is used to verify the header of a packet

- Status Records: Stores internal data

- Finite State Machine: Controls the data input and output flow of the module

- **Timer Processes:** Counters are used to control the timeout and retranmission of open packets

Memory is the most important resource of the CRR hardware module. It is implemented using block RAM (BRAM) which is embedded on the FPGA. The **sender module** uses the BRAM to buffer frames, because in case of a timeout they would have to be retransmitted.

The **receiver module** needs to store out of order packets, that are forwarded at a later stage, when the packet's sequence number matches the expected sequence number. Figure 3.5 shows the structure of the memory:

The memory's data width is 9 bits. The first bit is used to mark the end of the packet and the remaining 8 bits are used for the frame. Ethernet frames may vary between 64 bytes and 1518 bytes including CRC checksum [47]. Therefore, the dimension of the memory depends on the maximum transmission unit (MTU) and the window size. In order to prevent possible problems of overlapping windows, we set the maximum sequence number to twice the window size. This way, the receiver can clearly differentiate between consecutive windows. The whole memory is  $MTU \times 2 \times WIN\_SZ$ . For simple addressing of all frames in our memory, the packets start at multiples of the MTU. The address of the frame with sequence number i is:

$$Address[i] = MTU \times (i-1)$$

The shift register has the same functionality as for the Huffman module: It is used to verify the header for a CRR frame and to extract the sequence number. The FSM changes its state depending on the sequence number or on the type of the frame.

The **sender** does not evaluate the header, because all frames arriving in the sender module are tagged as CRR frames. This is done by changing the Ethernet type and adding a small CRR header. For efficiency and performance reasons, the frame is forwarded and stored in the BRAM in parallel.

A timer is started for each open packet that decrements its value each clock cycle. When the timer runs out, thus it reached 0 before the corresponding ACK arrived, the frame is retransmitted and the timer restarted. In case of several timeouts at once, they are processed from oldest to newest packet. In order not to waste bandwidth, the sender would read potential ACK frames first, before retransmitting a packet that has timed out. It may be possible that an open packet times out and at the same time, a new frames arrives that may be the awaited ACK frame. Thus, it makes more sense to read the newly arrived frame first before retransmitting the open frame.

The **receiver**, on the other side, needs to analyze the header of the frame. Invalid frames (invalid sequence number) are dropped without ACK. CRR frames with correct or incorrect sequence numbers are both acknowledged, because the sender may not have received previous ACKs, hence, the retransmission of an old (previously received) frame. Old frames are ignored internally, whereas out of order frames, frames with sequence numbers larger than the expected number, are acknowledged and stored in the memory. ACKs are sent while the corresponding frame is still being received. The hardware receiver module works exactly the same as the software module with regards to queued frames. Each correctly received frame is forwarded to higher level protocols and results in the examination of the queue. Thus, consecutive frames stored in the memory are forwarded subsequently.

The CRR modules share the same FIFO interface as we have seen for the Huffman module. One difference to be noted is the fact that there are 3 interfaces for **sender** and **receiver** each. The sender receives frames from the software side, ACKs from the Ethernet-side, and sends frames to the Ethernet side. The receiver receives frames from the Ethernet-side, sends ACKs to the Ethernet side, and forwards frames to the software side.

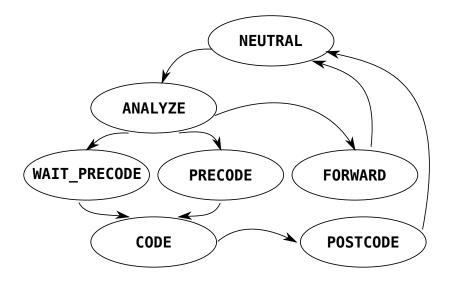

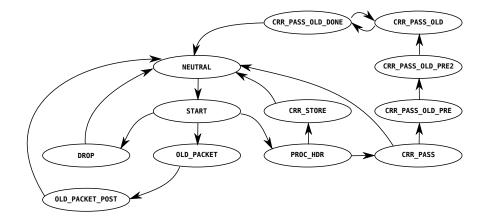

## 3.3 State Transition

To be able to change and map functionality of our protocol stack dynamically to either hardware or software, a mechanism for the state transition is needed. State transition means the migration of a protocol from software to hardware, or vice versa. The transition must guarantee that no frame loss occurs and that the end user of the system doesn't even notice the migration of protocols. For the continuous and error-free processing before and after a state transition, a transfer of the protocol state may be necessary. Further, it may be required to migrate some internal data (buffered packets) of the module as well.

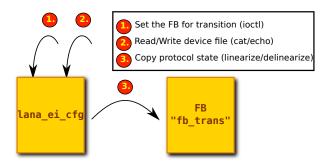

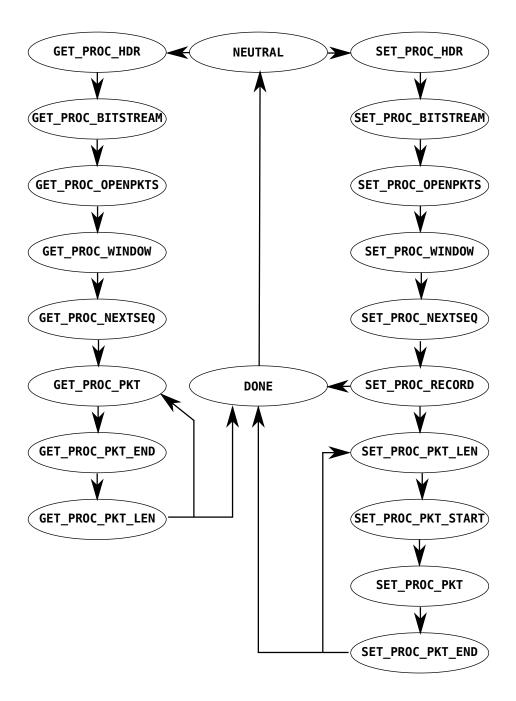

Let's take a look at CRR, for instance: Our sender module runs in software and we would like to change the execution to hardware for performance or energy efficiency reasons. The software module stored some internal data (buffered packets), which needs to be transfered to the CRR module in hardware before it can start operating. The state transition mechanism needs to transfer data such as next sequence number, open packets, buffered packets and packets in the queue. The hardware module then needs to initialize its internal structure properly, based on the internal data from the software module. The whole process of swapping tasks from software to hardware and vice versa is pictured in Figure 3.6.

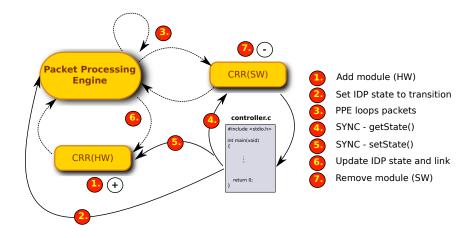

Figure 3.6: State transition mechanism

The component responsible for the state transition is a software component, called controller.c in Figure 3.6, that is in charge of the whole process. The first step (1) is to add the FB in hardware and to generate a hardware thread and its delegate thread. The FB is now present in hardware, but still not linked to our protocol stack or the packet processing engine.