Intrusion Prevention for flexible Protocol Stacks.

Stefan Kronig

Master's Thesis MA-2013-04 March until September 2013 Advisors: Ariane Keller, Dr. Markus Happe, Dr. Stephan Neuhaus Supervisor: Prof. Dr. Bernhard Plattner

### Acknowledgements

Thanks to my project advisors, Ariane Keller, Dr. Markus Happe and Dr. Stephan Neuhaus for their help and great support during the last half year. Thanks to the TIK Communication Systems Group, directed by Prof. Dr. Bernhard Plattner, for providing me the possibility to carry out this Master's Thesis in their group. This thesis was a great opportunity to put into practise many aspects of the (mostly theoretical) knowledge I gained during my studies at ETH.

Special thanks go to my parents who have always given me good advice and the needed support during my years of study.

#### Abstract

In the context of the Future Internet, recent research at ETH have developed a networking platform for flexible protocol stacks with hardware- and software support. This platform is called EmbedNet and runs on a FPGA-based system on chip. Functional blocks for the networking protocol stack can be run in hardware or in software, whichever is more optimal for the current communication scenario.

As today, also in the context of the Future Internet, security will play a crucial role. In this thesis, we pay regard to the security aspect in flexible protocol stacks, by implementing an intrusion prevention functional block for EmbedNet. The presented functional block is available as a Kernel Module written in C, as well as a hardware implementation written in VHDL. The hardware version runs directly inside the FPGA and can process packets in the full line rate of of 1 GBit/s.

# Contents

| Co | onten         | ats                                        | 5               |

|----|---------------|--------------------------------------------|-----------------|

| Li | st of         | Figures                                    | 9               |

| Li | st of         | Tables                                     | 11              |

| Li | $_{ m sting}$ | $\mathbf{s}$                               | 13              |

| 1  | Intr          | oduction                                   | 15              |

|    | 1.1           | Context of this Thesis                     | 15              |

|    | 1.2           | Motivation                                 | 15              |

|    | 1.3           | Software and Concepts used in this Thesis  | 16              |

|    |               | 1.3.1 Intrusion Prevention Systems         | 16              |

|    |               | 1.3.2 Flexible Protocol Stacks             | 16              |

|    |               | 1.3.3 The EPiCS Project                    | 17              |

|    |               | 1.3.4 ReconOS                              | 17              |

|    |               | 1.3.5 LANA                                 | 18              |

|    |               | 1.3.6 EmbedNet                             | 18              |

|    | 1.4           | Introduction to Unicode                    | 19              |

|    |               | 1.4.1 Unicode Characters                   | 19              |

|    |               | 1.4.2 UTF-8 Encoding                       | 19              |

|    | 1.5           | FPGA Board and Xilinx Software used        | 20              |

|    | 1.6           | Related Work                               | 20              |

| 2  | Uni           | code Attacks                               | 21              |

|    | 2.1           | Description of the System to be Protected  | 21              |

|    | 2.2           | Attack Categorisation                      | $\overline{21}$ |

|    |               | 2.2.1 Homograph Attack                     | 22              |

|    |               | 2.2.2 Injection of Control Characters      | 23              |

|    |               | 2.2.3 Change of Size of Requests           | 24              |

|    | 2.3           | Choosing an Attack to be Implemented       | 25              |

|    | 2.4           | UTF-8 Non-Shortest Form Attack             | 25              |

|    | 2.5           | Attacker model                             | 26              |

| 3  | Des           | ign and Implementation                     | 27              |

|    | 3.1           | Design Goals                               | 27              |

|    |               | 3.1.1 Attack to Detect                     | 27              |

|    |               | 3.1.2 Extendability                        | 27              |

|    |               | 3.1.3 Hardware and Software Implementation | 27              |

|    |               | 3.1.4 Single Packet Operation              | 27              |

|    |               | 3.1.5 Configurable Header Length           | 28              |

|    |               | 3.1.6 Statistics and Configuration         | 28              |

|    | 3.2           | Overall System Design                      | 28              |

6 CONTENTS

|   | 3.3       | Hardware IPS Design and Implementation                    | 2 | 29          |

|---|-----------|-----------------------------------------------------------|---|-------------|

|   |           | 3.3.1 IPS Hardware Thread                                 | 2 | 29          |

|   |           | 3.3.2 IPS Main Entity                                     | 3 | 80          |

|   |           | 3.3.3 Receiver Control                                    |   | 80          |

|   |           | 3.3.4 Packet Buffer                                       |   | 31          |

|   |           | 3.3.5 Packet Inspection Entity                            |   | 32          |

|   |           | 3.3.6 Sender Control                                      |   | 3           |

|   |           | 3.3.7 Interface to the Content Analysis Blocks            |   | 34          |

|   | 3.4       | Software Design                                           |   | 5           |

|   | 0.1       | 3.4.1 Constructor Function                                |   | 55          |

|   |           | 3.4.2 IPS Main Function                                   |   | 55          |

|   |           | 3.4.3 Configure Header and get Statistics                 |   | 6<br>6      |

|   |           | 3.4.4 Interface to the Content Analysis Blocks            |   | 6<br>6      |

|   | 3.5       | Software Measurements                                     |   | 6<br>86     |

|   | 3.6       | UTF-8 Non-Shortest Form Detection                         |   | 50<br>57    |

|   |           |                                                           |   |             |

|   | 3.7       | Vulnerable Application: Web Server                        |   | 89          |

|   | 3.8       | Tools                                                     | 4 | -0          |

| 4 | Vali      | idation and Evaluation                                    | 4 | 3           |

|   | 4.1       | Validation                                                | 4 | 13          |

|   |           | 4.1.1 Test setup                                          |   | 13          |

|   |           | 4.1.2 Validation of the Attack Detection                  |   | 4           |

|   |           | 4.1.3 Validation Result                                   |   | 4           |

|   | 4.2       | Evaluation Methodology                                    |   | 4           |

|   | 1.2       | 4.2.1 Test setups                                         |   | 4           |

|   |           | 4.2.2 Data measured                                       |   | 4           |

|   |           | 4.2.3 Performed tests and expected results                |   | 4           |

|   | 4.3       | Results                                                   |   | 16          |

|   | 4.0       | 4.3.1 Hardware                                            |   | 16          |

|   |           | 4.3.2 Software - best case                                |   | 18          |

|   |           | 4.3.3 Software - Real World Scenario                      |   | 19          |

|   |           | 4.6.9 Software - Iteal World Sechario                     | 1 | :0          |

| 5 | Con       | nclusion and future work                                  | 5 | 1           |

|   | 5.1       | Interpretation                                            | 5 | 51          |

|   | 5.2       | Conclusion                                                | 5 | 1           |

|   | 5.3       | Known Bugs                                                | 5 | 51          |

|   |           | 5.3.1 Double Byte Bug                                     |   | 51          |

|   |           | 5.3.2 Hardware "gives away" one Clock Cycle per Packet    | 5 | $^{52}$     |

|   | 5.4       | Future work                                               | 5 | $\tilde{2}$ |

|   |           | 5.4.1 Implement more Attacks                              | 5 | $\tilde{2}$ |

|   |           | 5.4.2 Support for Data Streams                            | 5 | 2           |

|   |           | 5.4.3 Run-time Reconfiguration of Hardware FBs            | 5 | 2           |

|   | <b>TT</b> | 1 1 1 1 1                                                 | _ | _           |

| A |           | w to get started (manual)                                 |   | <b>5</b>    |

|   | A.1       | Prerequisites                                             |   |             |

|   |           | A.1.1 Linux Workstation and other Hardware Requirements . |   | 55          |

|   |           | A.1.2 Install and configure Linux on your Workstation     |   | 55          |

|   |           | A.1.3 ReconOS Git repository and Get Started              |   | 66          |

|   |           | A.1.4 Setup FPGA Board and Xilinx Tools                   |   | 66          |

|   |           | A.1.5 Setup ReconOS                                       |   | 66          |

|   |           | A.1.6 Setup LANA                                          |   | 7           |

|   |           | A.1.7 Well done                                           |   | 7           |

|   | A.2       |                                                           |   | 7           |

|   | A.3       | Hardware IPS Usage                                        | 5 | 8           |

| $\mathbf{CONTE}$ | ENTS | 7 | , |

|------------------|------|---|---|

|                  |      |   |   |

|              | A.4 Include software IPS into ReconOS                 | 61<br>63 |

|--------------|-------------------------------------------------------|----------|

| В            | Tubles                                                | 65       |

|              | B.1 Verification of UTF-8 non-shortest form detection | 65       |

|              | B.2 Measurements: Software, best case                 | 66       |

| $\mathbf{C}$ | Task Description                                      | 69       |

| D            | Project Schedule                                      | 73       |

| Re           | eferences                                             | 77       |

8 CONTENTS

# List of Figures

| 1.1 | Traditional, static compared to flexible protocol stacks  | .7 |

|-----|-----------------------------------------------------------|----|

| 1.2 | ReconOS hardware thread abstraction                       | 8  |

| 3.1 | Overview of the entire system                             | 28 |

|     | hwt_ips.vhd – Hardware thread entity containing the IPS 2 | 29 |

| 3.3 | ips.vhd – The IPS Main entity                             | 3C |

| 3.4 | Packets pipelining                                        | 31 |

| 3.5 | packet inspection                                         | 32 |

| 3.6 | Sender control FSM                                        | 33 |

| 3.7 | Example of a packet sent via the LocalLink interface      | 34 |

| 3.8 | UTF-8 non-shortest form detection FSM                     | łC |

| 4.1 | Execution time of the UTF-8 nonshortest form detection    | 19 |

# List of Tables

| 1.1                                           | Encoding convention of Unicode code points in UTF-8                                                                                                                                                                                                                                                                        | 20                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.1<br>2.2<br>2.3                             | Representations for Dot and Slash in UTF-8                                                                                                                                                                                                                                                                                 | 24<br>25<br>26             |

| 3.1                                           | Bits which are 0 when a non-shortest form attack is present                                                                                                                                                                                                                                                                | 37                         |

| 4.1<br>4.2                                    | Characters used for testing the UTF-8 non-shortest form detection. These characters contain all possible bit lengths of UTF-8 code points. Measurement results for the real world scenario                                                                                                                                 | 45<br>49                   |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7 | All 1-byte characters used for testing.  All 2-byte characters used for testing.  All 3-byte characters used for testing.  All 4-byte characters used for testing.  Mean of processing times.  Standard deviation of processing times (in Jiffies).  Mean, median and standard deviation of processing times (in Jiffies), | 65<br>65<br>66<br>67<br>67 |

|                                               | for 1000 packets of each size, without an attack                                                                                                                                                                                                                                                                           | 68                         |

# Listings

| 3.1  | Interface to the hardware content analysis blocks                     | 34 |

|------|-----------------------------------------------------------------------|----|

| 3.2  | Definition of constants for "good" and "evil" in hardware             | 35 |

| 3.3  | Interface to the software content analysis blocks                     | 36 |

| 3.4  | Definition of constants for "good" and "evil" in software             | 36 |

| 3.5  | Pseudocode of the UTF-8 non-shortest form detection                   | 38 |

| 4.1  | Device utilisation report for our design on the Xilinx Virtex-6 FPGA. | 47 |

| 4.2  | Timing report for our design on the Xilinx Virtex-6 FPGA              | 47 |

| A.1  | Get started: Prerequisites                                            | 55 |

| A.2  | Copy hardware IPS files to ReconOS directory                          | 57 |

| A.3  | Hardware IPS usage                                                    | 58 |

| A.4  | Configure the hardware IPS using hw_sw_interface.c                    | 58 |

| A.5  | How to start the hardware IPS                                         | 60 |

| A.6  | Copy software IPS files to ReconOS directory                          | 61 |

| A.7  | Adapt Makefile and xt_nocx.c for software IPS                         | 61 |

| A.8  | Software IPS usage                                                    | 61 |

| A.9  | How to start the software IPS                                         | 62 |

| A.10 | Add more content analysis blocks                                      | 63 |

# Chapter 1

# Introduction

#### 1.1 Context of this Thesis

This thesis is in the context of the Engineering Proprioception in Computing Systems (EPiCS) Project. The goal of EPiCS is to make computing systems self-aware, in order that they can adapt to exterior influences.

In this thesis we work on the networking aspect of EPiCS, which is called Embed-Net. EmbedNet is based on Autonomic Network Architecture (ANA), a networking core intended for future Internet architectures. Instead of a static protocol stack, networking functionality is organised into specific Functional Blocks, they can be dynamically assembled to a protocol stack at run-time.

The EPiCS project maintains its own Operating System (OS), called ReconOS. ReconOS is a Linux-based OS extension which provides an abstraction of hardware resources to so-called hardware threads, which can be handled like threads or processes in the software.

The goal of this thesis is to implement an intrusion prevention block. This will be a Functional Block (FB) for EmbedNet and will be implemented in hardware and software. For the hardware version we will use ReconOS' features in order to communicate between the hardware block and the OS.

#### 1.2 Motivation

In this thesis, we will present an Intrusion Prevention System (IPS) for flexible protocol stacks. Intrusion detection and prevention plays an important role in today's computer network architectures. Large organisations rely on Intrusion Detection and Prevention Systems (IDPSs) to protect their IT assets. Network-based IDPS analyse all network traffic which enter and leaves the the organisation's network and can detect malicious activities, independently if end nodes are separately secured or not.

New threats are arising daily in the Internet, and this is unlikely to change in the future. So when thinking about concepts and technologies for the future Internet, it is advised to think about security, too. Intrusion detection and prevention is one possible approach to satisfy this need for security, also in future Internet technologies, like flexible protocol stacks.

In recent years, a new trend towards hardware-accelerated computing can be observed, like General Purpose computing on Graphics Processing Units (GPGPU), Field Programmable Gate Arrays (FPGAs), etc. Intrusion prevention systems must handle high amount of data at the full data rate of a organisation's Internet link.

16 1 Introduction

Hardware-accelerated solutions can provide more computing power and, thus, increase the overall performance of an IPS.

This thesis will present a prototype for a Network-based IPS which runs on EmbedNet, a hardware platform implementing flexible protocol stacks. This IPS will be implemented as a hardware block, was well as in software.

In order to implement a new kind of intrusion prevention, some attack had to be chosen which the IPS shall be able to detect in order to show that it works correctly. We chose to consider attacks on UTF-8 encoding. Unicode is the default encoding in HTML and XML [1][p. 1], thus its importance in today's Internet is indisputable. However, although Unicode's roots reach back to the 1990's, also in 2013 we find examples of software tools which have troubles with Unicode support<sup>1 2</sup>. Or, if we look some years back, examples of vulnerabilities in widespread software which were vulnerable to UTF-8 non-shortest form attacks: Microsoft Internet Information Services (IIS) allowed an attacker to bypass authentication mechanisms by sending a non-shortest form / character in 2009 [2], or a standard function of PHP, which was vulnerable to non-shortest form attacks in the end of 2010 [3].

These examples indicate that Unicode encoding problems are still an issue in modern software and worth to take care about in a future IPS.

## 1.3 Software and Concepts used in this Thesis

#### 1.3.1 Intrusion Prevention Systems

Intrusion Prevention Systems (IPSs), also known as Intrusion Detection and Prevention Systems (IDPS) are systems which monitor network traffic for malicious activities and also attempt to stop the detected activities. Network-based IDPS are able to analyse all network traffic. They do not rely on any end-node security applications, but can detect malicious activities in the network itself, by analysing traffic patterns or the the payload of the traffic (deep packet inspection).

Today's IPS are commonly realised in software and optimised for the static Transmission Control Protocols (TCPs)/Internet Protocols (IPs) protocol stack. In this thesis, we will lay the foundation for a network-based IPS running in hardware and software. Further, the IPS is not intended for legacy protocol stacks, but for a novel, flexible protocol stack, as it may be used in the Future Internet.

#### 1.3.2 Flexible Protocol Stacks

This inflexibility, although working quite fine for the current Internet as we know it, is not well suited for all needs of communication: For instance, it reaches its functional limit for mobile and high-delay networks, and is not suited at all for delay-tolerant networking.

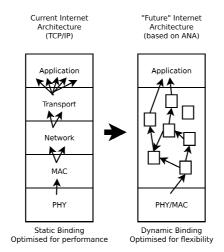

The basic idea of flexible protocol stacks is to emerge from this paradigm of static layers and create a new, modular network architecture. Network functionality is organised in Functional Blocks (FBs) (also referred to as network blocks or network elements in the literature) which can be freely connected to build a protocol stack according to the current communication needs. Figure 1.1 illustrates this. Such a network block can provide anything from simple operations like packet classification or checksum calculations, up to a complete networking stack. Examples for implementations of flexible protocol stacks are [4]/[5] or [6].

<sup>&</sup>lt;sup>1</sup>Fedora problem with the release name "Schrödinger's Cat": https://bugzilla.redhat.com/show\_bug.cgi?id=922433

<sup>&</sup>lt;sup>2</sup>Vulnerability in the VFAT file system implementation of the Linux Kernel, when converting from UTF-8: http://web.nvd.nist.gov/view/vuln/detail?vulnId=CVE-2013-1773

**Figure 1.1:** The Ideas of traditional, static protocol stacks (TCP/IP) on the left, compared to flexible protocol stacks (ANA/LANA) on the right. Figure taken from [4][p. 7].

This thesis will be implemented as a FB for a flexible protocol stack implementation.

#### 1.3.3 The EPiCS Project

This thesis is in the context of the Engineering Proprioception in Computing Systems (EPiCS) Project [7]. EPiCS is an international multi-disciplinary research project, its goal is to make computing systems more self-aware (hence proprioceptive). Proprioceptive computing systems collect information about their state and environments and are able react to them by adapting their behaviour.

EPiCS maintains the ReconOS software, which also includes LANA, an implementation of dynamic protocol stacks developed at ETH Zurich. ReconOS and LANA will be explained in the following sections.

#### 1.3.4 ReconOS

ReconOS [8] is a Linux-based Operating System (OS) which extends the threading programming model, known from software, to reconfigurable hardware. It is intended for the use on Systems on Chip (SoCs). The basic idea behind is to outsource resource intensive tasks to specialised hardware resources, while still maintaining the flexibility and simplicity of software threads.

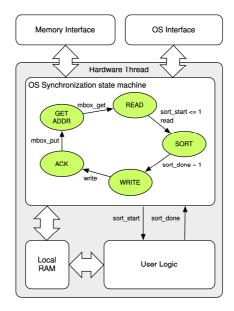

The ReconOS API simplifies the access to hardware resources from the software, by providing a variety of POSIX-like functions to communicate with these so-called hardware threads, as if they were software threads: Semaphores, mutexes, shared memory, mailboxes etc. Within the hardware, the OS synchronisation state machine controls the data exchange with the software. For instance, the software may copy data to be processed into a specified shared memory location. It then passes a message to the hardware using the <code>mbox\_put</code> call. The hardware state machine retrieves this message using (a hardware version of) the <code>mbox\_get</code>-call and can react to it, e.g. by starting the processing of the data. In the same way, the hardware can pass a message back to the software as soon as the computation is finished. Figure 1.2 illustrates this.

In the context of this thesis, the IPS will run as a ReconOS hardware thread.

18 1 Introduction

Figure 1.2: ReconOS abstracts communication to the hardware, s.t. communication with hardware threads is possible like with software threads. Figure taken from [9].

We will use mailboxes to communicate with the hardware, in order to exchange configuration messages (cf. section 3.3.1).

#### 1.3.5 LANA

Our work is focused on the networking part of EPiCS. The networking stack included in EPiCS is Lightweight ANA (LANA) [4], an optimised version of the Autonomic Network Architecture (ANA) [5] networking stack. The EPiCS project includes LANA as its networking part.

LANA is a flexible networking core, intended for future Internet architectures. Instead of a static protocol stack, networking functionality is organised into specific FBs. Different FBs can be dynamically loaded and assembled at run-time, to build a protocol stack according to the current need of communication: One may imagine a couple of battery driven devices communicating with each other: Since they are proprioceptive, they may detect that the battery level is dropping too fast and dynamically adapt the protocol stack to a less reliable, but more energy-effective one.

#### 1.3.6 EmbedNet

By combining the two ideas of hardware threads and flexible protocol stacks, a dynamic protocol stack can be built with support for hardware resources. EmbedNet [10] implements this idea by providing a SoC implementation of flexible protocol stacks, based on LANA. Parts of the protocol stack can be moved between software and hardware at run time. By doing so, EmbedNet enables developers to implement LANA FBs with high resource demand in hardware, and others in software.

EmbedNet provides separate data channel to transmit packets within the hardware: A Network on Chip (NoC) [11]. Two special hardware FBs, the Hardware to Software FB (h2s) and Software to Hardware FB (s2h), are used to transmit packets across the hardware-software boundary. These FBs are connected to the NoC to transmit packets within the hardware, as well as they use the the already presented ReconOS mechanisms like shared memory or message boxes to copy packet data

between hardware and software. In order to send and receive packets from and to the NoC, each hardware FB is equipped with a so-called packet encoder which can send data to, resp. packet decoder which receives packets from other hardware FBs via the NoC [11].

Not only the h2s and s2h can communicate with the software, but all FBs can, as they are all ReconOS hardware threads. The difference is that h2s and s2h are meant to transfer packet data to the software, all other FBs shall transfer their packet data via the NoC.

In the context of this thesis, we will use the packet decoder and packet encoder features of EmbedNet to exchange data packets with other FBs (cf. section 3.3.1).

### 1.4 Introduction to Unicode

The attack presented in this thesis is based on Unicode and the way characters are stored in UTF-8. This section shall give an overview of the most relevant principles used in Unicode.

#### 1.4.1 Unicode Characters

Unicode [1] is an international standard to represent characters. It aims to unify all of the world's writing systems and defines ways to encode multilingual text, in order to exchange text data internationally.

The standard, defines a mapping of a numeric value (so-called code point) and name for each of its characters in the Universal Character Set (UCS). It contains 1'114'112 ( $\approx 2^{20}$ ) code points, the most common characters of all languages still used today are encoded in the first 65'536 =  $2^{16}$  code points. Unicode code points are usually referred to using the U+<hexcode> notation, e.g. U+0053 is the code point with the number  $53_{hex}=83_{decimal}$ , the latin capital letter "S"<sup>3</sup>.

Unicode is compatible to the ISO/IEC 10646 standard.

#### 1.4.2 UTF-8 Encoding

Besides the mapping of characters to code points just introduced, there is a second mapping of the used code points into binary data, the so-called encoding. Unicode characters can be encoded in different forms: UTF-32, UTF-16 and UTF-8. We will only explain UTF-8, as the attack we work with is based on this encoding.

In UTF-8, characters are represented using a variable length of 8, 16, 24 or 32 bits (1, 2, 3 or 4 bytes). Early code points require less data to be stored, so 8 or 16 bits provide enough space to store them, whereas later code points need more bytes of space to be stored. Table 1.1 presents the convention how data is to be stored within the individual bytes of a UTF-8 character. The bits marked with 1 and 0 are given by the convention, while the bits market with x shall be filled with the (binary) code point number. The "max." column in the table lists the maximum length of the code point which can be encoded. The theoretic maximum of characters which can be encoded using this method is  $2^{21} \approx 2$  million.

Using variable bit lengths sounds complicated at first glance, but brings the major advantage of backwards compatibility: The first  $2^7 = 128$  code points (U+0000 to U+007F) were chosen s.t. they are identical to the widely used American Standard Code for Information Interchange (ASCII) character set. With their length of 7 bits, these code points are still short enough to be stored as 1-byte character, so their binary encoding in UTF-8 corresponds exactly to their encoding in ASCII.

<sup>&</sup>lt;sup>3</sup>Unicode character search available at http://www.unicode.org/charts/.

20 1 Introduction

| char. length | binary representation |           |           | max.      |         |

|--------------|-----------------------|-----------|-----------|-----------|---------|

| 1 byte       |                       |           |           | 0xxx xxxx | 7 bits  |

| 2 bytes      |                       |           | 110x xxxx | 10xx xxxx | 11 bits |

| 3 bytes      |                       | 1110 xxxx | 10xx xxxx | 10xx xxxx | 16 bits |

| 4 bytes      | 1111 0xxx             | 10xx xxxx | 10xx xxxx | 10xx xxxx | 21 bits |

**Table 1.1:** Convention to encode Unicode code points in UTF-8: Bits marked with x shall be filled with the code point number.

#### 1.5 FPGA Board and Xilinx Software used

As mentioned, ReconOS and EmbedNet are made for SoCs. In this thesis we use a SoC implemented on a Field Programmable Gate Array (FPGA). The used hardware is a Xilinx ML605<sup>4</sup> Evaluation board. This board is equiped with a Xilinx Virtex-6<sup>5</sup> XC6VLX240T FPGA. The board also provides all peripherals needed, such as a programming interface and Serial Console interface, external RAM for the OS, an Ethernet interface and a Compact Flash (CF) card reader to store Linux' root filesystem. The board has no hard-wired CPU, therefore we make use of a MicroBlaze<sup>6</sup> soft-core CPU.

Using an FPGA (and not an ASIC) provides the desired flexibility to reconfigure parts or all of the hardware resources needed for the current communication scenario. At present, the desired hardware configuration has to be chosen at synthesis time, but there are ambitions to make EmbedNet hardware FBs reconfigurable at run-time, which is possible with this FPGA.

To synthesise and simulate the hardware, we use the tools provided by Xilinx in the ISE Design Suite<sup>7</sup> version 13.3.

#### 1.6 Related Work

In 2012, Yang wrote an AES hardware encryption FB [12] for EmbedNet. The FB was was written as a Semester Thesis at ETH Zurich. In this thesis, we write a hardware FB as well as a software FB. The AES FB is included in the current version (September 2013) of the ReconOS git repository and uses the same same interfaces to control with the outside world, as our hardware IPS FB. In the Get Started (Section A.2), we will explain how to replace the AES FB with our IPS FB.

<sup>&</sup>lt;sup>4</sup>http://www.xilinx.com/products/boards-and-kits/EK-V6-ML605-G.htm

<sup>&</sup>lt;sup>5</sup>http://www.xilinx.com/onlinestore/silicon/online\_store\_v6.htm

<sup>6</sup>http://www.xilinx.com/tools/microblaze.htm

<sup>7</sup>http://www.xilinx.com/products/design-tools/ise-design-suite/index.htm

# Chapter 2

# Unicode Attacks

This chapter describes the different possibilities of attacks which are possible through Unicode and UTF-8. We will first introduce the system to be protected. Then, we provide an attack classification (Section 2.2) and choose an attack to be implemented in the IPS (Section 2.4). The chapter is concluded by providing an attacker model (Section 2.5).

## 2.1 Description of the System to be Protected

In Order to demonstrate and test the functionality of the IPS, we need some Software which is vulnerable to the Attacks described in section 2.4. As we use the (L)ANA Protocol stack and not a standard TCP/IP protocol stack, it is not possible to use an already existing software, it must be written by ourselves. Thus, the Software should be as simple as possible. Neverthless, the software should be somehow reusable and for demonstration purpose, the used protocols should be well-known to users.

We found that a simple web server is the ideal trade-off between these two goals. The web server should only deliver static webpages, it has no support for scripting (like CGI<sup>1</sup>, PHP<sup>2</sup>, or similar). It accepts so-called "Simple-Requests" as defined in HTML 1.0 [13] sends the requested file back to the user.

The web Server is protected against directory traversal attacks, using the following (naïve) approach: It searches the input string for 0x2E 0x2E 0x2F, which is the hexadecimal representation of ../ in ASCII or the shortest form in UTF-8. It drops any requests which contain it. However, it will not search for other (UTF-8-)representations of the ../ String.

In a more real-world like scenario, one could imagine a web application which protects itself against SQL injection attacks<sup>3</sup> by searching all input strings for 0x27, the shortest form representation of a single quote, but not for other representations of it.

# 2.2 Attack Categorisation

In the last few years, many legacy software systems were updated to support Unicode. E.g. UTF-8 has become the standard encoding for HTML files[1][p. 1], or internationalised domain names<sup>4</sup> were made possible. This obviously brings the

<sup>&</sup>lt;sup>1</sup>Common Gateway Interface

<sup>&</sup>lt;sup>2</sup>PHP Hypertext Preprocessor, http://www.php.net

<sup>&</sup>lt;sup>3</sup>https://www.owasp.org/index.php/SQL\_Injection

<sup>&</sup>lt;sup>4</sup>http://www.icann.org/en/resources/idn, e.g. domains with umlauts in German.

22 2 Unicode Attacks

advantages which Unicode was invented for, i.e. better and simpler internationalisation. But with this transition, also new attacks became possible by abusing UTF-8 characters.

Thus, attackers do not focus on breaking or exploiting vulnerabilities directly in UTF-8, but hiding an attack to the underlying system using Unicode encodings, by abusing faulty implementations of UTF-8 interpreters or converters. The Unicode Consortium provides a good overview of attacks and best practises when implementing Unicode and UTF-8 in [14]. When not stated otherwise, the attacks described in this chapter were found in this report [14].

#### 2.2.1 Homograph Attack

**Description and examples:** The attacker sends a message to the victim, using characters which look equivalent to characters well known by the victim. Although this attack is easily detectable by a computer, a human cannot tell the difference between the original and faked message. The more User Interfaces (UIs) support Unicode, the more attack vectors are present which can be exploited. Goals of the attacker can be:

- Spamming, getting through Spam filters undetected. This method is very similar to Image Spam, i.e. Spam messages where the actual text is put into image files, in order to hide it from spam filters [15].

- Try to fool the user by presenting text which looks very similar to a well-known, trusted website or Company. Examples are links to www.paypa1.com, which uses the digit 1 instead of a lower-case L, or the following link to the website of a famous Swiss bank, www.ubs.com<sup>5</sup>. Latter uses a Cyrillic Dze-Letter instead of the Latin s and is not distinguishable for a human (at least not in font used in this document). This kind of attack is known as homograph attack [16].

- Circumvent security measures, e.g. by presenting the victim a forged certificate, with a name which looks like a trusted company or organisation.

**Possible countermeasures:** In the Internationalised Domain Names (IDN) system, characters are converted to so-called compatibility-equivalent characters [17], i.e. the most simple form a character can have.

An IPS could block all requests to URLs containing non-Latin characters, but it is highly arguable if this measure is wise or not. Especially in non English-speaking countries, such requests might well be legitimate traffic and users will feel confused or hindered if they cannot access certain certain web sites that they expect to work.

Possible attacks and impact on our system: Since our system does not use any domain names (there is no DNS support yet for LANA), we are currently not vulnerable to any attack which relies on domain names. Of course, an attacker could still send forged Links to "our" users with links to any website of our server, but when the users access the webserver, the requested file or resource will most probably just not be found, which makes this attack uninteresting for an attacker. Thus we weight the likelihood and the possible impact on our system as low.

As already stated in the motivation (section 1.2), we will present a network-based IPS in this thesis. Even if our system used domain names, a network-based IPS

<sup>&</sup>lt;sup>5</sup>If you are reading this document in a PDF reader, you can try clicking on the URL and see if your browser is smart enough to inform you about the possibly fraud website.

running inside our infrastructure cannot do anything against this attack, because the attack happens on the client side. The only way to protect would be to run an IPS on "our" client's machines, too. We do not assume this scenario for this thesis, so no countermeasures are planned either.

#### 2.2.2 Injection of Control Characters

**Description and examples:** Instead of fooling the user, the attacker can also try to fool the system by encoding control characters using non-ASCII encoding. Examples for such control characters are: . and / for paths, allowing directory traversal attacks, < > for HTML (XSS attacks), and " '; etc. which allow different kinds of injection attacks.

There are different methods to inject control characters.

• All legacy control characters are within the ASCII character set, i.e. the first 127 code points of the UCS. So the preferred attack methods are to send these characters using UTF-16 or UTF-32 encoding, which are not backwards compatible to ASCII, or using UTF-8 with a non-shortest form representation instead of the shortest form (the non-shortest form representation will be explained in section 2.4).

Assume a system where the user input is passed to a program or a function A, which does input sanitising and then forwards the input to program B. A does not support UTF-8 (e.g. because it is a legacy tool which only supports ASCII), but B does. If this is the case, A will check the input, but will not detect the control characters and forward the message to B. B, thus, will interpret the full Unicode input string, including the hidden control characters. By exploiting this behaviour, the attacker could successfully bypass input sanitising.

• An attacker could send invalid Unicode characters, e.g. a byte where the first 3 bits are set to '110' (which indicates a 2-byte character, cf. table 1.1), but not followed by a second byte beginning with '10'. Depending on how the UTF-8 interpreter interprets this combination of invalid byte and the following, possibly valid, second byte, the attacker may hide control characters or control sequences.

Assume the same two processes A and B, as described before: Process A, as part of its input sanitising, searches for the string "attack". Process B just ignores (i.e. deletes) unknown or invalid characters. So, the attacker could send a string of the form "atotack", where the diamond stands for the invalid character, and this string will pass to B, unnoticed by process A. Later, the diamond character is removed by process B and it becomes "attack" again.

Similarly, the attacker can "hide" a control character in the second byte of the mentioned invalid 2-byte character: If the interpreter only replaces the first byte and ignores the others. The inverse case is also possible, the input byte can be deleted if the UTF-8 interpreter replaces all 2 bytes of the character.

Possible countermeasures: The recommended best practises according to [14] are that a converter shall substitute invalid UTF-8 bytes by the replacement character (U+FFFD), but not delete or substitute the successor byte of them. The interpretation of UTF-8 characters encoded in the non-shortest form was allowed in early Unicode versions, but is forbidden since unicode version 3.0. So, non-shortest forms must not be interpreted as valid UTF-8.

24 2 Unicode Attacks

From the IPS perspective, it would make perfectly sense to block all traffic which contains requests with invalid UTF-8 characters or non-shortest forms. Such requests are either an erroneous implementation or an attack; no matter which applies, it is extremely unlikely to be legitimate traffic.

Possible attacks and impact on our system: The attacker can forge requests which contains a path containing the parent directory ../ string, thus try to perform a directory traversal attack. When he succeeds, he is able to read all the files on our system. He can thus search all files on the webserver which are readable for the www user. Such files may contain information, which is a severe privacy breach, or configuration information, which the attacker can search for weaknesses (e.g. try to crack weak passwords). Since our webserver does neither support any scripting nor accept form data sent to it, injection attacks and Cross site scripting (XSS) attacks are not a concern.

We rate the likelihood that someone attacks the system (at least tries it) using this method as high, because this attack is quite simple and the expected reward for the attacker is high.

The impact is classified medium or high, depending on what data (besides the actual public web site) the web server hosts. Even if the web server does not hold any sensitive data, a successful directory traversal attack is a privacy breach which should not happen under normal circumstances, thus we classify it at least medium.

| Character          | Shortest form | Non-shortest forms |

|--------------------|---------------|--------------------|

| U+002E "full stop" | 2E            | CO AE              |

| a.k.a. dot (.)     |               | EO 80 AE           |

|                    |               | FO 80 80 AE        |

| U+002F "solidus"   | 2F            | CO AF              |

| a.k.a. slash (/)   |               | E0 80 AF           |

|                    |               | FO 80 80 AF        |

**Table 2.1:** Representations (hexadecimal) for the control characters "Dot" and "Slash" in UTF-8, in the shortest form and non-shortest forms. These characters can be abused to perform directory traversal attacks.

#### 2.2.3 Change of Size of Requests

Description and examples: Unicode characters typically do not have a fixed length (except UTF-32, all encodings use variable length). Typically in legacy encodings (like ASCII or ISO-encodings), the character size was fixed to 1 byte. In UTF-8, the character width is variable, a single character can be up to 4 bytes long If a developer assumed one byte per characters and only checks input for the number of characters, but not for their size, the buffers he reserved in the memory will probably not be big enough to keep all input data. So, buffer overflow attacks become possible as the attacker just needs to send enough multi-byte characters which will be counted as 1 byte, but expanded to several bytes. The effects of buffer overflow attacks reach from Denial of Service (DoS) (cause a system / application to crash) up to code injection and privilege escalation attacks. A similar attack is possible when single characters are converted to several characters in another character set. As an example, one could imagine a UTF-8 to ASCII converter which automatically converts  $\beta$  (German Eszett) to ss, umlauts to ae, oe and ue or the fi-Ligature to fi.

**Possible countermeasures:** Programmers must reserve enough space for their string variables<sup>6</sup> when converting Unicode characters to other encodings, resp. stop the conversion when it contains too many characters.

As with the homograph attacks (2.2.1), an IPS could of course block such traffic. But it is also arguable if it makes sense, because the traffic might be legitimate.

Possible attacks and impact on our system: An attacker can send forged requests to our web server which contains multi-byte UTF-8 characters, to provoke a buffer overflow in the internal request handling procedures. He can then try to inject and execute his own executable code. Should he succeed, he will be in control of a process with the full access rights of the www user. This will gain him at least as much power as with the directory traversal attack described in Section 2.2.2.

We rate the likelihood of this attack medium, since provoking a privilege escalation (which implies a high reward for the attacker) using buffer overflows requires a deeper understanding of the web server's inner workings, thus it is not trivial. The attacker's risk that the attack gets noticed because the application crashes is much higher that the probability of a successful privilege escalation attack. The impact of a successful attack is similar, to a successful directory traversal attack: medium-high.

## 2.3 Choosing an Attack to be Implemented

Table 2.2 summarises the attacks described in the previous sections. The highest risk was assessed to the injection of control characters, in our case notably the directory traversal attack.

| Attack (section describing it)          | likelihood | impact   | risk   |

|-----------------------------------------|------------|----------|--------|

| Homograph attack (2.2.1)                | low        | low      | low    |

| Injection of control characters (2.2.2) | high       | med-high | high   |

| Change of size of requests (2.2.3)      | medium     | med-high | medium |

Table 2.2: Risk assessment of the evaluated attacks on Unicode resp. UTF-8.

As the web server to be protected only needs to understand ASCII, the most simple form of an IPS could simply reject all traffic containing non-ASCII characters. But in these days, where Unicode is omnipresent, this may not be wanted in general.

So we chose to implement a detection of UTF-8 non-shortest form attack. This is a more generic approach, as non-shortest form representations are almost never legitimate traffic.

#### 2.4 UTF-8 Non-Shortest Form Attack

This section explains how the UTF-8 non-shortest form attacks works, based on the UTF-8 encoding convention already explained in section 1.4.2. As one may observe from table 1.1, there is not only one possibility to encode short code points, but up to four. Code points shorter than 16 bits may be represented either in their shortest possible form, or using one of the longer representations possible, by padding the unused x's with 0. Table 2.3 illustrates this with the example of the character U+002E, "full stop".

<sup>&</sup>lt;sup>6</sup>A Table with maximum expansion factors can be found in [14].

26 2 Unicode Attacks

| Example: U+002E, "full stop" Code point number: $46_{decimal} = 2E_{hex} = 10 \ 1110_{binary}$ |                                         |                |

|------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|

| char. length                                                                                   | binary representation                   | hex represent. |

| 1 byte                                                                                         | <b>0</b> 010 1110                       | 2E             |

| 2 bytes                                                                                        | 1100 0000 1010 1110                     | C0 AE          |

| 3 bytes                                                                                        | 1110 0000 1000 0000 1010 1110           | E0 80 AE       |

| 4 bytes                                                                                        | 1111 0000 1000 0000 1000 0000 1010 1110 | F0 80 80 AE    |

**Table 2.3:** Example of a "full stop" character, encoded in the shortest form (first line) and the three non-shortest forms.

Only the shortest form representation is valid UTF-8, but there are implementation of UTF-8 interpreters which also (wrongly) interpret the non-shortest (a.k.a. overlong) form as UTF-8 characters, which potentially opens the door for attacks.

#### 2.5 Attacker model

Any security measure can only protect against certain kinds of attacks and attackers. In order to reasonably define and test the functionality of the IPS, we assume the following attacker model: The attacker is an active, external attacker, who tries to break into the system by exploiting vulnerabilities. He is able to fabricate packets and send them to our system. It is assumed he knows about the webserver's vulnerabilities to injection or directory traversal attacks, using UTF-8 encoded characters.

The IPS shall protect the webserver from these kind of attacks. It does not have to protect against any other kind of attackers or attacks. For instance, the IPS need not be able to detect or protect against man in the middle attacks, denial of service attacks or any kind of cryptographic attacks.

If an attacker manages to overload an IPS, there are two possibilities: The IPS can either switch to a state where it lets all packets pass unchecked, or switch to a state in which it blocks all traffic. Latter protects the system against attacks possible by overloading the IPS but, on the other hand, also makes DoS attacks more easy. We consider a DoS the less harmful impact on our system than a successful attack on the webserver, so we choose this option.

# Chapter 3

# Design and Implementation

This chapter describes the design and implementation of the EmbedNet IPS FB. We will first list all design goals (Section 3.1) and then explain the actual design and implementation steps of the different IPS components (Section 3.2ff.). Section 3.6explains the detection of the UTF-8 non-shortest form attack and in Section 3.7f. the vulnerable web server and other tools will be explained.

For the sake of linguistic simplicity, we will refer to the "EmbedNet IPS FB" simply as the "IPS".

## 3.1 Design Goals

#### 3.1.1 Attack to Detect

As chosen in 2.3, the IPS has to detect the 8-Bit UCS Transformation Format (UTF-8) non-shortest form attack. The attack is explained in Section 2.4.

#### 3.1.2 Extendability

In the context of future Internet technologies like LANA/EmbedNet, new threats are likely to appear each day in the wild. So an IPS must be easy to adapt and extend. It shall be simple to add more content analysis blocks to the IPS in order to extend it. Interfaces must be clearly defined and the implemented content analysis shall be easily reusable for new implementations.

#### 3.1.3 Hardware and Software Implementation

The IPS has to be implemented in hardware and in software, with identical behaviour. We expect the IPS to perform faster in hardware than in software. On the other hand, software resources can be reconfigured much faster and with higher flexibility than hardware. By providing both implementations, users may dynamically switch to the hardware version if the IPS is under heavy load. On the other hand, they can use the software version if only a few packets need to be inspected, and let the hardware do other tasks, e.g. de- or encryption.

#### 3.1.4 Single Packet Operation

The IPS operates on single packets. LANA/EmbedNet provides many new possibilities and no standard protocol for connection-oriented communication (like TCP in the current Internet) is defined yet. So it makes no sense yet to try to associate

various packets and inspect them together. The only thing which makes sense from today's point of view is to look at individual packets.

Each packet has to be received and checked for attacks. If an attack is found, the entire packet shall be dropped. If no attack is found, the entire packet has to be forwarded. Especially, the IPS shall not alter packets, e.g. by trying to remove or otherwise disable the attack from the packet.

#### 3.1.5 Configurable Header Length

It may be desirable to inspect only the payload of packets. The IPS shall provide the possibility to skip a certain amount of header bytes. This number has to be configurable at run-time. The correct usage of this variable is in the responsibility of the system implementer, especially this length shall not be set to a bigger value than the size of the packet which shall be inspected.

#### 3.1.6 Statistics and Configuration

The number of received, forwarded and dropped packets shall be counted. These counters shall be accessible by the software at run-time.

## 3.2 Overall System Design

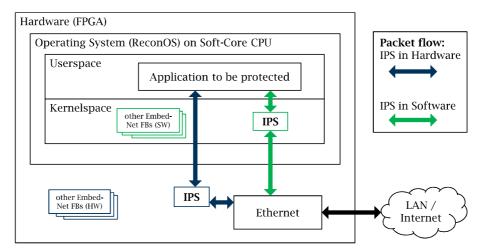

Figure 3.1: Overview of the entire system. The IPS can either be run in hardware (i.e. directly implemented on the FPGA), or in Software (i.e. running on CPU, on the FPGA). The application to be protected always runs in software.

Figure 3.1 shows an overview of the entire system. The IPS is one of several EmbedNet FBs. As explained in the Introduction (1.3.5), different FBs can be used at the same time and they can be dynamically loaded and unloaded according to the current needs of the system.

There are EmbedNet FBs which exist in hardware only (e.g. the Ethernet FB, as it must be connected to the physical Ethernet interface) or in software only, or in both. Programming a EmbedNet FB for hardware and software allows even more flexibility, as hardware-accelerated blocks can be used for load-intensive applications and software blocks for seldomly used applications. When we speak of a "Hardware EmbedNet FB" this means that the FB is implemented directly on the FPGA, using a Hardware Description Language (HDL). On the other hand, if we speak of

a "software FB" it means that this FB runs as executable program code within the CPU/RAM of the FPGA. The application to be protected always runs in software.

As already stated in the design goals (goal 3.1.3), the IPS has to be done in hardware and in software. The rest of this chapter is organised in the following way: Section 3.3 explains the design of the hardware block, Section 3.4 the software block and in Section 3.6 the design of the UTF-8 non-shortest form attack detection will be explained.

## 3.3 Hardware IPS Design and Implementation

In this section, we will explain the hardware design using a top-down approach. The Very High Speed Integrated Circuit Hardware Description Language (VHDL) will be used as HDL to implement the hardware. This language was chosen because the existing interfaces are also written in VHDL.

#### 3.3.1 IPS Hardware Thread

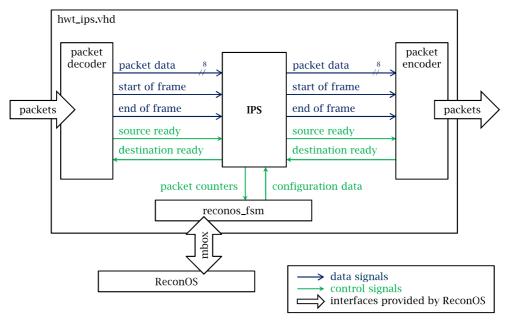

Figure 3.2: hwt\_ips.vhd – The ReconOS hardware thread entity provides communication between the software and the hardware. It contains the actual IPS entity.

The IPS hardware thread entity,  $hwt\_ips.vhd$  is the outermost entity of our design. Its layout is shown in Figure 3.2. It provides an abstraction layer to wrap the actual user logic of the IPS as a hardware thread. Communication with the software is handled by the OS synchronisation state machine  $reconos\_fsm$ , which, in turn, makes use of ReconOS message boxes and shared memory interfaces explained in Section 1.3.4. Furthermore, the entity also takes care of receiving and sending packet data from and to other hardware threads via the NoC, using the packet decoder and packet encoder entities explained in Section 1.3.6.

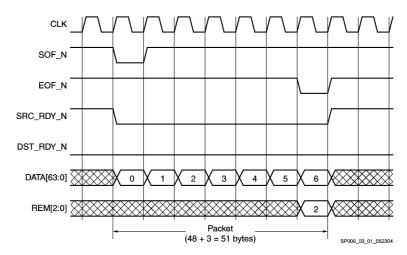

Within the entity, the Xilinx LocalLink Interface [18] is used to transfer packet data. The LocalLink Interface provides point-to-point communication within Xilinx FPGAs, Xilinx Intellectual Property (IP) cores also use this Interface. Besides transferring actual data signals in form of a data bus, this interface also defines flow control signals (source ready, destination ready) and framing control signals (start

of frame, end of frame). In our context, the start of frame and end of frame signals correspond to the start resp. the end of a network packet. We use a data bus width of 8 Bit, which means that 1 Byte can be transferred per clock cycle. The LocalLink interface provides even more signals, which we will not explain because they are not used in this thesis.

As most functionality in this entity is provided by ReconOS, there are only a few adaptions required within this entity. The obvious change is to include and instantiate one IPS entity and connect its input resp. output to the packet decoder and packet encoder. Furthermore, we need to add and connect 4 additional signals, 3 signals for packet counters and one for the header length (design goals 3.1.5 and 3.1.6). In order to send and receive these values to/from the software, also the reconos\_fsm state machine needs to be extended.

For better clearness, the *start of frame*, *end of frame* and actual *packet data* signals will be drawn combined, as a single *packets* signal, in the following figures.

#### 3.3.2 IPS Main Entity

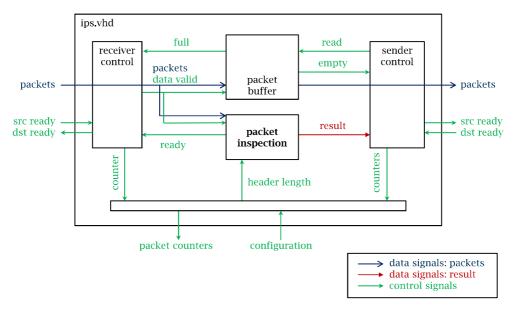

Figure 3.3: ips.vhd – The IPS Main entity

Figure 3.3 shows the main entity of the IPS. It handles the receiving of incoming packets, forwards input data to the packet inspection entity and buffers the packets while they are checked for attacks. When packet inspection is finished, it sends resp. drops the packets, depending of the result of the packet inspection. The following sections explain the mentioned parts.

#### 3.3.3 Receiver Control

As the name says, the receiver control part is responsible to receive packets. When all submodules of the IPS are ready to process packet data, it communicates this to the sender by setting the *source ready* bit to high.

It also provides an IPS-internal *data valid* signal, used by the other submodules. This signal set to high means that the data they receive are currently valid, i.e. all other submodules are ready and the IPS is currently receiving valid data. Furthermore, receiver control counts the packets received by the IPS (design goal 3.1.6).

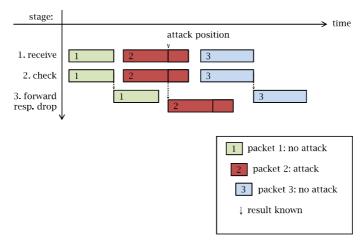

#### 3.3.4 Packet Buffer

As stated in design goal 3.1.4, the IPS has to be able to drop an entire packet if it contains an attack. Even if the hardware is able to process data at line rate, as they arrive, the IPS must not forward the packet unless it knows it does not contain an attack. The worst case scenario is that the attack is "hidden" in the byte that arrives last at the IPS, so we must reserve enough space to buffer at least one packet with the maximum possible size, Maximum Transmission Unit (MTU). We use the MTU of Ethernet as a reference, which is between 1500 and 1982 bytes [19]<sup>1</sup>, and chose to implement a 2000 byte deep First In, First Out (FIFO) buffer. The FIFO enables us to process packets exactly in the order they arrived, which is desirable. Packet can be queued (received) and dequeued (either sent or dropped) at the same time (except, of course, when the queue is full resp. empty), so we implicitly apply pipelining here. Figure 3.4 illustrates the timing behaviour of multiple packets processed by the IPS. Changing the size of of this buffer in the future is possible by adapting the value of one single constant in the entire VHDL code.

Figure 3.4: Packets can be received, processed and forwarded / dropped in parallel, by using the pipelining technique.

Besides the actual data bytes, also the *start of frame* and *end of frame signals* must be stored within this buffer, in order to clearly identify single packets. We define that all data in the buffer has to be valid packet data. This has the benefit that we don't need to explicitly buffer the *data valid* signal and there is no need to check data validity at the output of the buffer anymore. But it also implies that *receiver control* must only enqueue valid data bytes into the buffer.

Improvements made at ReconOS' FIFO Entity To implement the buffers in our design, the hardware fifo32.vhd entity of the ReconOS repository was used, and some adaptions were made: We implemented an overflow/underflow protection (which can be turned on or off using a generic variable). Additionally to the fill and free spaces signals, two new 1-bit signals full and empty were introduced which are set to '1' if the queue is full resp. empty. Further, the data width of the queue is no more fixed to 32 Bits, but can be set using a generic instruction.

The new file is included in the directory of the hardware IPS<sup>2</sup>. All changes are backwards compatible so it can be imported as the prototype FIFO queue to the ReconOS repository instead of the old version, if this is desired.

<sup>&</sup>lt;sup>1</sup>Not considering Gigabit Ethernet Jumbo frames.

$<sup>^2</sup>path\_to\_cdrom/IPS-HW/hwt\_ips\_v1\_00\_a/hdl/vhdl/fifo32.vhd$

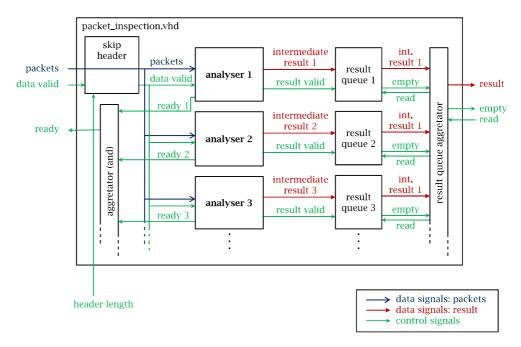

## 3.3.5 Packet Inspection Entity

Figure 3.5: packet\_inspection.vhd - The packet inspection entity distributes data to the different content analyses and aggretates their intermediate results.

The "heart" of the IPS are the content analysis blocks, which check the payload for actual attacks. This entity contains and manages the different content analyses. One instance of each content analysis is created by this entity, this means each of them gets its own hardware resources assigned at synthesis time, thus they can process the same packet in parallel. The packet inspection entity receives packets as input and broadcasts them to the different content analyses. All content analysis instances receive the packet data as input and return an intermediate result to the packet inspection entity, i.e. if they found "their" attack within the packet or not. Each of these intermediate results need to be queued in a separate queue, first because the content analyses do not necessarily finish all at the same time and secondly because we need to wait until the next higher level entity (i.e. sender control) is ready to process the result. From the outside, the output interface looks like one FIFO queue of results, so as soon as all intermediate results are present, they are aggregated and the next upper entity can dequeue the result from this virtual queue.

The packet inspection entity expects exactly one intermediate result for each packet. This means that the content analysis blocks must ensure that they reply each result during exactly one clock cycle, not more.

Note that the content analysers do not output any packet data, but only results. The IPS only needs to forward or drop packets (design goal 3.1.4), so no output except a result is needed from them.

Furthermore, this entity skips a user-defineable amount of (header-)bytes at the beginning of each packet (design goal 3.1.5). It manages this by overriding the internal data valid signal to be low on all bytes which don't have to be checked.

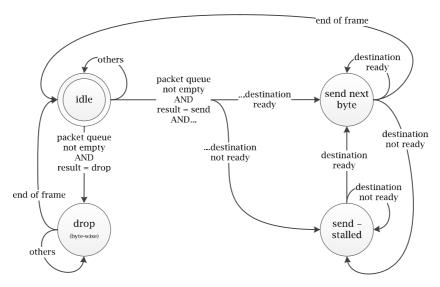

#### 3.3.6 Sender Control

Apart from the actual content analysis, this process is the most essential part of the IPS entity. The *sender control* process controls the data flow of the entire IPS. It retrieves the result from the *packet inspection* entity and sends or drops packets, according to the result. Furthermore, it counts the number of dropped resp. forwarded packets. The output of the IPS is connected to the packet encoder using the Xilinx LocalLink Interface, as explained in Section 3.3.1.

**Figure 3.6:** The *sender control* state machine controls the data flow of the IPS entity: It retreives the result from the *packet inspection* entity and sends or drops packets, according to the result.

Figure 3.6 shows the state diagram of the sender control Finite State Machine (FSM). Its initial state is the the *idle* state. In this state, the packet queue or the result queue are empty, so the sender currently cannot do anything and needs to wait for a new packet to arrive. When a packet arrives, the packet queue is being filled, but the result queue is still empty, because the result of the content analyses is not yet available. As soon as both queues contain data, sender control can start its work: Depending on the result, it must either forward (i.e. send) or drop the packet.

In the *drop* state, the current packet is known to contain an attack, hence it has to be dropped. "To drop" in this context means that *sender control* has to flush the current packet from the packet queue, s.t. the next packet in the queue can be accessed, but without actually sending the current packet to the output. It does this by dequeuing single bytes from the packet queue until the *end of frame* signal. The way to achieve this is by connecting the data bus directly to the output, and just by setting the *source ready* signal to low, *sender control* instructs the receiving entity that the data currently arriving is invalid and has to be ignored.

When the current packet is known not to contain an attack, it can be forwarded (sent). Sending is a bit more complex than dropping, because it may happen that the receiver is not ready while the IPS would like to send data. This is why there are two states for sending,  $send\_nextbyte$  and  $send\_stalled$ . As the names suggest, in the  $send\_nextbyte$  the next byte is read from the packet queue and forwarded to the receiver, as opposed to the  $send\_stalled$  state, where no byte must be read from the queue, since the receiver is not ready to process it.

**State machine implementation** The Sender Control FSM is a Mealy state machine. It is implemented using two concurrent processes, a synchronous, memorising (i.e. only executed on the rising clock edge) process and an asynchronous, memoryless (i.e. purely combinatorial) process. In the synchronous process, only the states and packet counters are updated. All other signals are updated in the combinatorial process.

#### 3.3.7 Interface to the Content Analysis Blocks

In the hardware, each content analysis block is implemented as a separate VHDL entity. The hardware interface for the content analysis blocks is defined as follows:

```

entity ca_prototype is

port (

rst

in

std_logic;

clk

in

std_logic;

std_logic;

rx sof

in

std_logic;

rx_eof

: in

std_logic_vector(7 downto 0);

rx_data

: in

rx_data_valid

: in

std_logic;

rx_ca_ready

: out std_logic;

tx_result

: out std_logic;

tx_result_valid : out std_logic

end ca_prototype;

```

Listing 3.1: Interface to the hardware content analysis blocks.

All rx\_ signals belong to the LocalLink interface, explained in Section 3.3.1. These are the input of the content analysis block, used to send the packet from the to the content analysis block. rx\_data\_valid and rx\_ca\_ready are the flow control signals source ready and destination ready, whereas rx\_sof and rx\_eof are the framing control signals start of frame and end of frame. Figure 3.7 illustrates how a packet sent via the LocalLink interface looks like.

**Figure 3.7:** Example of a packet sent via the LocalLink interface. The REM signal is not used by our system. (Figure taken from [18, p. 31])

The  $\mathtt{tx}$ \_ signals are the output of the content analyser, i.e. the result it has found. They are defined as

```

constant GOOD_FORWARD : std_logic := '1';

constant EVIL_DROP : std_logic := '0';

```

Listing 3.2: Definition of constants for "good" and "evil" in hardware.

and only considered valid when the tx\_result\_valid bit is also set to '1'. In the implementation one must consider that packet inspection entity expects exactly one intermediate result for each packet: The content analysis block must ensure it replies each result during exactly one clock cycle.

CA, in this context, stands for content analyser, RX and TX for receiver and sender.

The signals rst and clk are the reset and clock signal. The IPS is a synchronous design, i.e. there is one clock signal for the entire entity. The same applies for the reset signal: The rst signal is only set when the entire IPS is reset, not between single packets.

Content analysers shall not rely on a specific minimum length of packets (e.g. 64 bytes, as known from the Ethernet specification [19]), because the skipped header will not be "visible" for them. A minimum length of 1 byte per packet shall be assumed. Further, one needs to consider that the *start of frame* signal is not "visible" either when a header is skipped.

With this explanation of the content analysis blocks' interface, we conclude the hardware IPS. The following section will explain the design and implementation phase for the software IPS.

## 3.4 Software Design

The software version of the IPS is based on a Linux kernel networking module, for the LANA networking stack. Many parts of the the framework were given and simplified software design, as compared to the hardware design. Sending and receiving packets is done by the kernel, we can concentrate on the actual attack detection.

#### 3.4.1 Constructor Function

When the kernel loads a module (e.g. because the user instructed it to do so using the insmod command [20]), it calls the function init\_fb\_ips\_module. After loading, the module can be instantiated, using the fbctl tool. On instantiation, the constructor function fb\_ips\_ctor is called. We don't need any specific code to be run at loading time, only at instantiation, we need to reserve space for the counters and the header length variable. All other data or variables are only needed on a per packet basis, hence they don't need to be reserved at this time. To simplify debugging, some feedback output may be provided to the user when the module was successfully loaded and instantiated.

#### 3.4.2 IPS Main Function

The *netrx* function is called by the kernel each time a packet is received. This is where the IPS' work starts. Besides other information, the kernel provides the module the starting pointer to the memory area where the current packet is stored, and its size. All packet handling can then be performed by this function.

Processing packets basically requires the following sequential steps:

1. Increses received packets counter each time the function is called.

- 2. Determine which part to check for attacks (skip header, design goal 3.1.5).

- 3. Inspect the packet for attacks.

- 4. Instruct kernel either to drop or to forward the packet. Increase resp. counter.

As opposed to the hardware version where all content analyses can be run in parallel, the software may only run one packet analysis at once<sup>3</sup>. It makes thus sense to first run the analyses which do not require much computation time and skip the remaining analyses, should an attack be found. As only one packet is processed at once, there is no need to queue the results.

After the result is known, the main function either instructs the kernel to drop the packet or returns a success value, which instructs it to forward the packet.

#### 3.4.3 Configure Header and get Statistics

In order to configure the IPS and get information from it, we use the *procfs* interface. This interface creates a node in the file system which, when read by the user, prints a content specified in the kernel module and, when written to it, stores the written content inside the kernel module's memory. We use the *procfs* interface to display packet counters (*fb\_ips\_proc\_show* function) or to receive a new value for the header length (*fb\_ips\_proc\_write* function).

#### 3.4.4 Interface to the Content Analysis Blocks

In the software, each content analysis is implemented as a C function, usually stored in a separate file.

The called function will receive two arguments:

**Listing 3.3:** Interface to the software content analysis blocks.

The pointer buffer points directly to the start of the payload, stripping the header has already been done by the calling function. The number of bytes which have to be checked are stored in the integer packet\_length. As with the pointer, also this is the length without the header.

The content analysis returns a value of type *int*, which is defined as 1 when the packet is "good" and 0 for "evil":

```

const int GOODFORWARD = 1;

const int EVIL_DROP = 0;

```

Listing 3.4: Definition of constants for "good" and "evil" in software.

When implementing new content analyses, do not rely on a specific minimum length of packets (e.g. 64 byte), because the skipped header will not be "visible" for the content analysis block. Assume a minimum length of 1 byte per packet.

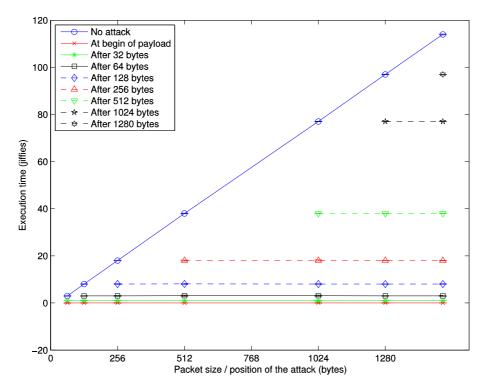

#### 3.5 Software Measurements

To perform the measurements of the software, some code has to be added which stores the current time stamps on different execution stages of the IPS and computes the elapsed time. In order to minimise the impact of this code on the overall performance, all variables are instantiated before the actual computation phase and

<sup>&</sup>lt;sup>3</sup>The system we use runs on a single core processor

all output is made after the computation phase. The output is made s.t. the result data can be imported and processed as a Comma-Separated Values (CSV) file. This was done by printing all results which belong together, on one line, separated by semicolons<sup>4</sup>. To perform the measurement, the output of the serial console must be recorded (e.g. using minicom's log feature) and then evaluated.

In order to differentiate between the lines containing the CSV data and any other output which may be present on the serial console's recording (from the setup phase, other measurement output, etc.), we added keyword [fb\_ips\_meas] to each line containing measurement data, so they can be filtered for this keyword.

Further, there shall not be any unneccessary commands during the measurement phase. Especially there shall be no printf commands, since they need a lot of time (data must be sent over a slow serial terminal) and would distort the measurement.

This concludes the explanations of the software IPS. The following section will explain how to detect the UTF-8 non-shortest form attack.

#### 3.6 UTF-8 Non-Shortest Form Detection

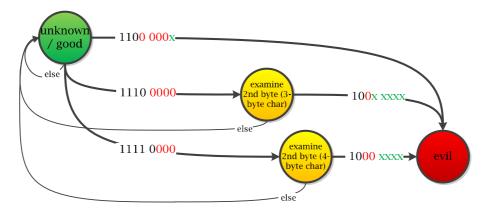

In this section, we explain the detection of the UTF-8 non-shortest form attack. Table 3.1 shows how UTF-8 characters are represented as binary data. For a general explanation of how UTF-8 works, please refer to Section 1.4.2 of this document. As explained there, UTF-8 stores characters using 1, 2, 3 or 4 bytes. Part a) of the table shows these different possibilities: Line 1 shows a 1-byte character, line 2 a 2-byte character, etc. The bytes which are available for encoding bits of the codepoint number are marked with an x in the table and the number of possible bits is marked in the rightmost column.

| a)      |                                                                   |         |

|---------|-------------------------------------------------------------------|---------|

| 1 byte  | 0xxx xxxx                                                         | 7 bits  |

| 2 bytes | 110x xxxx 10xx xxxx  Tth bit                                      | 11 bits |

| 3 bytes | 1110 xxxx 10xx xxxx 10xx xxxx  11th bit                           | 16 bits |

| 4 bytes | 1111 0xxx 10xx xxxx 10xx xxxx 10xx xxxx    16th bit               | 21 bits |

| b)      |                                                                   |         |

| 1 byte  | 0xxx xxxx                                                         | 7 bits  |

| 2 bytes | 110 <u>0 000</u> x 10xx xxxx<br>— 7th bit                         | 11 bits |

| 3 bytes | 1110 <u>0000</u> 10 <u>0</u> x xxxx 10xx xxxx<br>11th bit         | 16 bits |

| 4 bytes | 1111 0 <u>000</u> 10 <u>00</u> xxxx 10xx xxxx 10xx xxxx  16th bit | 21 bits |

**Table 3.1:** Binary representation of Unicode characters in UTF-8. Underlined in table b) are the bits which are 0 when a non-shortest form attack is present.